本文主要是介绍关于CAN逻辑电平显性优先的硬件原理,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

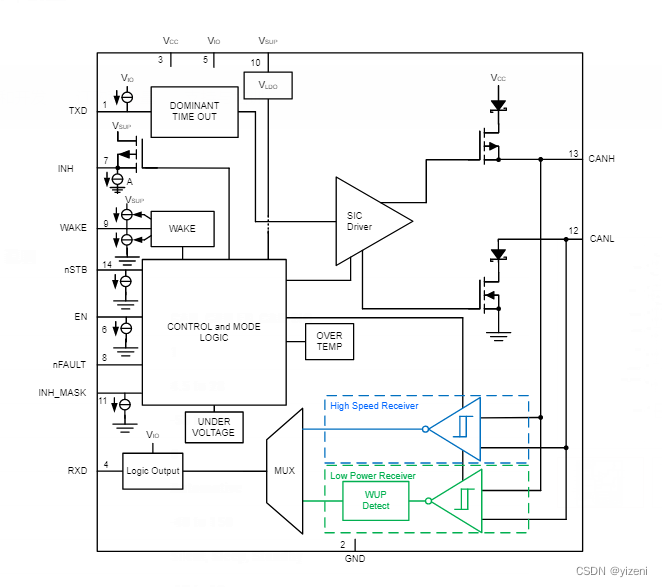

最近在学习CAN报文的时候,在涉及仲裁段电平显性优先时,资料大多模糊不清让我很难受,于是直接去TI官网随便找了一个CAN芯片电路图,从硬件看逻辑电平的判断,一下就明白了

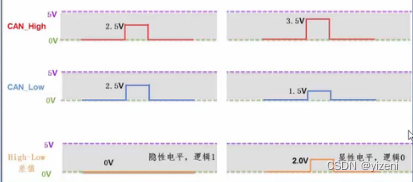

当CAN_H为3.5V CAN_L为1.5V CAN逻辑电平为0,即显性电平

当CAN_H和CAN_L都为2.5V CAN逻辑电平为隐形电平,即为1;

参考CAN芯片电路,CAN—H 上拉,显性的与隐性信号同时出现时,输出显性电平(0)的节点会从VCC源源不断地输出3.5V电压来拉高总线上输出隐性电平(1)的2.5V至3.5V;CAN_L下拉 ,输出显性电平的(0)节点也会源源不断的将总线从2.5V拉低至1.5V,此时CAN_H为3.5V,CAN_L为1.5V,逻辑电平为显性电平(0),从而从硬件上实现了线与

这篇关于关于CAN逻辑电平显性优先的硬件原理的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!