本文主要是介绍CoaXPress 2.0 FPGA 4 Channel Host and Device FMC Card User Manual,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Hello-FPGA CoaXPress 2.0 FMC Card User Manual 4

1 CoaXPress 简介 4

2 CoaXPress 4R FMC 5

2.1 硬件特性 5

2.2 框图说明 7

2.3 电源监测 8

3 CoaXPress 4T FMC 9

3.1 硬件特性 9

3.2 框图说明 10

4 FMC PIN定义 11

Annex A:参考资料 22

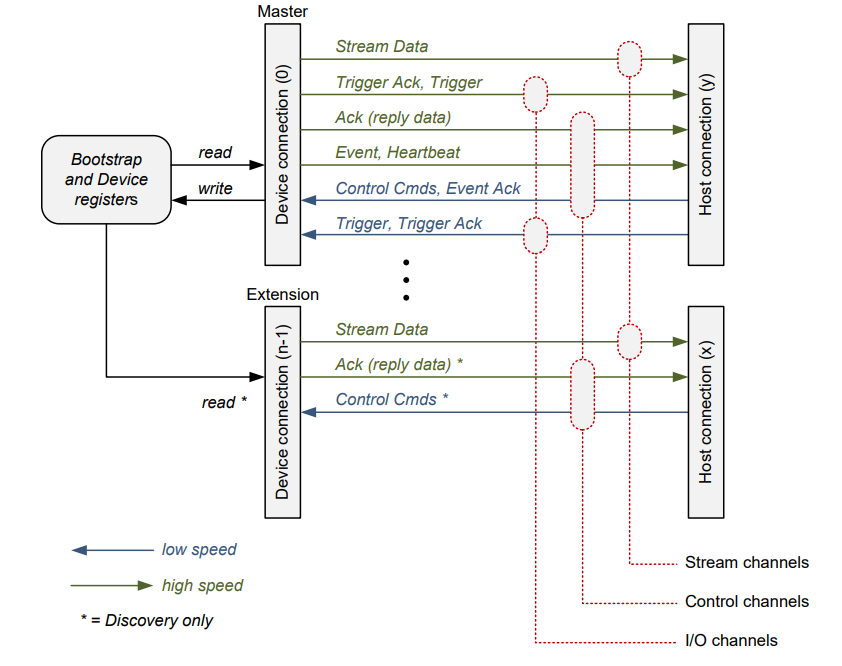

图 1‑1 CXP链接结构 5

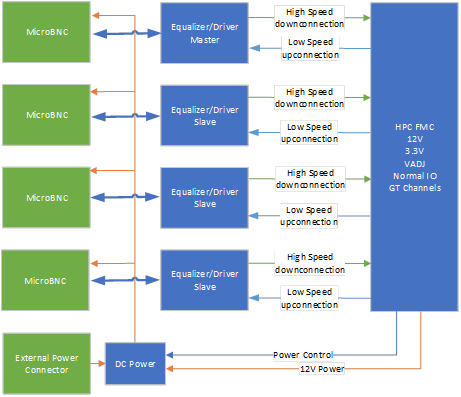

图 2‑1 Hello-FPGA 4R FMC Card Simple Diagram 6

图 2‑2 Hello-FPGA 4R FMC Card 7

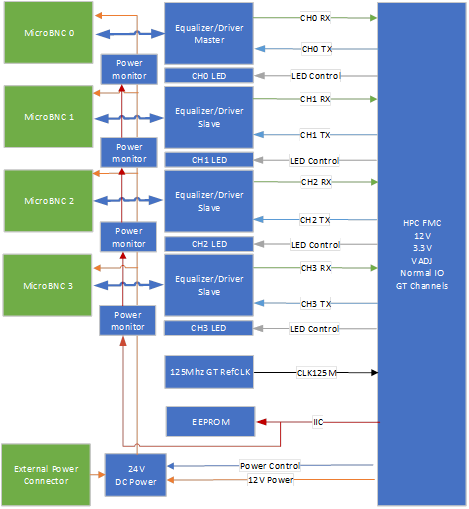

图 2‑3 CoaXPress 4R FMC detailed diagram 8

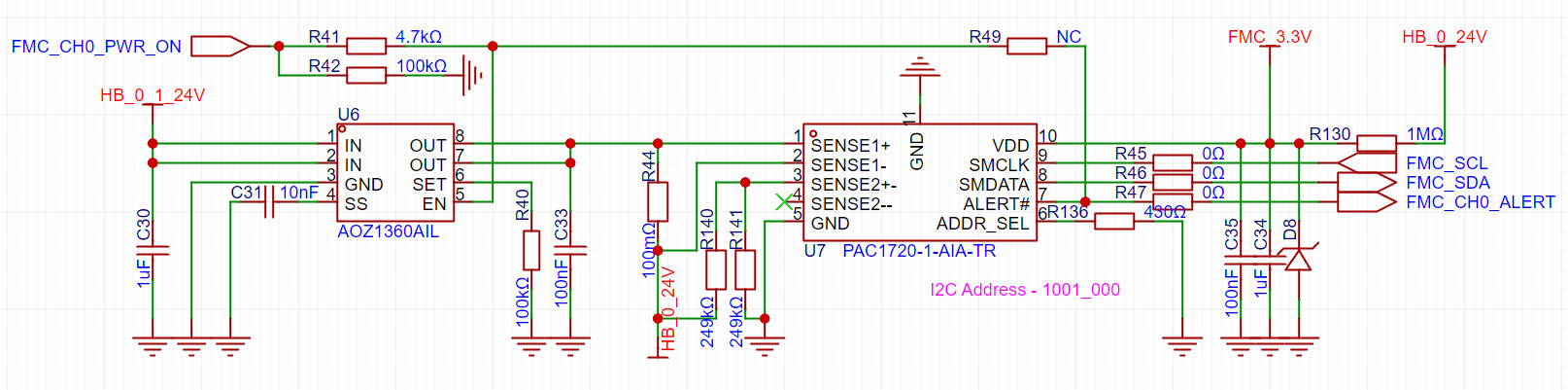

图 2‑4 channel 0电源监测电路 9

图 3‑1 Hello-FPGA 4T FMC Card Simple Diagram 10

图 3‑2 Hello-FPGA 4T FMC Card 10

图 3‑3 CoaXPress 4R FMC detailed diagram 11

图 4‑1 HPC FMC pins 12

Hello-FPGA CoaXPress 2.0 FMC Card User Manual

CoaXPress 简介

CoaXPress (简称CXP)是指一种采用同轴线缆进行互联的相机数据传输标准,主要用于替代之前的Camera Link协议,常见于科学相机、工业相机、医学图像、航空防务等场景。Camera Link 由于线缆的形式、传输速度等原因,已经不再适用于不断增长的数据带宽需求。

CXP是一个非对称的高速点对点串行传输协议,主要用于传输视频和静态图像,线缆多使用单条或多条同轴电缆。目前2.0标准的最高速度为单条lane 12.5Gbps,单条lane 上除了传输图像数据之外,还可以传输低速控制信号(41.6Mbps)、也可以利用该线缆对相机进行供电,即“Power-over-Coax”,单条线缆最长可达100m。

- 单条同轴线缆最高12.5Gbps的线速率,可以使用单条或者多条线缆,比如4条线缆可以最高提供50Gbps的数据速率

- 较长的线缆长度,比如3.125 Gbps 速率下线长可以到100m,12.5Gbps速率下可以到35m

- 数据传输具备实时和低延迟的特性,且延迟是固定的

- 精准实时的触发特性,支持通过同轴线缆发送触发,无需额外的通讯线缆

- 可以获得灵活可靠的性能,通过使用标准的同轴线缆,比如RG59 和 RG6规格,推荐使用RG6

- 易于集成的特性,图像、控制通讯、电源可以使用同一条线缆,且线缆价格便宜

CXP是一种点对点可扩展接口, 设备和HOST之间的物理介质为75Ω 同轴电缆。每一个CXP接口都包含1个MASTER连接和若干可选的扩展SLAVE连接,每一个连接都需要1条同轴线缆,通常设备会对这些连接进行编号,MASTER固定为0,SLAVE扩展接口依次递增。

每一个connection都包含如下功能

- 高速串行数据(通常为Device到 Host downconnection), 最高 12.5 Gbps.

- 低速串行数据(通常为Host 到Device upconnection), 最高 41.6˙ Mbps .

- 供电功能Power (Host 到 Device), 最高13W.

CoaXPress 4R FMC

为了评估IP功能,快速实现应用,Hello-FPGA开发了4通道CoaXPress 收发模块,其中收模块定义如下,配合Hello-FPGA的CoaXPress Host IP可以实现自定义相机Grabber采集、处理应用:

硬件特性

▪ 最高支持4 CoaXPress links

▪ 支持POE Power over CoaXPress功能,用户可选外部供电或者使用板上12V电源

▪ 4 x Micro BNC 连接器

▪ HPC连接器 – High Pin count connector,VITA 57.1 compliant

▪ 尺寸63mm x 84mm, 单槽 FMC

▪ 最高支持速率 12.5Gpbs,支持CoaXPress 2.0协议标称所有速率,使用高速PCB板材

▪ - 40°C to 85°C 工作温度 (industrial grade)

▪ 板载2Kb EEPROM,可以用于写入用户特定信息

▪ 板载4路power 功率监测电路,用户可以实时监测供电情况

图 2‑1 Hello-FPGA 4R FMC Card Simple Diagram

框图说明

图 2‑3 CoaXPress 4R FMC detailed diagram

- HPC FMC连接器,使用FMC高密度连接器,符合VITA 57.1标准;

- Equalizer/Driver均衡器与驱动器,接收来自相机的高速downlink信号,发送来组FMC IO的低速控制信号;

- LED,每个通道配置1个双色LED,可以通过FMC IO实现R,G颜色任意组合;

- EEPROM,使用IIC接口的MT24C02 EEPROM,256Bytes容量,可以用于存储用户数据;

- 24V DC Power, 24V DC电源电路,可以接受来自FMC的12V或者来自外部电源的12V供电电源,为power on cable功能提供DC电源,理论CXP每通道提供最大13W输出功率;

- Power monitor,每路CoaXPress提供1路电流、电压监测电路,当电流超过门限后,会通过alert 端口向外发出警告;

- MicroBNC, 根据CoaXPress标准,子板使用MircroBNC连接器连接Device设备;

电源监测

使用4路PAC1720进行电源监测,4路IIC设备地址分别为0x48.0x49.0x5a,0x5b,分别对应channel 0-3。

PAC1720功能说明:

- PoE电流监测,通过SENSE1+和SENSE1-引脚两端的外部电阻(图中R44)上的电压间接得到(需结合FSR的设定);

- PoE电压监测,通过SENSE2+引脚可以获取1/2的PoE电压,从而间接获取PoE电压;

- 过流提醒,用户可以编程限定PoE电压流过的电流,在过流时将ALERT信号拉低,从而触发电源控制系统;

- 通讯地址选择,用户可以通过改变ADDR_SEL引脚对地的电阻值来改变I2C的地址;

备注:具体功能参数设定,请参考PAC1720 datasheet。我们的范例程序会包含电源监测部分示例源代码供测试、参考。

CoaXPress 4T FMC

为了评估IP功能,快速实现应用,Hello-FPGA开发了4通道CoaXPress 收发模块,其中发模块定义如下,配合Hello-FPGA CoaXPress Device IP,可以实现相机、图像模拟源的开发应用:

硬件特性

▪ 最高支持4 CoaXPress links

▪ 4 x Micro BNC 连接器

▪ HPC连接器 – High Pin count connector,VITA 57.1 compliant

▪ 尺寸63mm x 84mm, 单槽 FMC

▪ 最高支持速率 12.5Gpbs,支持CoaXPress 2.0协议标称所有速率,使用高速PCB板材

▪ - 40°C to 85°C 工作温度 (industrial grade)

▪ 板载2Kb EEPROM,可以用于写入用户特定信息

图 3‑1 Hello-FPGA 4T FMC Card Simple Diagram

框图说明

图 3‑3 CoaXPress 4R FMC detailed diagram

- HPC FMC连接器,使用FMC高密度连接器,符合VITA 57.1标准;

- Equalizer/Driver均衡器与驱动器,发送来自FPGA高速收发器的高速downlink信号,接受来组Grabber的低速控制信号;

- LED,每个通道配置1个双色LED,可以通过FMC IO实现R,G颜色任意组合;

- EEPROM,使用IIC接口的MT24C02 EEPROM,256Bytes容量,可以用于存储用户数据;

- MicroBNC, 根据CoaXPress标准,子板使用MircroBNC连接器连接Grabber采集设备;

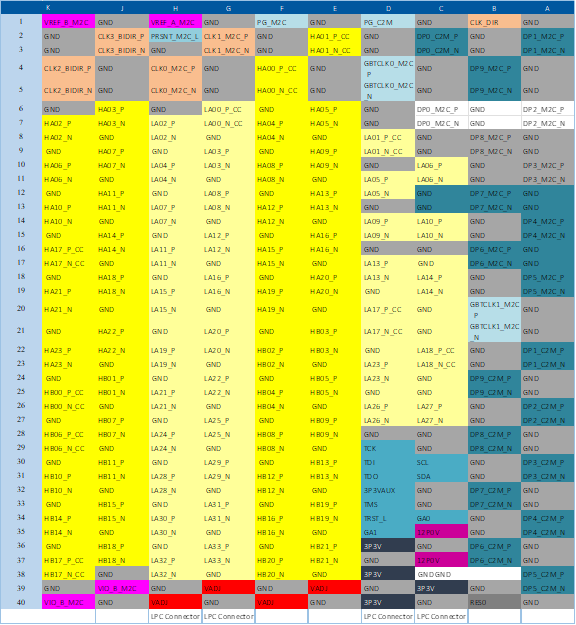

FMC PIN定义

这里的pin定义适用于Hello-FPGA CoaXPress 4R/4T FMC硬件。

表 4‑1 CoaXPress 4 Channel FMC Pin Map

| # | FMC PIN name | 信号名称 | 描述 |

| A1 | GND | - | Signal GND |

| A2 | DP1_M2C_P | CH1_RXp | CoaXPress channel 1 fast speed link Receive (Positive) Grabber Only |

| A3 | DP1_M2C_N | CH1_RXn | CoaXPress channel 1 fast speed link Receive (Negative) |

| A4 | GND | - | Signal GND |

| A5 | GND | - | Signal GND |

| A6 | DP2_M2C_P | CH2_RXp | CoaXPress channel 2 fast speed link Receive (Positive) Grabber Only |

| A7 | DP2_M2C_N | CH2_RXn | CoaXPress channel 2 fast speed link Receive (Negative) |

| A8 | GND | - | Signal GND |

| A9 | GND | - | Signal GND |

| A10 | DP3_M2C_P | CH3_RXp | CoaXPress channel 3 fast speed link Receive (Positive) Grabber Only |

| A11 | DP3_M2C_N | CH3_RXn | CoaXPress channel 3 fast speed link Receive (Negative) |

| A12 | GND | - | Signal GND |

| A13 | GND | - | Signal GND |

| A14 | DP4_M2C_P | N/C | NC |

| A15 | DP4_M2C_N | N/C | NC |

| A16 | GND | - | Signal GND |

| A17 | GND | - | Signal GND |

| A18 | DP5_M2C_P | N/C | NC |

| A19 | DP5_M2C_N | N/C | NC |

| A20 | GND | - | Signal GND |

| A21 | GND | - | Signal GND |

| A22 | DP1_C2M_P | CH1_TXp | CoaXPress channel 1 fast speed link Transmit (Positive) Device Only |

| A23 | DP1_C2M_N | CH1_TXn | CoaXPress channel 1 fast speed link Transmit (Negative) |

| A24 | GND | - | Signal GND |

| A25 | GND | - | Signal GND |

| A26 | DP2_C2M_P | CH2_TXp | CoaXPress channel 2 fast speed link Transmit (Positive) Device Only |

| A27 | DP2_C2M_N | CH2_TXn | CoaXPress channel 2 fast speed link Transmit (Negative) |

| A28 | GND | - | Signal GND |

| A29 | GND | - | Signal GND |

| A30 | DP3_C2M_P | CH3_TXp | CoaXPress channel 3 fast speed link Transmit (Positive) Device Only |

| A31 | DP3_C2M_N | CH3_TXn | CoaXPress channel 3 fast speed link Transmit (Negative) |

| A32 | GND | - | Signal GND |

| A33 | GND | - | Signal GND |

| A34 | DP4_C2M_P | N/C | NC |

| A35 | DP4_C2M_N | N/C | NC |

| A36 | GND | - | Signal GND |

| A37 | GND | - | Signal GND |

| A38 | DP5_C2M_P | N/C | NC |

| A39 | DP5_C2M_N | N/C | NC |

| A40 | GND | - | Signal GND |

| B1 | CLK_DIR | N/C | NC |

| B2 | GND | - | Signal GND |

| B3 | GND | - | Signal GND |

| B4 | DP9_M2C_P | N/C | NC |

| B5 | DP9_M2C_N | N/C | NC |

| B6 | GND | - | Signal GND |

| B7 | GND | - | Signal GND |

| B8 | DP8_M2C_P | N/C | NC |

| B9 | DP8_M2C_N | N/C | NC |

| B10 | GND | - | Signal GND |

| B11 | GND | - | Signal GND |

| B12 | DP7_M2C_P | N/C | NC |

| B13 | DP7_M2C_N | N/C | NC |

| B14 | GND | - | Signal GND |

| B15 | GND | - | Signal GND |

| B16 | DP6_M2C_P | N/C | NC |

| B17 | DP6_M2C_N | N/C | NC |

| B18 | GND | - | Signal GND |

| B19 | GND | - | Signal GND |

| B20 | GBTCLK1_M2C_P | GND | Pulled to GND |

| B21 | GBTCLK1_M2C_N | VADJ | Adjustable voltage for I/O signals to FPGA |

| B22 | GND | - | Signal GND |

| B23 | GND | - | Signal GND |

| B24 | DP9_C2M_P | N/C | NC |

| B25 | DP9_C2M_N | N/C | NC |

| B26 | GND | - | Signal GND |

| B27 | GND | - | Signal GND |

| B28 | DP8_C2M_P | N/C | NC |

| B29 | DP8_C2M_N | N/C | NC |

| B30 | GND | - | Signal GND |

| B31 | GND | - | Signal GND |

| B32 | DP7_C2M_P | N/C | NC |

| B33 | DP7_C2M_N | N/C | NC |

| B34 | GND | - | Signal GND |

| B35 | GND | - | Signal GND |

| B36 | DP6_C2M_P | N/C | NC |

| B37 | DP6_C2M_N | N/C | NC |

| B38 | GND | - | Signal GND |

| B39 | GND | - | Signal GND |

| B40 | RES0 | N/C | NC |

| C1 | GND | - | Signal GND |

| C2 | DP0_C2M_P | CH0_TXp | CoaXPress channel 0 fast speed link Transmit (Positive) Device Only |

| C3 | DP0_C2M_N | CH0_TXn | CoaXPress channel 0 fast speed link Transmit (Negative) |

| C4 | GND | - | Signal GND |

| C5 | GND | - | Signal GND |

| C6 | DP0_M2C_P | CH0_RXp | CoaXPress channel 0 fast speed link Receive (Positive) Grabber Only |

| C7 | DP0_M2C_N | CH0_RXn | CoaXPress channel 0 fast speed link Receive (Negative) |

| C8 | GND | - | Signal GND |

| C9 | GND | - | Signal GND |

| C10 | LA06_P | N/C | NC |

| C11 | LA06_N | N/C | NC |

| C12 | GND | - | Signal GND |

| C13 | GND | - | Signal GND |

| C14 | LA10_P | N/C | NC |

| C15 | LA10_N | N/C | NC |

| C16 | GND | - | Signal GND |

| C17 | GND | - | Signal GND |

| C18 | LA14_P | CH3_LED0 | Channel 3 Green indicator LED (Active high) |

| C19 | LA14_N | CH3_LED1 | Channel 3 Red indicator LED (Active high) |

| C20 | GND | - | Signal GND |

| C21 | GND | - | Signal GND |

| C22 | LA18_P_CC | CH0_ALERT | Channel 0 PoCXP alert indicator(Active high) |

| C23 | LA18_N_CC | N/C | NC |

| C24 | GND | - | Signal GND |

| C25 | GND | - | Signal GND |

| C26 | LA27_P | N/C | NC |

| C27 | LA27_N | N/C | NC |

| C28 | GND | - | Signal GND |

| C29 | GND | - | Signal GND |

| C30 | SCL | SCL | IIC clock Connected to EEPROM and PoCXP power monitor ADCs |

| C31 | SDA | SDA | IIC data Connected to EEPROM and PoCXP power monitor ADCs |

| C32 | GND | - | Signal GND |

| C33 | GND | - | Signal GND |

| C34 | GA0 | N/C | NC |

| C35 | 12P0V | 12V | 12V power supply |

| C36 | GND | - | Signal GND |

| C37 | 12P0V | 12V | 12V power supply |

| C38 | GND | - | Signal GND |

| C39 | 3P3V | 3.3V | 3.3V Power supply |

| C40 | GND | - | Signal GND |

| D1 | PG_C2M | N/C | NC |

| D2 | GND | - | Signal GND |

| D3 | GND | - | Signal GND |

| D4 | GBTCLK0_M2C_P | CLK_125M_P | 125MHz Reference clock (Positive) ±25ppm / -40℃ to +85℃ |

| D5 | GBTCLK0_M2C_N | CLK_125M_N | 125MHz Reference clock (Negative) |

| D6 | GND | - | Signal GND |

| D7 | GND | - | Signal GND |

| D8 | LA01_P_CC | CH2_LF | CoaXPress channel 2 low speed link TX/RX (Rx for Device, TX for Grabber) |

| D9 | LA01_N_CC | CH1_LF | CoaXPress channel 1 low speed link TX/RX(Rx for Device, TX for Grabber) |

| D10 | GND | - | Signal GND |

| D11 | LA05_P | N/C | NC |

| D12 | LA05_N | N/C | NC |

| D13 | GND | - | Signal GND |

| D14 | LA09_P | N/C | NC |

| D15 | LA09_N | N/C | NC |

| D16 | GND | - | Signal GND |

| D17 | LA13_P | CH2_LED0 | Channel 2 Green indicator LED (Active high) |

| D18 | LA13_N | CH2_LED1 | Channel 2 Red indicator LED (Active high) |

| D19 | GND | - | Signal GND |

| D20 | LA17_P_CC | N/C | NC |

| D21 | LA17_N_CC | N/C | NC |

| D22 | GND | - | Signal GND |

| D23 | LA23_P | N/C | NC |

| D24 | LA23_N | N/C | NC |

| D25 | GND | - | Signal GND |

| D26 | LA26_P | N/C | NC |

| D27 | LA26_N | N/C | NC |

| D28 | GND | - | Signal GND |

| D29 | TCK | N/C | NC |

| D30 | TDI | TD | JTAG Loopback |

| D31 | TDO | TD | JTAG Loopback |

| D32 | 3P3VAUX | 3.3V_AUX | Auxiliary 3.3V |

| D33 | TMS | N/C | NC |

| D34 | TRST_L | N/C | NC |

| D35 | GA1 | N/C | NC |

| D36 | 3P3V | 3.3V | 3.3V Power supply |

| D37 | GND | - | Signal GND |

| D38 | 3P3V | 3.3V | 3.3V Power supply |

| D39 | GND | - | Signal GND |

| D40 | 3P3V | 3.3V | 3.3V Power supply |

| E1 | GND | - | Signal GND |

| E2 | HA01_P_CC | N/C | NC |

| E3 | HA01_N_CC | N/C | NC |

| E4 | GND | - | Signal GND |

| E5 | GND | - | Signal GND |

| E6 | HA05_P | N/C | NC |

| E7 | HA05_N | N/C | NC |

| E8 | GND | - | Signal GND |

| E9 | HA09_P | N/C | NC |

| E10 | HA09_N | N/C | NC |

| E11 | GND | - | Signal GND |

| E12 | HA13_P | N/C | NC |

| E13 | HA13_N | N/C | NC |

| E14 | GND | - | Signal GND |

| E15 | HA16_P | N/C | NC |

| E16 | HA16_N | N/C | NC |

| E17 | GND | - | Signal GND |

| E18 | HA20_P | N/C | NC |

| E19 | HA20_N | N/C | NC |

| E20 | GND | - | Signal GND |

| E21 | HB03_P | N/C | NC |

| E22 | HB03_N | N/C | NC |

| E23 | GND | - | Signal GND |

| E24 | HB05_P | N/C | NC |

| E25 | HB05_N | N/C | NC |

| E26 | GND | - | Signal GND |

| E27 | HB09_P | N/C | NC |

| E28 | HB09_N | N/C | NC |

| E29 | GND | - | Signal GND |

| E30 | HB13_P | N/C | NC |

| E31 | HB13_N | N/C | NC |

| E32 | GND | - | Signal GND |

| E33 | HB19_P | N/C | NC |

| E34 | HB19_N | N/C | NC |

| E35 | GND | - | Signal GND |

| E36 | HB21_P | N/C | NC |

| E37 | HB21_N | N/C | NC |

| E38 | GND | - | Signal GND |

| E39 | VADJ | VADJ | Adjustable voltage for I/O signals to FPGA |

| E40 | GND | - | Signal GND |

| F1 | PG_M2C | 3.3V | Pulled to 3.3V |

| F2 | GND | - | Signal GND |

| F3 | GND | - | Signal GND |

| F4 | HA00_P_CC | N/C | NC |

| F5 | HA00_N_CC | N/C | NC |

| F6 | GND | - | Signal GND |

| F7 | HA04_P | N/C | NC |

| F8 | HA04_N | N/C | NC |

| F9 | GND | - | Signal GND |

| F10 | HA08_P | N/C | NC |

| F11 | HA08_N | N/C | NC |

| F12 | GND | - | Signal GND |

| F13 | HA12_P | N/C | NC |

| F14 | HA12_N | N/C | NC |

| F15 | GND | - | Signal GND |

| F16 | HA15_P | N/C | NC |

| F17 | HA15_N | N/C | NC |

| F18 | GND | - | Signal GND |

| F19 | HA19_P | N/C | NC |

| F20 | HA19_N | N/C | NC |

| F21 | GND | - | Signal GND |

| F22 | HB02_P | N/C | NC |

| F23 | HB02_N | N/C | NC |

| F24 | GND | - | Signal GND |

| F25 | HB04_P | N/C | NC |

| F26 | HB04_N | N/C | NC |

| F27 | GND | - | Signal GND |

| F28 | HB08_P | N/C | NC |

| F29 | HB08_N | N/C | NC |

| F30 | GND | - | Signal GND |

| F31 | HB12_P | N/C | NC |

| F32 | HB12_N | N/C | NC |

| F33 | GND | - | Signal GND |

| F34 | HB16_P | N/C | NC |

| F35 | HB16_N | N/C | NC |

| F36 | GND | - | Signal GND |

| F37 | HB20_P | N/C | NC |

| F38 | HB20_N | N/C | NC |

| F39 | GND | - | Signal GND |

| F40 | VADJ | VADJ | Adjustable voltage for I/O signals to FPGA |

| G1 | GND | - | Signal GND |

| G2 | CLK1_M2C_P | N/C | NC |

| G3 | CLK1_M2C_N | N/C | NC |

| G4 | GND | - | Signal GND |

| G5 | GND | - | Signal GND |

| G6 | LA00_P_CC | CH0_LF | CoaXPress channel 0 low speed link TX/RX |

| G7 | LA00_N_CC | N/C | NC |

| G8 | GND | - | Signal GND |

| G9 | LA03_P | N/C | NC |

| G10 | LA03_N | N/C | NC |

| G11 | GND | - | Signal GND |

| G12 | LA08_P | N/C | NC |

| G13 | LA08_N | N/C | NC |

| G14 | GND | - | Signal GND |

| G15 | LA12_P | CH1_LED0 | Channel 1 Green indicator LED (Active high) |

| G16 | LA12_N | CH1_LED1 | Channel 1 Red indicator LED (Active high) |

| G17 | GND | - | Signal GND |

| G18 | LA16_P | N/C | NC |

| G19 | LA16_N | N/C | NC |

| G20 | GND | - | Signal GND |

| G21 | LA20_P | N/C | NC |

| G22 | LA20_N | CH3_ALERT | Channel 3 PoCXP alert indicator (Active high) |

| G23 | GND | - | Signal GND |

| G24 | LA22_P | CH3_ON | Channel 3 PoCXP enable (Active high) |

| G25 | LA22_N | CH2_ON | Channel 2 PoCXP enable (Active high) |

| G26 | GND | - | Signal GND |

| G27 | LA25_P | N/C | NC |

| G28 | LA25_N | N/C | NC |

| G29 | GND | - | Signal GND |

| G30 | LA29_P | N/C | NC |

| G31 | LA29_N | N/C | NC |

| G32 | GND | - | Signal GND |

| G33 | LA31_P | N/C | NC |

| G34 | LA31_N | N/C | NC |

| G35 | GND | - | Signal GND |

| G36 | LA33_P | N/C | NC |

| G37 | LA33_N | N/C | NC |

| G38 | GND | - | Signal GND |

| G39 | VADJ | VADJ | Adjustable voltage for I/O signals to FPGA |

| G40 | GND | - | Signal GND |

| H1 | VREF_A_M2C | N/C | NC |

| H2 | PRSNT_M2C_L | GND | Pulled Low |

| H3 | GND | - | Signal GND |

| H4 | CLK0_M2C_P | GND | Pulled to GND |

| H5 | CLK0_M2C_N | VADJ | Adjustable voltage for I/O signals to FPGA |

| H6 | GND | - | Signal GND |

| H7 | LA02_P | N/C | NC |

| H8 | LA02_N | CH3_LF | CoaXPress channel 3 low speed link TX/RX |

| H9 | GND | - | Signal GND |

| H10 | LA04_P | N/C | NC |

| H11 | LA04_N | N/C | NC |

| H12 | GND | - | Signal GND |

| H13 | LA07_P | N/C | NC |

| H14 | LA07_N | N/C | NC |

| H15 | GND | - | Signal GND |

| H16 | LA11_P | CH0_LED0 | Channel 0 Green indicator LED (Active high) |

| H17 | LA11_N | CH0_LED1 | Channel 0 Red indicator LED (Active high) |

| H18 | GND | - | Signal GND |

| H19 | LA15_P | N/C | NC |

| H20 | LA15_N | N/C | NC |

| H21 | GND | - | Signal GND |

| H22 | LA19_P | CH2_ALERT | Channel 2 PoCXP alert indicator (Active high) |

| H23 | LA19_N | CH1_ALERT | Channel 1 PoCXP alert indicator (Active high) |

| H24 | GND | - | Signal GND |

| H25 | LA21_P | CH1_ON | Channel 1 PoCXP enable (Active high) |

| H26 | LA21_N | CH0_ON | Channel 0 PoCXP enable (Active high) |

| H27 | GND | - | Signal GND |

| H28 | LA24_P | N/C | NC |

| H29 | LA24_N | N/C | NC |

| H30 | GND | - | Signal GND |

| H31 | LA28_P | N/C | NC |

| H32 | LA28_N | N/C | NC |

| H33 | GND | - | Signal GND |

| H34 | LA30_P | N/C | NC |

| H35 | LA30_N | N/C | NC |

| H36 | GND | - | Signal GND |

| H37 | LA32_P | N/C | NC |

| H38 | LA32_N | N/C | NC |

| H39 | GND | - | Signal GND |

| H40 | VADJ | VADJ | Adjustable voltage for I/O signals to FPGA |

| J1 | GND | - | Signal GND |

| J2 | CLK3_BIDIR_P | N/C | NC |

| J3 | CLK3_BIDIR _N | N/C | NC |

| J4 | GND | - | Signal GND |

| J5 | GND | - | Signal GND |

| J6 | HA03_P | N/C | NC |

| J7 | HA03_N | N/C | NC |

| J8 | GND | - | Signal GND |

| J9 | HA07_P | N/C | NC |

| J10 | HA07_N | N/C | NC |

| J11 | GND | - | Signal GND |

| J12 | HA11_P | N/C | NC |

| J13 | HA11_N | N/C | NC |

| J14 | GND | - | Signal GND |

| J15 | HA14_P | N/C | NC |

| J16 | HA14_N | N/C | NC |

| J17 | GND | - | Signal GND |

| J18 | HA18_P | N/C | NC |

| J19 | HA18_N | N/C | NC |

| J20 | GND | - | Signal GND |

| J21 | HA22_P | N/C | NC |

| J22 | HA22_N | N/C | NC |

| J23 | GND | - | Signal GND |

| J24 | HB01_P | N/C | NC |

| J25 | HB01_N | N/C | NC |

| J26 | GND | - | Signal GND |

| J27 | HB07_P | N/C | NC |

| J28 | HB07_N | N/C | NC |

| J29 | GND | - | Signal GND |

| J30 | HB11_P | N/C | NC |

| J31 | HB11_N | N/C | NC |

| J32 | GND | - | Signal GND |

| J33 | HB15_P | N/C | NC |

| J34 | HB15_N | N/C | NC |

| J35 | GND | - | Signal GND |

| J36 | HB18_P | N/C | NC |

| J37 | HB18_N | N/C | NC |

| J38 | GND | - | Signal GND |

| J39 | VIO_B_M2C | VADJ | Adjustable voltage for I/O signals to FPGA |

| J40 | GND | - | Signal GND |

| K1 | VREF_B_M2C | N/C | NC |

| K2 | GND | - | Signal GND |

| K3 | GND | - | Signal GND |

| K4 | CLK2_BIDIR _P | GND | Pulled to GND |

| K5 | CLK2_BIDIR _N | VADJ | Adjustable voltage for I/O signals to FPGA |

| K6 | GND | - | Signal GND |

| K7 | HA02_P | N/C | NC |

| K8 | HA02_N | N/C | NC |

| K9 | GND | - | Signal GND |

| K10 | HA06_P | N/C | NC |

| K11 | HA06_N | N/C | NC |

| K12 | GND | - | Signal GND |

| K13 | HA10_P | N/C | NC |

| K14 | HA10_N | N/C | NC |

| K15 | GND | - | Signal GND |

| K16 | HA17_P_CC | N/C | NC |

| K17 | HA17_N_CC | N/C | NC |

| K18 | GND | - | Signal GND |

| K19 | HA21_P | N/C | NC |

| K20 | HA21_N | N/C | NC |

| K21 | GND | - | Signal GND |

| K22 | HA23_P | N/C | NC |

| K23 | HA23_N | N/C | NC |

| K24 | GND | - | Signal GND |

| K25 | HB00_P_CC | N/C | NC |

| K26 | HB00_N_CC | N/C | NC |

| K27 | GND | - | Signal GND |

| K28 | HB06_P_CC | N/C | NC |

| K29 | HB06_N_CC | N/C | NC |

| K30 | GND | - | Signal GND |

| K31 | HB10_P | N/C | NC |

| K32 | HB10_N | N/C | NC |

| K33 | GND | - | Signal GND |

| K34 | HB14_P | N/C | NC |

| K35 | HB14_N | N/C | NC |

| K36 | GND | - | Signal GND |

| K37 | HB17_P_CC | N/C | NC |

| K38 | HB17_N_CC | N/C | NC |

| K39 | GND | - | Signal GND |

| K40 | VIO_B_M2C | VADJ | Adjustable voltage for I/O signals to FPGA |

1、CoaXPess JIIA CXP-001-2021

2、https://www.cnblogs.com/xingce/category/2165251.html

这篇关于CoaXPress 2.0 FPGA 4 Channel Host and Device FMC Card User Manual的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!