本文主要是介绍北邮22级信通院数电:Verilog-FPGA(6)第六周实验:全加器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

先抄作业!!!!!!!!!!!!!!!!!!!!!!!!没时间写解析了等之后慢慢补吧

实验效果参考视频链接:

数电第六周实验全加器_哔哩哔哩_bilibili

一.verilog 代码 add.v

module add_initial(a,b,ci_1,si,ci);input a,b,ci_1;output si,ci;wire p,g;assign p=a^b;assign g=a&b;assign si=p^ci_1;assign ci=g|(p&ci_1);endmodulemodule my_add(a,b,s,ci,cout);input [3:0] a;input [3:0] b;input ci;output [3:0] s;output cout;wire c1,c2,c3;add_initial u0(.a(a[0]),.b(b[0]),.ci_1(ci),.si(s[0]),.ci(c1));add_initial u1(.a(a[1]),.b(b[1]),.ci_1(c1),.si(s[1]),.ci(c2));add_initial u2(.a(a[2]),.b(b[2]),.ci_1(c2),.si(s[2]),.ci(c3));add_initial u3(.a(a[3]),.b(b[3]),.ci_1(c3),.si(s[3]),.ci(cout));

endmodulemodule add(sw,cal,key_confire_2,key_confire_3,seg_led_1,seg_led_2,clk,rst_n);

input clk;

input rst_n;

input [3:0] sw;

input cal;

input key_confire_2;

input key_confire_3;output reg [8:0] seg_led_1;

output reg [8:0] seg_led_2;reg [8:0] seg [15:0];

initial beginseg[0]=9'h3f;seg[1]=9'h06;seg[2]=9'h5b;seg[3]=9'h4f;seg[4]=9'h66;seg[5]=9'h6d;seg[6]=9'h7d;seg[7]=9'h07;seg[8]=9'h7f;seg[9]=9'h6f;seg[10]=9'h77;seg[11]=9'h7c;seg[12]=9'h39;seg[13]=9'h5e;seg[14]=9'h79;seg[15]=9'h71;endreg [3:0] a;

reg [3:0] b;

reg iscal;wire [3:0]ans;

wire cout;

wire ci;

always@(*)begin

if(rst_n==0)begina=4'b0000;b=4'b0000;iscal=0;end

if(key_confire_2==0)begin a=sw;end

if(key_confire_3==0)begin b=sw;end

if(cal==0)begin iscal=1;end

endmy_add u(.a(a),.b(b),.s(ans),.ci(ci),.cout(cout));

always@(posedge clk)

begin if(iscal)beginseg_led_1<=seg[ans];seg_led_2<=seg[cout];endelsebegin seg_led_1<=seg[a];seg_led_2<=seg[b];end

end

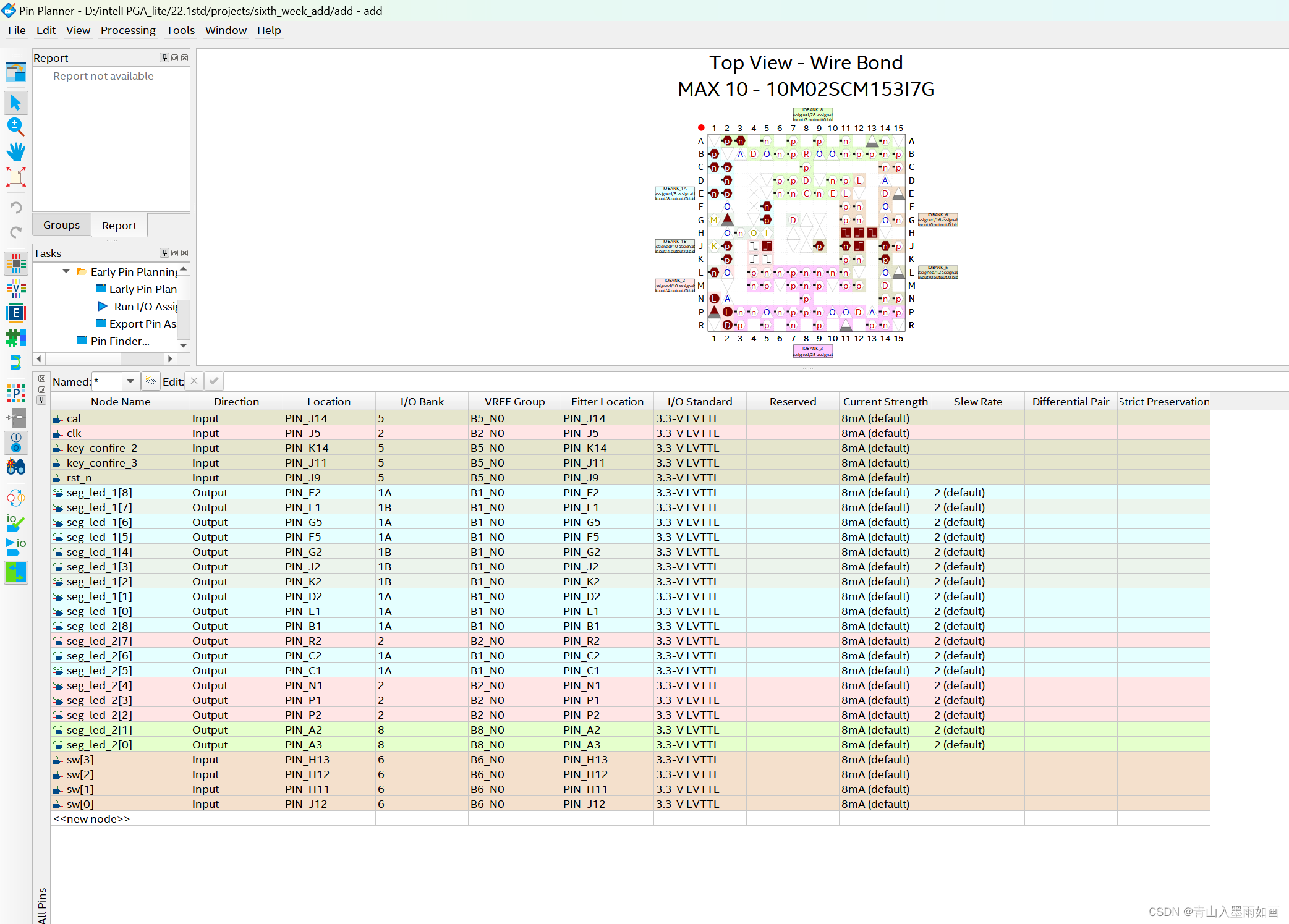

endmodule二.管脚分配

这篇关于北邮22级信通院数电:Verilog-FPGA(6)第六周实验:全加器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!