本文主要是介绍基于Lattice XO2-4000HC FPGA核心板ADS7868驱动模块及波形分析(Verilog),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

- :pushpin: 前言

- :cactus: ADC驱动分析

- ADS7868工作时序分析

- 方案一代码及波形分析

- 方案二代码及波形分析

- :books: 参考资料

📌 前言

本篇文章分析为《基于Lattice XO2-4000HC FPGA核心板及电子森林综合训练底板的ADC数字电压表及OLED显示设计(Verilog)》一文的延伸,针对该项目中的ADS7868驱动模块及工作时序进行分析比对,主要分析了两钟驱动模块的代码及testbench波形。

👉 注意事项及源代码参见原文。

🌵 ADC驱动分析

ADS7868工作时序分析

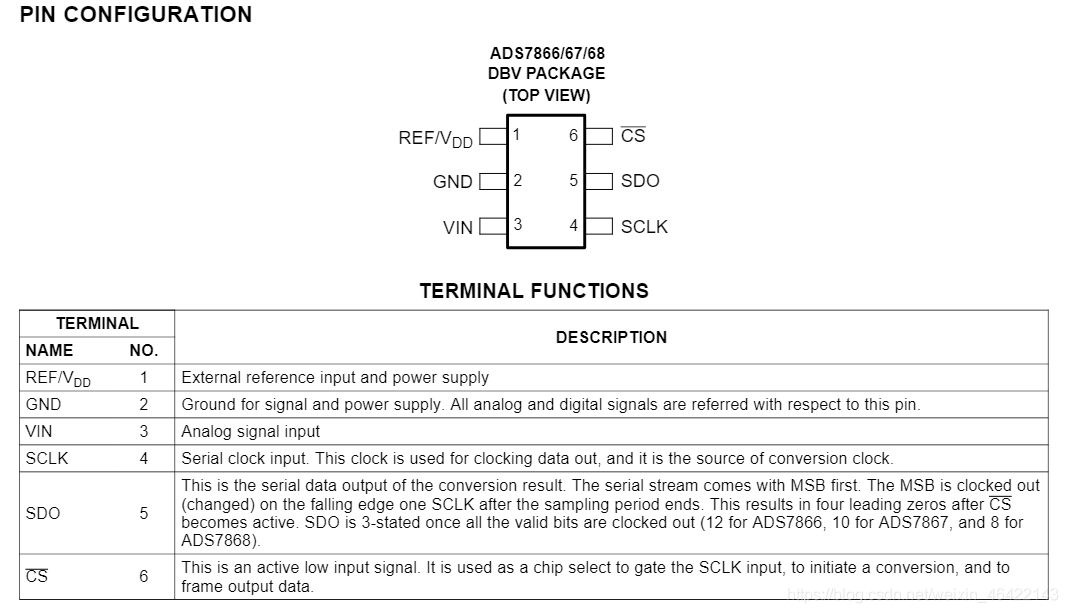

参考ADS7868的数据手册(TI),其各引脚功能如下图所示,不再赘述。简要说明一下SDO端口:

- 该端口每在SCLK时钟下降沿输出数字量,从MSB至LSB,对于ADS7868其分辨率为8位(即8位数字量);

- 当片选信号有效(低电平)后会产生连续4个0,在转换结束后SDO端口呈变为高阻态(Hi-Z)。

💡 着重关注ADS7868的时序图:

- CS片选有效后,在下个SCLK下降沿前,SDO便会输出0,而后的3个SCLK下降沿各输出0;

- 之后每个SCLK下降沿后的小段延时后(tD),会产生新的转换数据,因此可以考虑在SCLK上升沿接收上个下降沿产生的数据;

- 接收8位数字量后,CS置位,一次转换完成,可以考虑产生一次EOC脉冲。

方案一代码及波形分析

起初,参考电子森林:简易电压表设计中关于ADC081S101采样的程序,该程序主要思想是通过计数器编写一个ADC采样时钟(SCLK),根据计数器的值编写对应的操作。由于二者采样的时序有所差别,这体现在真实转换结果的前导0与后导0的个数(可以比较两ADC芯片的转换时序),因此修改相应的操作即可。

module adc_driver_2 #(parameter ADC_WIDTH = 8

)(input sys_clk,input rst_n,input sdo,output reg sclk,output reg adc_csn,output reg [ADC_WIDTH-1:0] adc_data

);localparam HIGH = 1'b1;localparam LOW = 1'b0;reg [7:0] CNT;reg [7:0] data;always @(posedge sys_clk or negedge rst_n) beginif(!rst_n) CNT <= 1'b0;else if(CNT >= 8'd26) CNT <= 1'b0;else CNT <= CNT + 1'b1;endalways @(posedge sys_clk or negedge rst_n) beginif(!rst_n) beginadc_csn <= HIGH; sclk <= HIGH;data <= 8'b0;adc_data <= 8'b0;end else case(CNT)8'd0 : begin adc_csn <= HIGH; sclk <= HIGH; end8'd1 : begin adc_csn <= LOW; sclk <= HIGH; end8'd2,8'd4,8'd6,8'd8,8'd10,8'd12,8'd14,8'd16,8'd18,8'd20,8'd22,8'd24:begin adc_csn <= LOW; sclk <= LOW; end8'd3 : begin adc_csn <= LOW; sclk <= HIGH; end //08'd5 : begin adc_csn <= LOW; sclk <= HIGH; end //18'd7 : begin adc_csn <= LOW; sclk <= HIGH; end //28'd9 : begin adc_csn <= LOW; sclk <= HIGH; data[7] <= sdo; end //38'd11 : begin adc_csn <= LOW; sclk <= HIGH; data[6] <= sdo; end //48'd13 : begin adc_csn <= LOW; sclk <= HIGH; data[5] <= sdo; end //58'd15 : begin adc_csn <= LOW; sclk <= HIGH; data[4] <= sdo; end //68'd17 : begin adc_csn <= LOW; sclk <= HIGH; data[3] <= sdo; end //78'd19 : begin adc_csn <= LOW; sclk <= HIGH; data[2] <= sdo; end //88'd21 : begin adc_csn <= LOW; sclk <= HIGH; data[1] <= sdo; end //98'd23 : begin adc_csn <= LOW; sclk <= HIGH; data[0] <= sdo; end //108'd25 : begin adc_csn <= LOW; sclk <= HIGH; adc_data <= data; end //118'd26 : begin adc_csn <= HIGH; sclk <= HIGH; enddefault:begin adc_csn <= HIGH; sclk <= HIGH; endendcaseendendmodule

注:由于参考的源代码中 adc_done 信号并未控制其他的信号,仅作为响应信号,因此作者将其去掉,但这个信号在作者改进的代码中会使用。

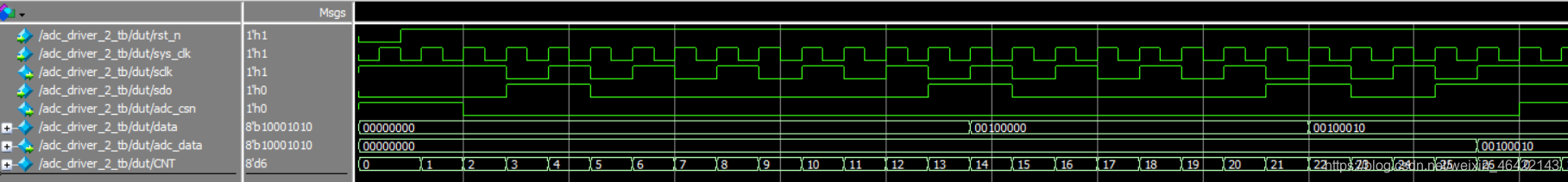

上述程序思路清晰,每个时钟周期的操作非常清晰,但是用计数器编写采样时钟SCLK,导致FCLK = 12MHz / 2 = 6MHz,牺牲了转换速率。这一点在作者的testbenchh验证波形图中可清晰展现。

该模块的testbench代码如下:

`timescale 1ns/1ns

module adc_driver_2_tb;parameter ADC_WIDTH = 8;reg sys_clk;reg rst_n;reg sdo;wire sclk;wire adc_csn;wire [ADC_WIDTH-1:0] adc_data;adc_driver_2 #(.ADC_WIDTH(ADC_WIDTH)) dut(.sys_clk(sys_clk),.rst_n(rst_n),.sdo(sdo),.sclk(sclk),.adc_csn(adc_csn),.adc_data(adc_data));initial beginsys_clk <= 1'b0;rst_n <= 1'b0;sdo <= 1'b0;#20 rst_n <= 1'b1;#1200 $stop;endalways @(negedge sclk) beginsdo <= $urandom_range(0,1);endalways #10 sys_clk = ~sys_clk;endmodule

⚠️ 注意:ADC转换后数字量(sdo)每SCLK下边沿(negedge sclk)才产生,在tb里通过$urandom_range(0,1)随机产生0或1,虽然在转换前为3个0,但是即便不是0,ADC驱动也不能将其接收。

testbench波形图如下图所示:

ADC驱动在CNT = 9,11,13,15,17,19,21,23接收转换结果至data,在CNT = 25送至输出(adc_data),CNT = 26结束后,片选信号拉高,一次转换结束。

方案二代码及波形分析

方案二结合ADS7868工作时序,通过状态机实现驱动,代码如下。

`timescale 1ns/1ns

module adc_driver #(parameter ADC_WIDTH = 8

)(input sys_clk,input rst_n,input sdo,output sclk,output reg adc_csn,output reg [ADC_WIDTH-1:0] adc_data

);localparam IDLE = 2'b00;localparam HOLD = 2'b01;localparam CONVERT = 2'b10;localparam FINISH = 2'b11;wire adc_eoc;reg [ADC_WIDTH-1:0] adc_data_reg;reg [1:0] state;reg [1:0] CNT_0;reg [2:0] CNT_data;assign sclk = sys_clk;assign adc_eoc = (state == FINISH);always @(posedge sys_clk or negedge rst_n) beginif(!rst_n)adc_csn <= 1'b1;else if(adc_eoc)adc_csn <= 1'b1;elseadc_csn <= 1'b0;endalways @(posedge sys_clk or negedge rst_n) beginif(!rst_n) beginstate <= IDLE;adc_data <= 8'b0;adc_data_reg <= 8'b0;CNT_0 <= 2'b10;CNT_data <= 3'b111;endelsecase(state)IDLE: beginstate <= HOLD;endHOLD: beginCNT_0 <= CNT_0 - 1'b1;if(CNT_0 == 0) beginstate <= CONVERT;CNT_0 <= 2'b10;end elsestate <= HOLD;endCONVERT: beginCNT_data <= CNT_data - 1'b1;adc_data_reg <= {adc_data_reg[ADC_WIDTH-2:0], sdo};if(CNT_data == 0) beginstate <= FINISH;CNT_data <= 3'b111;endelsestate <= CONVERT;endFINISH: beginadc_data <= adc_data_reg;state <= IDLE;enddefault: state <= IDLE;endcaseendendmodule

较方案一,改进有:

CNT_0与CNT_data根据实际ADC的工作时序可以灵活调整;- 加入了

adc_eoc转结束信号,在FINISH阶段作出判断以控制片选(adc_csn); - ADC的时钟直接为系统时钟(

sys_clk),因此较方案一更优。

该方案testbench代码如下:

`timescale 1ns/1ns

module adc_driver_tb;parameter ADC_WIDTH = 8;reg sys_clk;reg rst_n;reg sdo;wire sclk;wire adc_csn;wire [ADC_WIDTH-1:0] adc_data;adc_driver #(.ADC_WIDTH(ADC_WIDTH)) dut(.sys_clk(sys_clk),.rst_n(rst_n),.sdo(sdo),.sclk(sclk),.adc_csn(adc_csn),.adc_data(adc_data));initial beginsys_clk <= 1'b0;rst_n <= 1'b0;#20 rst_n <= 1'b1;#1200 $stop;endalways @(negedge sclk) beginsdo <= $urandom_range(0,1);endalways #10 sys_clk = ~sys_clk;endmodule

⚠️ 注意:sdo同样在sclk下边沿产生。

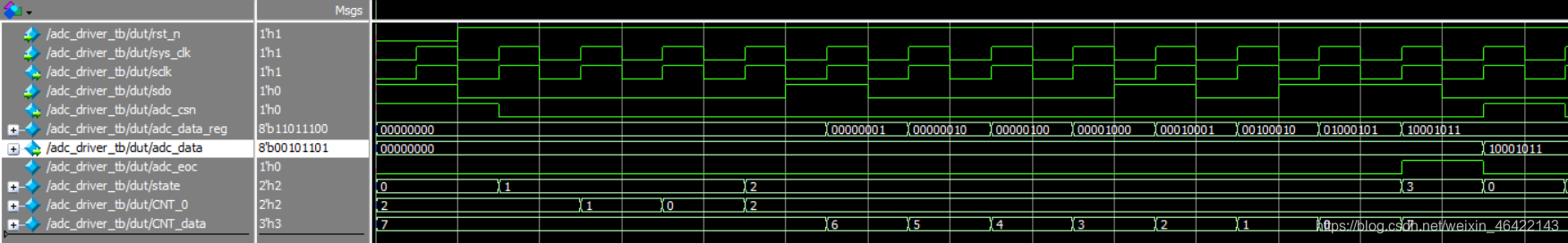

testbench波形图如下图所示:

根据state状态,CNT_0与CNT_data的计数,ADC转换的流程十分清晰。在CNT_data为0后,state转为3,adc_eoc产生一个SCLK的脉冲,在下个上边沿处,片选拉高,片选信号在拉高后的下一个上升沿处又拉低(此时adc_eoc恢复为0),因此实现了片选信号的控制。

📚 参考资料

[1] TI:ADS7868数据手册.pdf

[2] 电子森林:简易电压表设计

这篇关于基于Lattice XO2-4000HC FPGA核心板ADS7868驱动模块及波形分析(Verilog)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!