本文主要是介绍紫光同创FPGA学习之DDR3控制器IP仿真(方法1),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本仿真的DDR3控制器IP仿真直接使用紫光同创提供的example_design,使用modelSIM来仿真。

所使用的的软件为 Pango Design Suite 2020.3-Lite ,Modelsim SE-64 2020.4,两者的关联请参考help 文档。

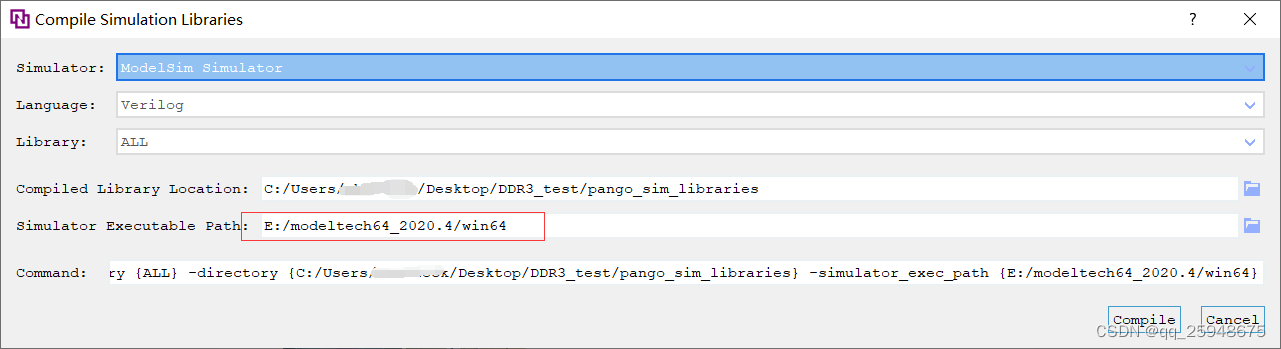

注意要填好自己电脑的modelSIM安装路径,一定要对(Tools->compile simulation libraries)

接下来开始具体的仿真文件获取。

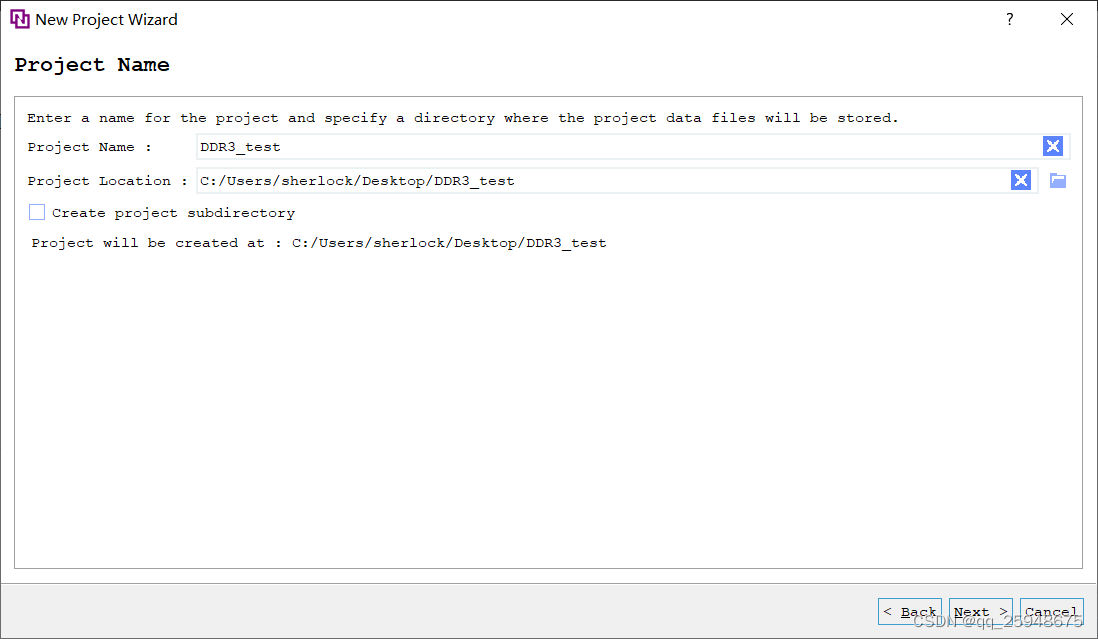

首先打开PDS,新建工程:

选择好路径(这里是桌面的一个文件夹)

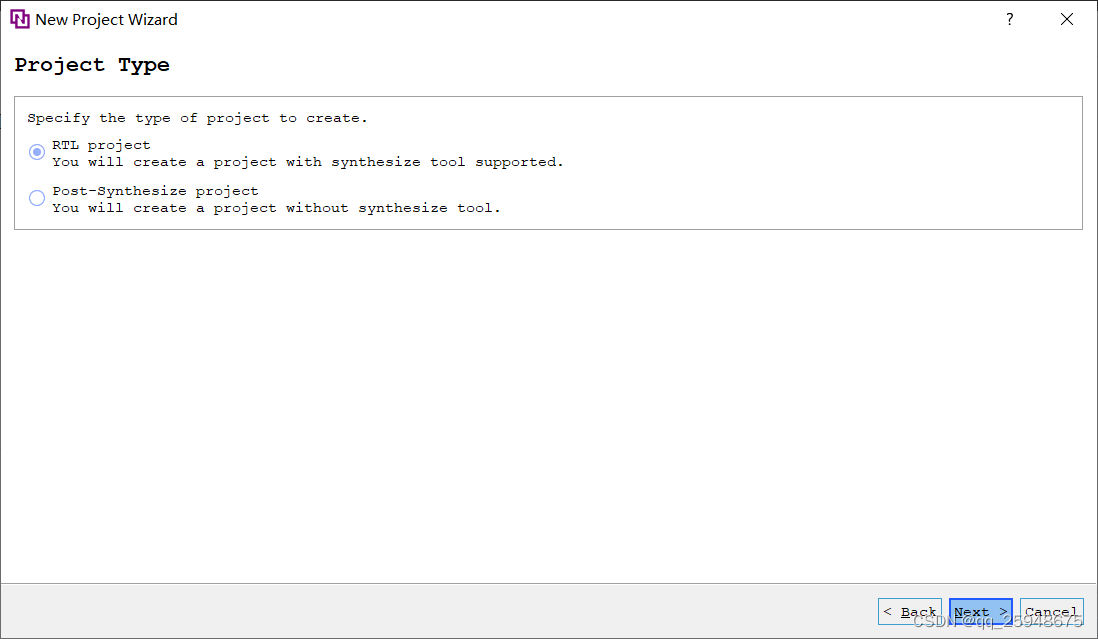

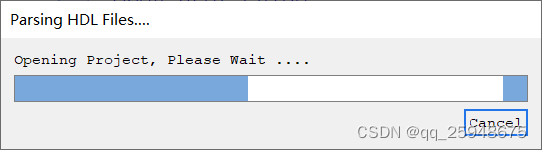

一直点击next,最后到finish(器件型号可以自行选择,我这里都选默认了)

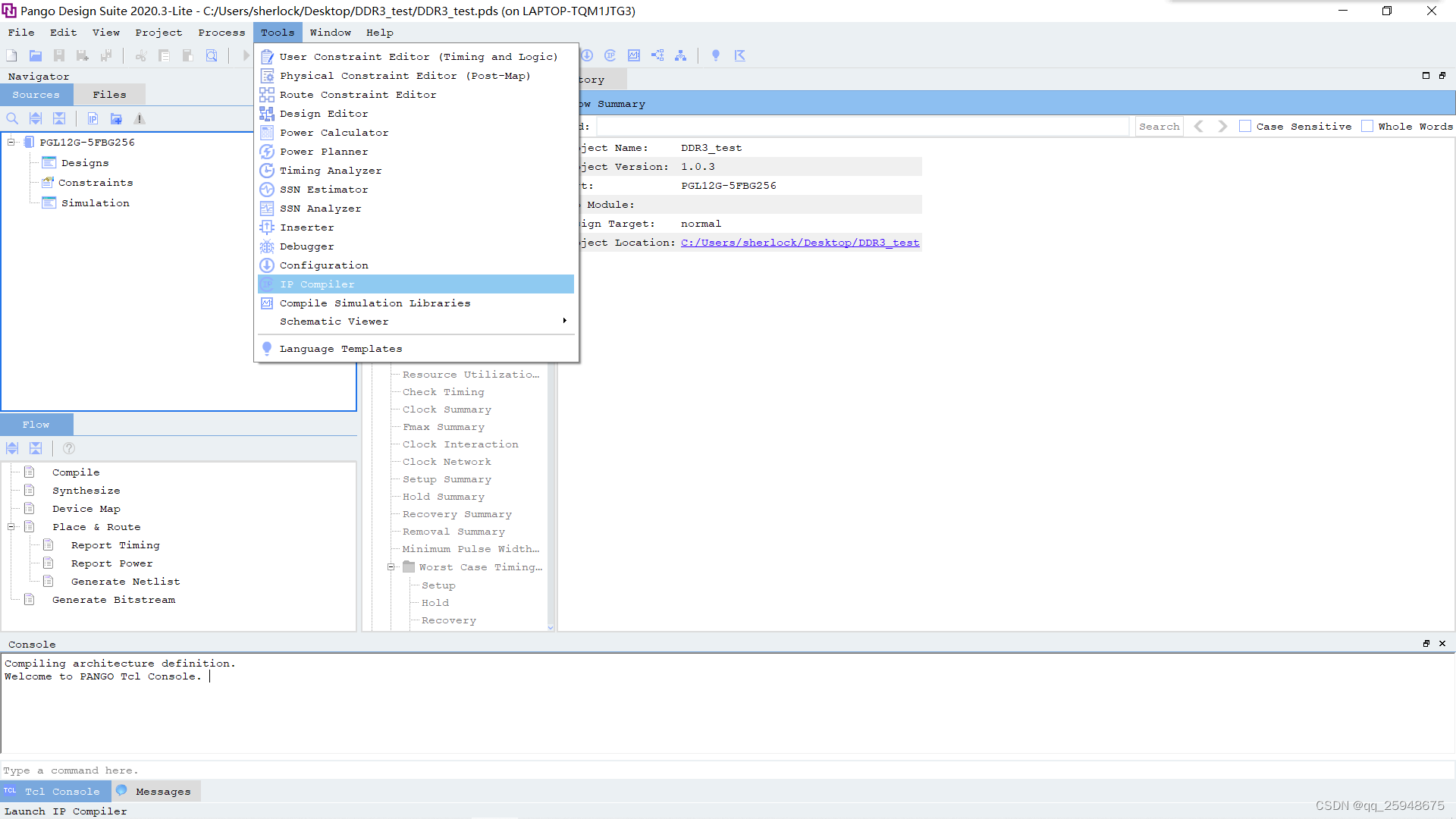

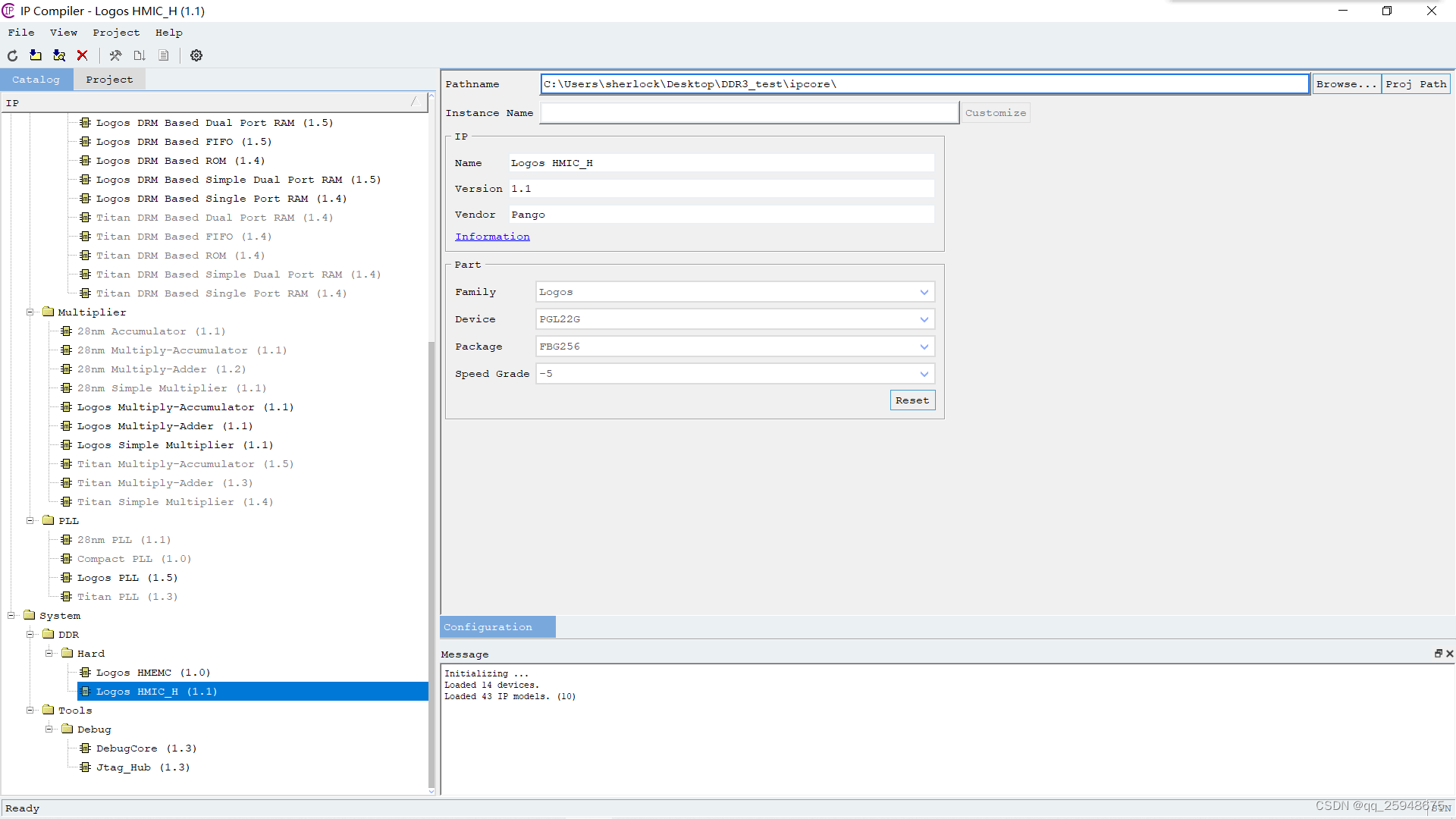

接下来添加DDR3控制器的IP,点击TOOLs->IP compiler

如下:

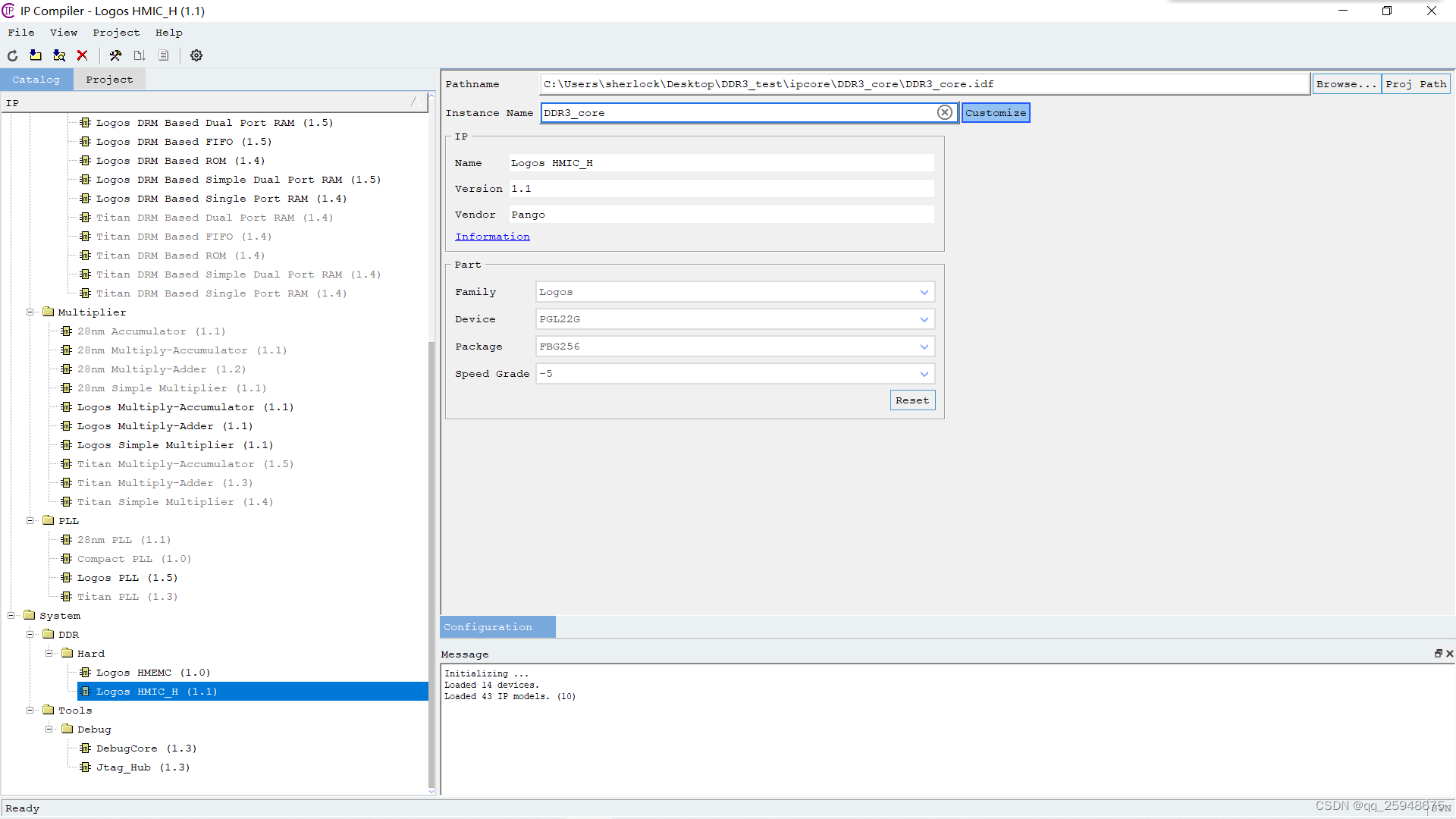

选择system-> DDR->Hard->Logos HMI_H (1.1),命名后点击customise

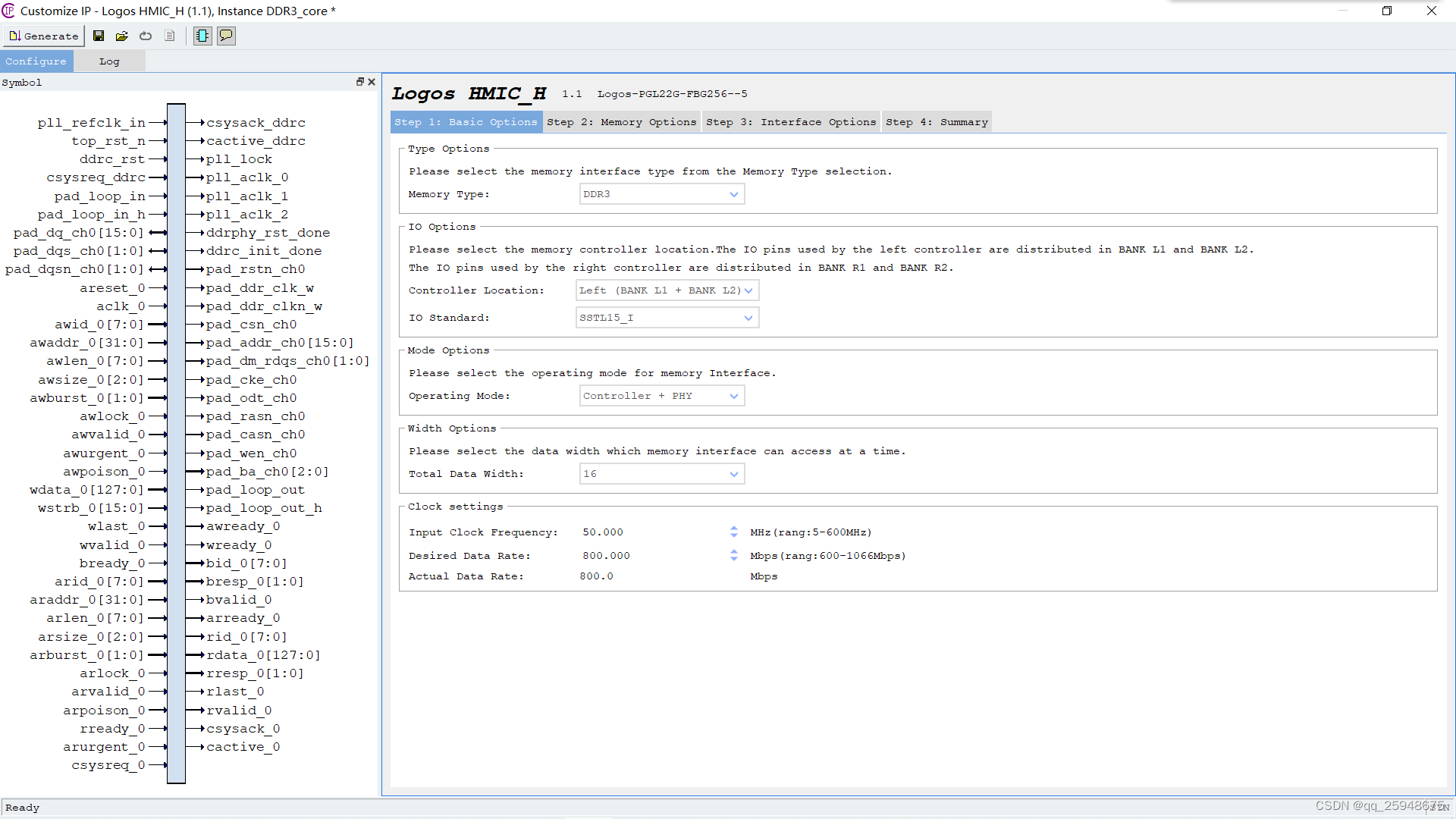

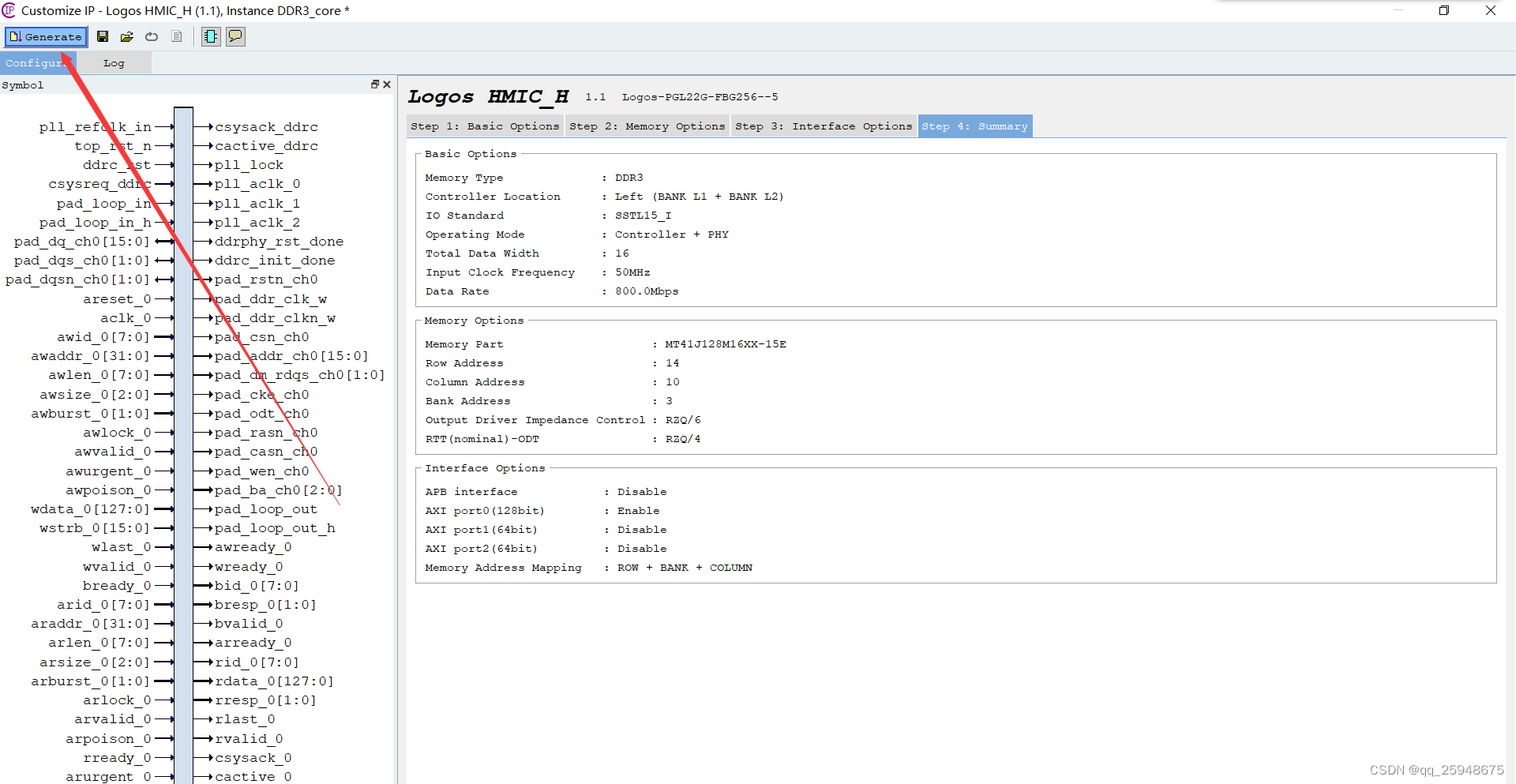

之后依次配置,详情参考说明文档

配置完毕点击generate,按提示依次点击

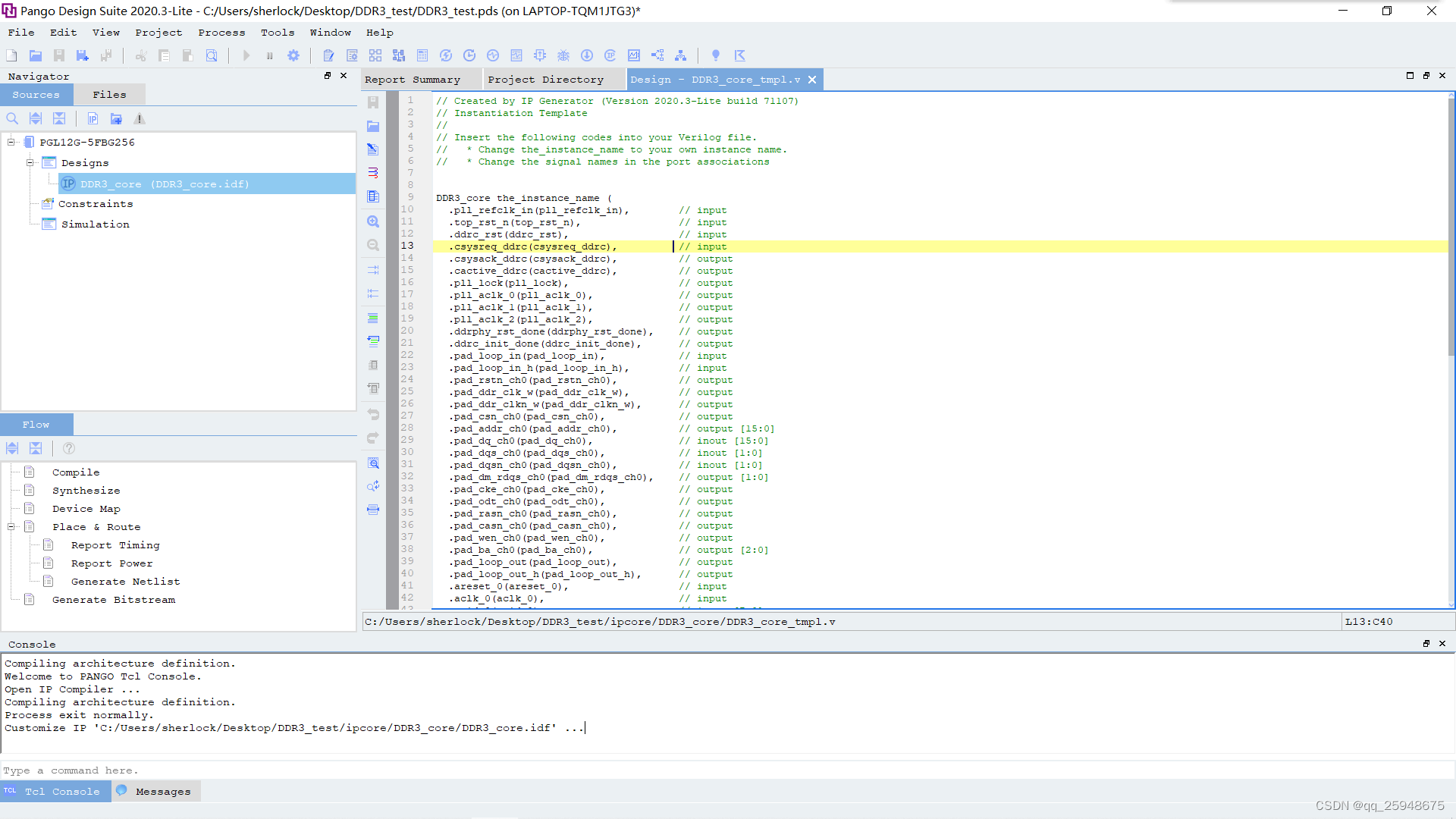

之后,回到pds主界面如下

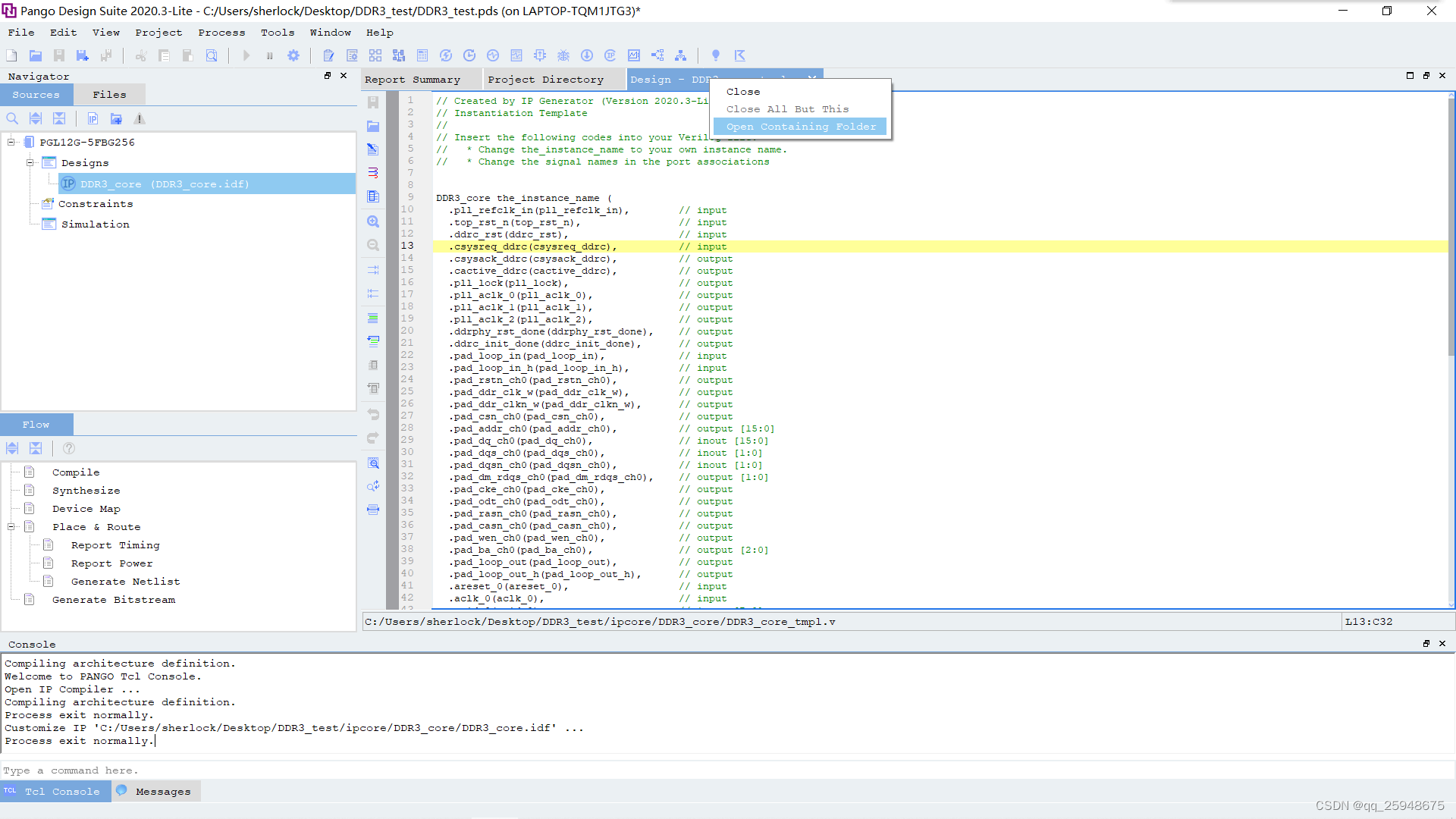

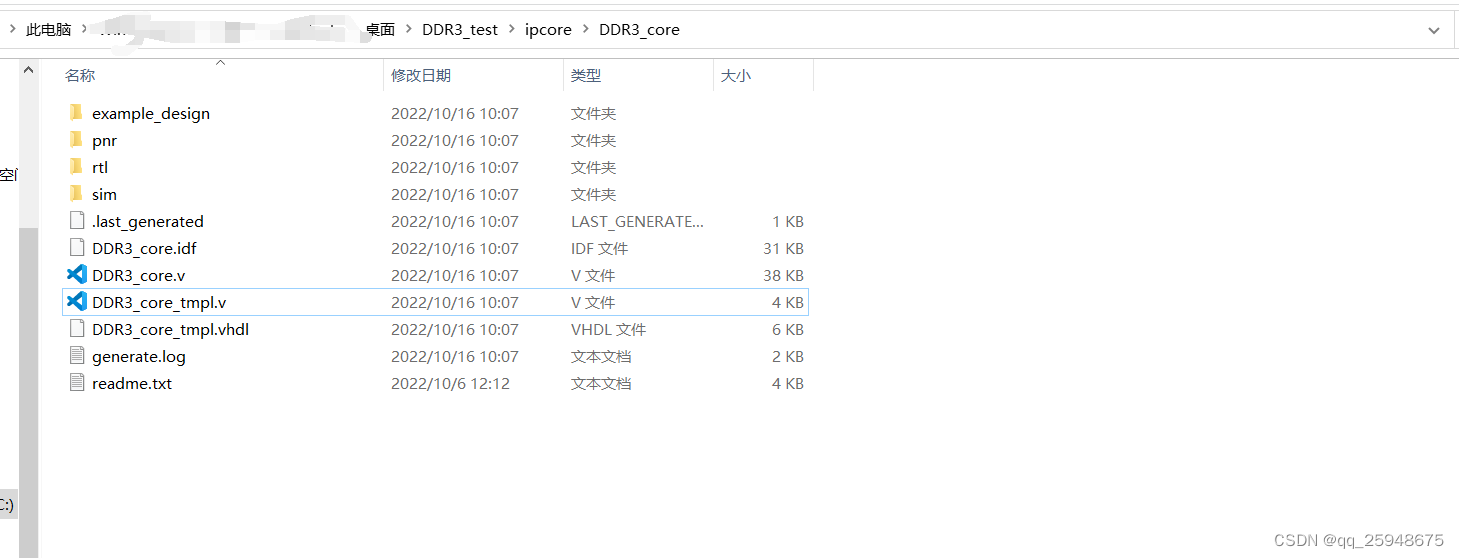

打开DDR3_core_tmpl.v所在文件夹

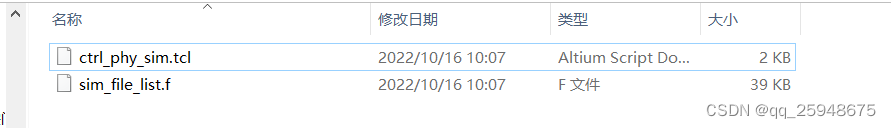

打开sim文件夹

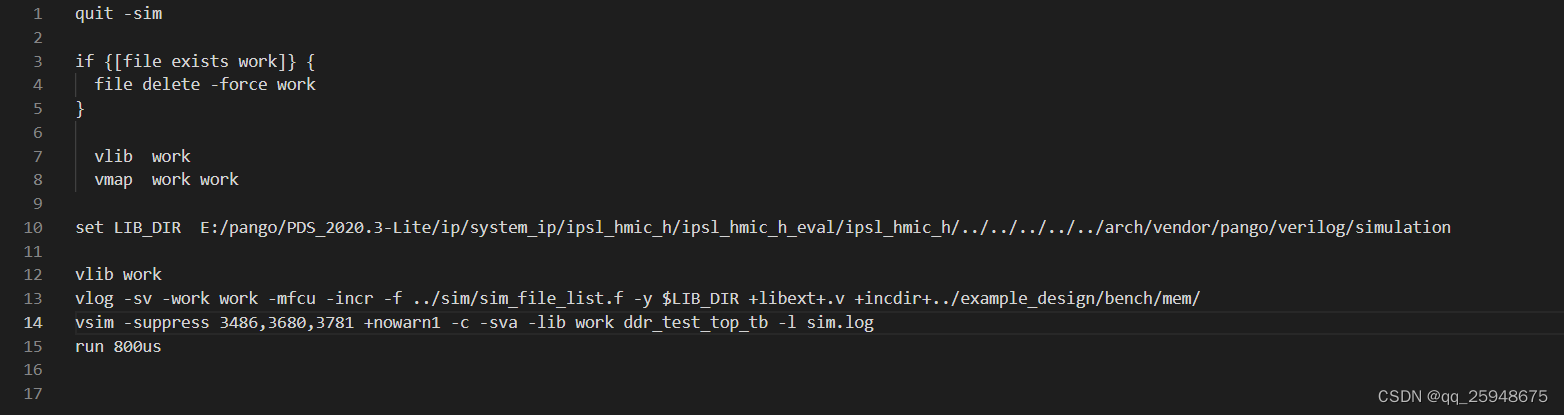

打开ctrl_phy_sim.tcl(我用的vs code)

如下:

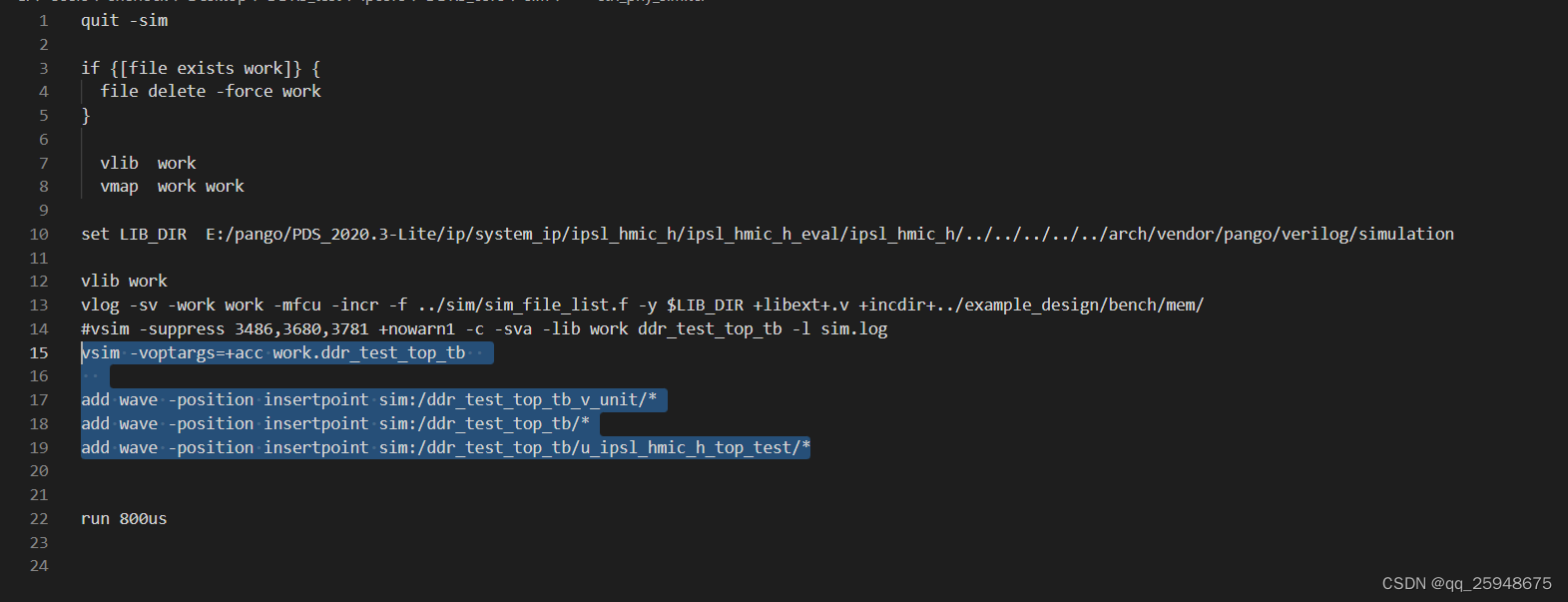

进行如下修改:

vsim 是仿真指令,这里做了修改。add wave是添加仿真波形。

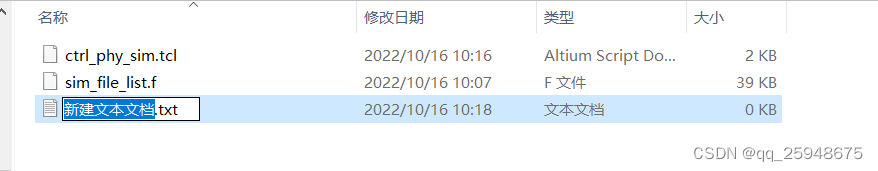

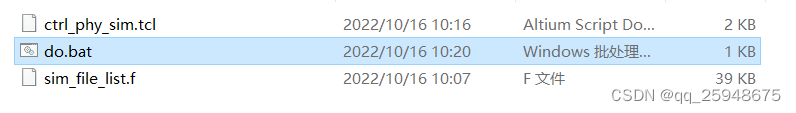

接下来编写bat文件(也可以直接打开modelSIM执行ctrl_phy_sim.tcl),新建文本文档:

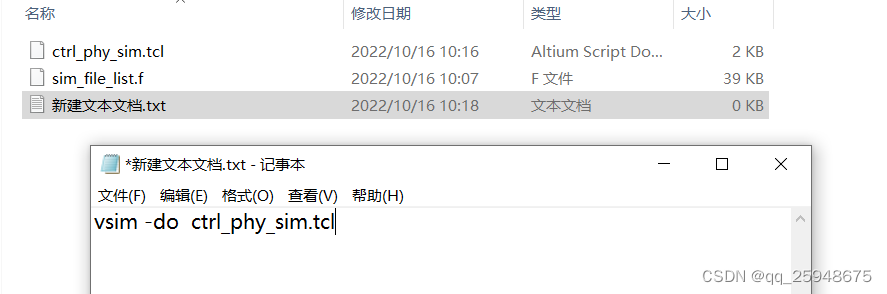

写入内容 vsim -do ctrl_phy_sim.tcl并保存,命名为do.bat

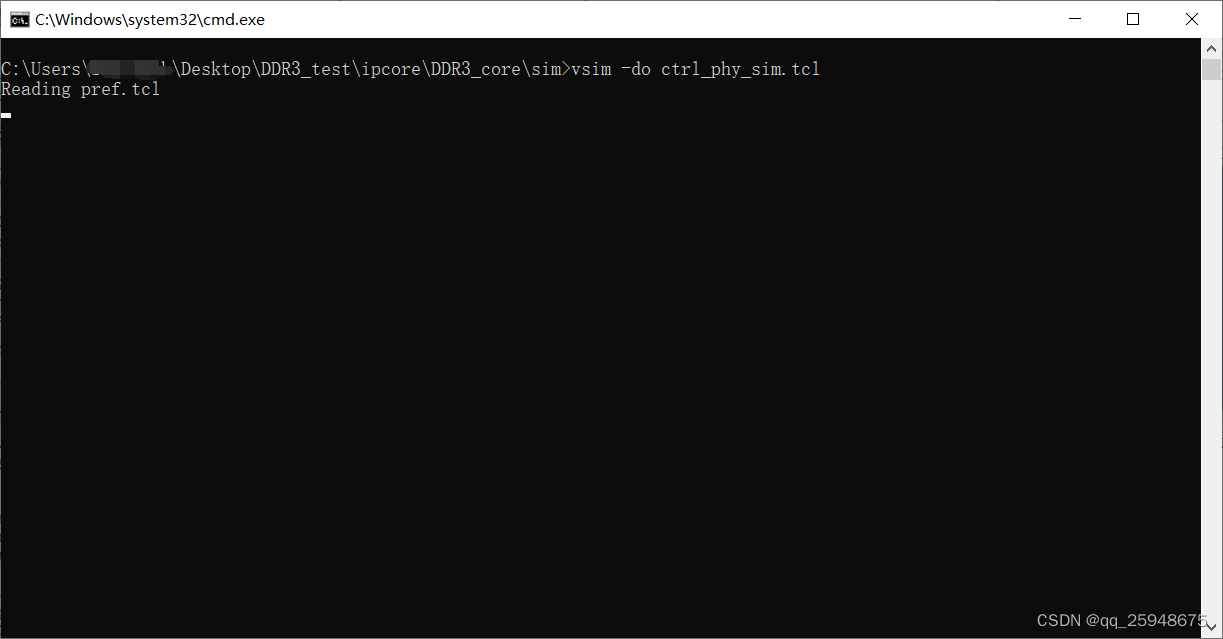

双击do.bat即可完成仿真。

双击do.bat即可完成仿真。

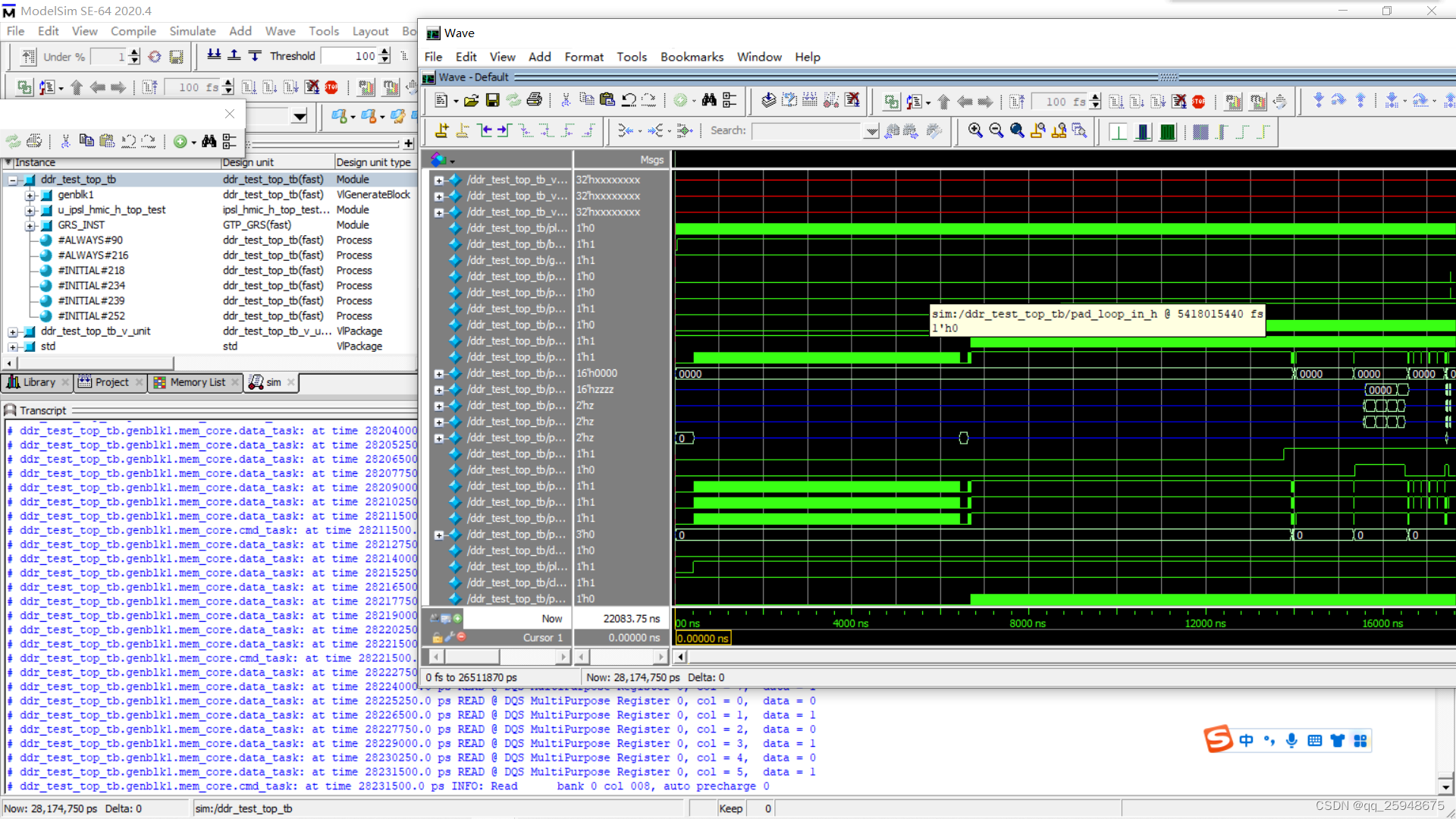

之后,就可以自行观察波形了。

这篇关于紫光同创FPGA学习之DDR3控制器IP仿真(方法1)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!