本文主要是介绍java实现输出加法表_米联客(MSXBO)通过简单的加法器了解LUT查找表实现加法功能...,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

米联客(MSXBO)通过简单的加法器了解LUT查找表实现加法功能

1.1概述

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构。LUT本质上就是一个RAM。它把数据事先写入RAM后, 每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

7系列FPGA中的函数发生器实现为六输入查找表(LUT)。slice的4个函数发生器(A,B,C和D)中的每一个都有六个独立输入(A输入A1至A6)和两个独立输出(O5和O6)。

这篇短文中,我们通过一个简单的加法器来了解下LUT如果实现加法器功能。

1.2加法器代码

module ADDER(

input [0:0]A,

input [0:0]B,

output [1:0]Q

);

assign Q = A + B;

endmodule

1.3加法器原理图

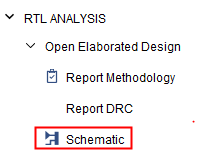

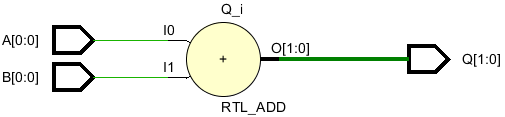

从VIVADO 左侧的 RTL ANALYSIS选择打开原理图

加法器原理图如下图所示

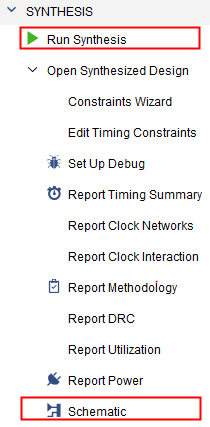

1.4综合代码后查看原理图

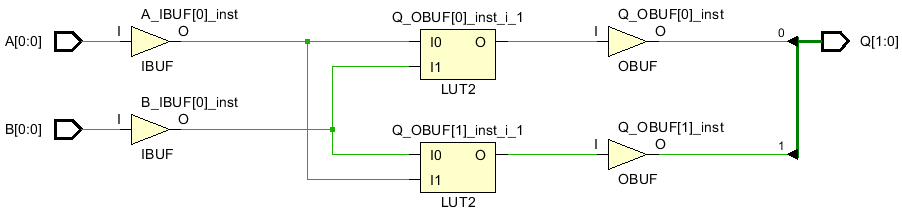

综合后的原理图可以看到IBUF以及LUT和OBUF

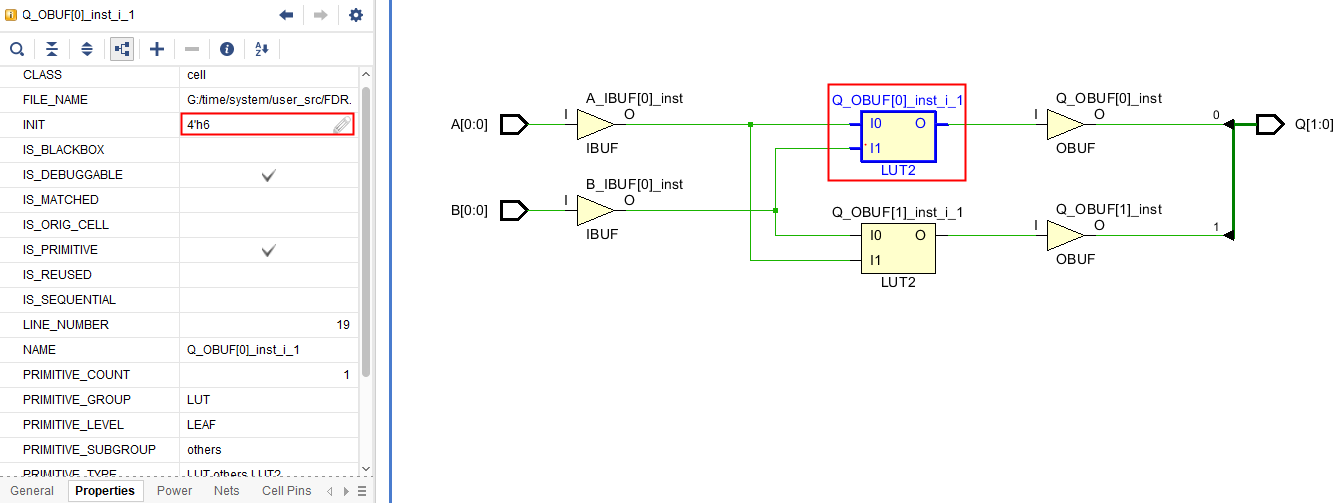

单击红框的LUT2单元,然后在左手边查看LUT2的属性

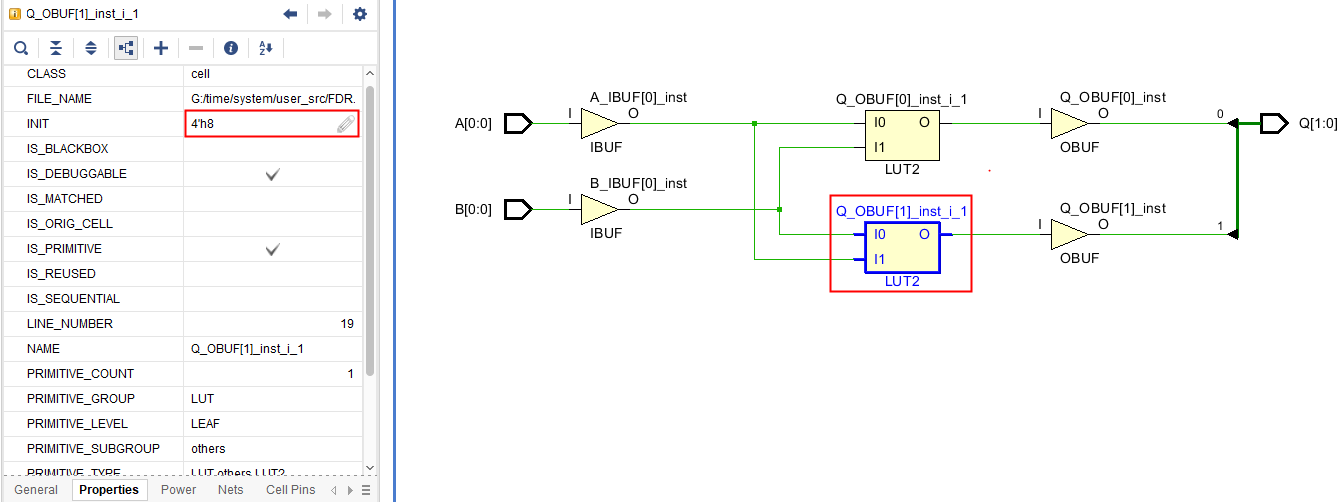

同理单击红框的LUT2单元,然后在左手边查看LUT2的属性

可以看到以上图中的初始值,就是LUT查找表的值,通过查表我们可以看到加法器的可以执行的结果。

A

B

ADDR

Q_OBUF[0]_inst_i_1

ADDR

Q_OBUF[1]_inst_i_1

Q[1:0]

0

0

0

0

0

0

2’b00

1

0

1

1

2

0

2’b01

0

1

2

1

1

0

2’b01

1

1

3

0

3

1

2’b10

通过以上的简单分析,相信大家可以掌握LUT实现逻辑单元功能的本质了。

这篇关于java实现输出加法表_米联客(MSXBO)通过简单的加法器了解LUT查找表实现加法功能...的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!