联客专题

[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-30 RS485串口程序收发环路设计

软件版本:VIVADO2021.1 操作系统:WIN10 64bit 硬件平台:适用 XILINX A7/K7/Z7/ZU/KU 系列 FPGA 实验平台:米联客-MLK-H3-CZ08-7100开发板 板卡获取平台:https://milianke.tmall.com/ 登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑! 目录 1概述

[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-25 RGB转HDMI显示方案

软件版本:VIVADO2021.1 操作系统:WIN10 64bit 硬件平台:适用 XILINX A7/K7/Z7/ZU/KU 系列 FPGA 实验平台:米联客-MLK-H3-CZ08-7100开发板 板卡获取平台:https://milianke.tmall.com/ 登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑! 目录 1概述

[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-22读写I2C接口的RTC时钟芯片

软件版本:VIVADO2021.1 操作系统:WIN10 64bit 硬件平台:适用 XILINX A7/K7/Z7/ZU/KU 系列 FPGA 实验平台:米联客-MLK-H3-CZ08-7100开发板 板卡获取平台:https://milianke.tmall.com/ 登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑! 目录 1概述

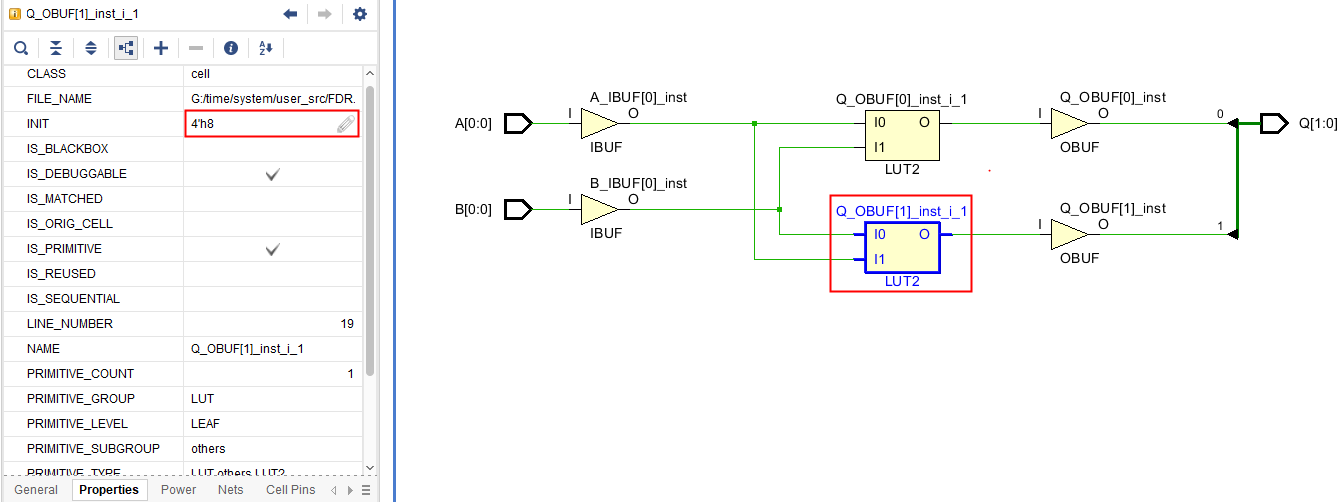

java实现输出加法表_米联客(MSXBO)通过简单的加法器了解LUT查找表实现加法功能...

米联客(MSXBO)通过简单的加法器了解LUT查找表实现加法功能 1.1概述 由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构。LUT本质上就是一个RAM。它把数据事先写入RAM后, 每当输入一个信号就等于输入一个地址进行查表,找出地

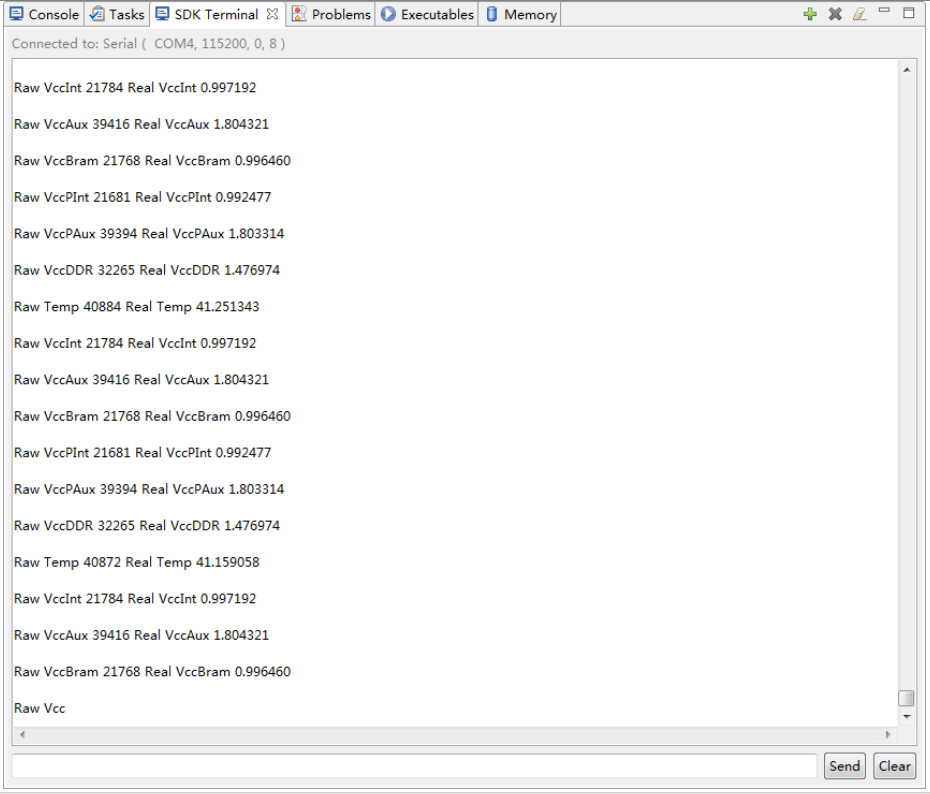

米联客 ZYNQ/SOC精品教程 S02-CH03 XADC 实验

软件版本:VIVADO2017.4 操作系统:WIN10 64bit 硬件平台:适用米联客 ZYNQ系列开发板 米联客(MSXBO)论坛:www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问!! 3.1 概述 本课讲解了使用芯片内部XADC采集片上电压以及温度的方法。 Xilinx 7系列的ADC是一个双12位分辨率的而且每秒一兆(MSPS, 1 Mega sa

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-30 RS485串口程序收发环路设计](https://i-blog.csdnimg.cn/direct/320b5c48ecbf46a2b876f556cbe213e5.png)

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-25 RGB转HDMI显示方案](https://i-blog.csdnimg.cn/direct/25b76f71a6f14056b4f4bfed14f6fa08.png)

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-22读写I2C接口的RTC时钟芯片](https://i-blog.csdnimg.cn/direct/1051dc21e2c34ea0aec68ad6ad598ca9.png)