本文主要是介绍FPGA的基本架构、IO命名方式和作用,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

今天想和大家一起聊聊 FPGA 的 IO。先说说我当年入门的经历吧。国内的大学有 FPGA 开发条件的实验室并不太多,当年大学的那帮同学有的做 ARM,有的做 linux,很少有人做 FPGA,当时学 FPGA 仅仅是由于非常渴望的好奇心。所以,在淘宝买了一块开发板,就开始了自己的 FPGA 之路。

大部分开发板的内容主要是教学员怎么样写 Verilog 代码,很少会对 FPGA 的芯片架构做详细的说明和解读,所以当年面试的时候就碰到了一个很尴尬的事情,面试官第一个问题问的就是:用的是哪颗 FPGA,内核电压是多少?当时就懵了,虽然做了快一年 FPGA,我还没有关注过芯片的内核电压···。

但其实熟悉 FPGA 的基本架构,了解 FPGA 的芯片内部资源真的很重要。

虽然很多 FPGA 工程师都是写代码,但是作为硬件编程工程师,如果不熟悉 FPGA 的底层资源和架构,是很难写出高质量的代码——至少很难写出复杂逻辑的高质量代码,也很难站在系统的层面去考虑芯片的选型等问题。那熟悉 FPGA 架构,首先最主要的一点,我们先来了解 FPGA 的 IO。

FPGA 的 IO 命名。FPGA 芯片 IO 命名方式太多,管脚也多,让人感觉很乱。这是我当年的感觉,诸如会经常听到:A13,B14···BANK34,BANK12····MIO0,EMIO···。但这确实是 FPGA 的特点,FPGA 可以兼容多种不同的电压标准,也有丰富的 IO。

首先,FPGA 的 IO 物理命名规则,也就是我们做管脚约束时候的命名,芯片通常是长方体或者正方体,所以命名通常采用字母+数字组合的方式,从上到下是字母(A,B,C,D```),从左到右是数字(1,2,3```),所以诸如:A13(见下图),就是图上标红的位置,这个是 xilinx 的一颗芯片示意图,其它厂商的 FPGA 芯片也类似。

其次,FPGA的功能命名规则。功能命名规则每个厂家都会自己的一套规则,但都大同小异,我们重点来讲述一下 xilinx 的命名(xilinx 的文档是行业标杆,其它 FPGA 厂家的资料多多少少会参考 xilinx)。通常 xilinx 的功能命名格式为:IO_LXXY#/IO_XX。其中:

(1) IO 代表用户 IO;

(2) L 代表差分,XX 代表在当前 BANK 下的唯一标识号,Y=[P|N]表示 LVDS 信号的 P 或者 N;

(3) #表示 Bank 号。

比如,我们的原理图中有一个 IO 的名字为:IO_L13P_T2_MRCC_12,那通过功能命名的规则我们就可以知道,这是一个用户 IO,支持差分信号,是 BANK12 的第 13 对差分的 P 端口,与此同时它也是全局时钟网络输入管脚(MRCC 是全局时钟网络)。

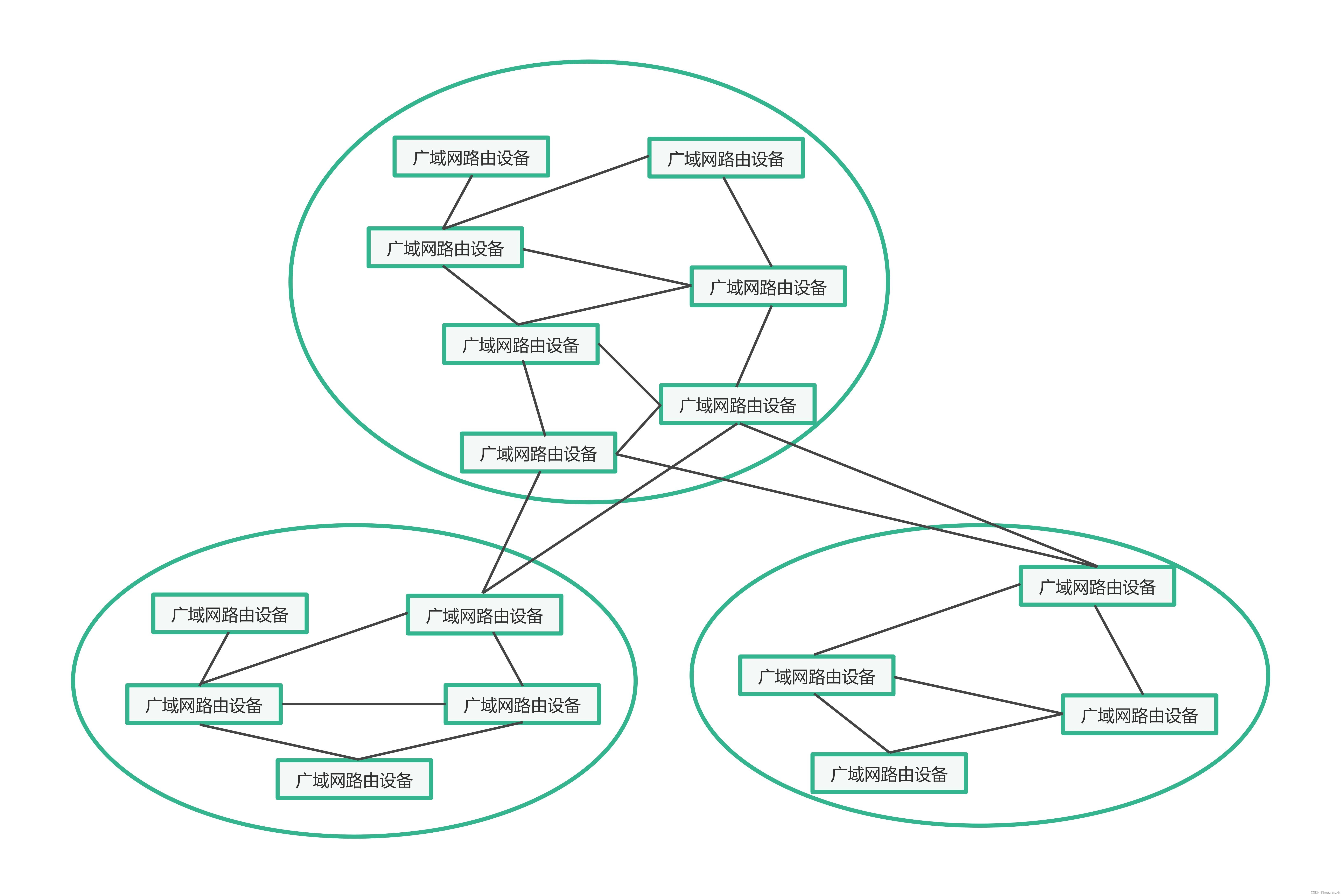

再次,什么是 Bank。Bank 是一组物理位置和特性相近的 IO 的总称,同一 BANK 的电压的基准是一致的,因此,通常如果我们需要各种不同标准的电压,可以通过给到 BANK 的电压基准不同的方式来实现多种电平标准的输入输出。通常封装越大,BANK 数量也越多,可以支持电压标准也越多。如下图就是 ZYNQ 7030 的一个 IO BANK 分布图:

除了 FPGA 的用户 IO 外,还有很多其他的功能 IO,如下载接口,模式选择接口,还有 MRCC,也即我们前文讲到的全局时钟网络和局部时钟网路等。其中最值得关注的是 FPGA 的电源引脚,其中 ZYNQ 器件包含两套完全独立的供电系统,一套是嵌入式端的电源(PS),一套是逻辑端的电源(PL),两套供电系统完全独立,因此也没有先后上电的时序需求。如下:

通常包含的电压有:

(1) 内核电压,Vccpint 和 Vccint 分别为 PS 的内核电压和 PL 的内容电压,内核电压的大小通常和工艺相关,如 48nm XILINX 器件的内核电压为 1.2v,28nm 的 ZYNQ 器件的内核电源为 1.0v(通常电压都有一个范围,范围也和速度等级相关),当然,电压越低,在同样逻辑规模和主频下,对应的功耗也会越低。

(2)Vccpaux 和 Vccaux 分别为 PS 和 PL 的辅助电压。在 ZYNQ 器件中为 1.8v。

(3) Vccpll 为内部锁相环供电电压。

(4) Vcc_mio0 为 PS 的 MIO0 BANK 的基准电压,VCCO_DDR 为 PS 端的 DDR 的电压,此电压通常和选择的 DDR 颗粒相关,如(DDR3,LDDR3 等相对应的值就有所不同,这一部分我们都要在相关视频中做详细解读)。

(5) Vccon 这部分就我们前面讲到的 PL 端的 Bank 基准。

对于纯逻辑的 FPGA 器件,由于没有 PS 端,因此相应的 PS 端供电就没有,只有 PL 端的供电,实现更简单。

最后,我们来聊聊 FPGA 的上电。和所有的器件一样,FPGA 的上电遵循一定的上电逻辑,通常情况下 SRAM 结构(XILINX、Altera 等都属于 SRAM 结构)的上电时间会比 FLASH 结构的(Microm,Actel 等)上电时间要长。有些国产 FPGA 为了简化 BOM 成本(如安路半导体)不需要用户特别关注上电时序,用单电源供电,芯片内部控制上电时序。虽然不合理的上电时序有时候也能让 FPGA 正常工作,但不正常的上电或掉电过程有可能会造成瞬时电流过大,无法保证上电期间 FPGAIO 为三态,甚至损坏芯片,因此需要设计者特别关注上电时序。针对 XILINX FPGA 的上电通常需要遵循以下规则:

(1)在PS 端,Vccpint,Vccpaux,Vccpll 一起上电,后启动 PS 的 Vcco 电源(Vcco_mio0,Vcco_mio1,Vcco_ddr),其中 PS_POR_B 在上电期间应保持低电平,直到内核,辅助电压,PLL 电压和 BANK 的电压达到相应阈值。掉电的顺序和上电顺序保持一致。

(2)在 PL 端,推荐的上电顺序依次为 Vccint,Vccbram,Vccaux,Vccaux_io,Vcco。其中,如果 Vccint 和 Vccbram 是相同的电压,则可以采用同一电源供电,同时启动。Vccaux,Vccaux_io 和 Vcco 为同一电压则亦可以采用同一电源,同时启动。

除此,在设计 FPGA 的原理图中要需要特别关注 Serdes 的供电(不同的厂家,甚至同一厂家不同的器件对 Serdes 都有不同的名称,如:GTH,GTX 等等,但实质都是自同步的高速串行收发器,支持的速率有所差别),不使用的情况下需相应的悬空或者接地。

这篇关于FPGA的基本架构、IO命名方式和作用的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[FPGA][基础模块]跨时钟域传播脉冲信号](/front/images/it_default.jpg)