本文主要是介绍vivado PIN,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

描述

引脚是基元或层次单元上的逻辑连接点。引脚允许

要抽象掉单元格的内容,并简化逻辑以便于使用。引脚可以

是标量的,包含单个连接,或者可以定义为对多个进行分组的总线引脚

信号在一起。

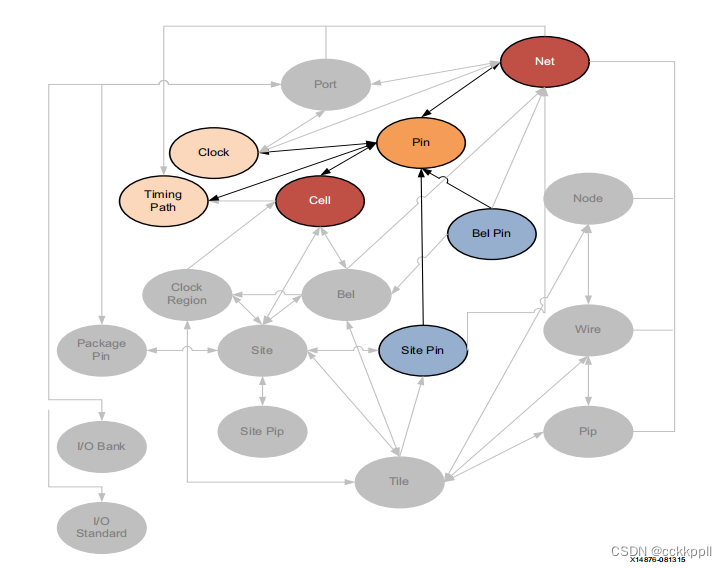

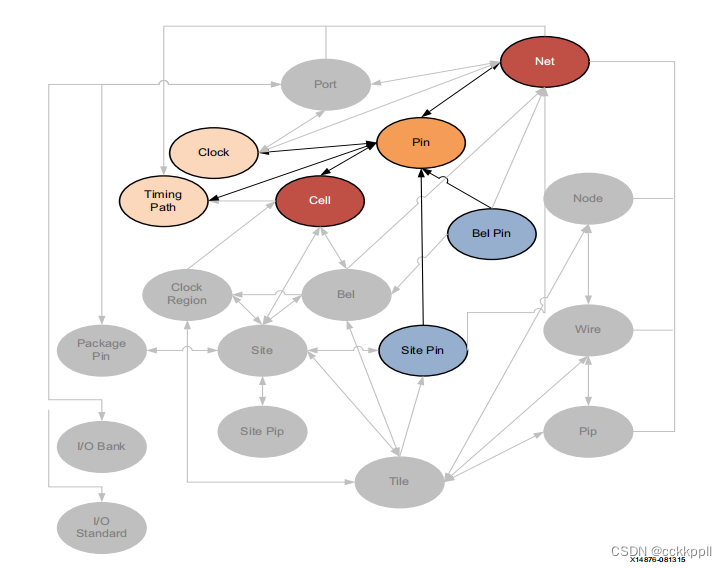

相关对象

引脚连接到一个单元,并且可以通过网络连接到其他单元上的引脚。的引脚

单元格还与bel对象的bel_pins或该单元格所在的site的site_pins相关

映射到。引脚作为时钟域的一部分与时钟相关联,并且是的一部分

timing_path(定义为路径的起点、终点或通过点时)。

端号也可以与drc_contractions相关联,以便更快地定位和

解决设计问题。

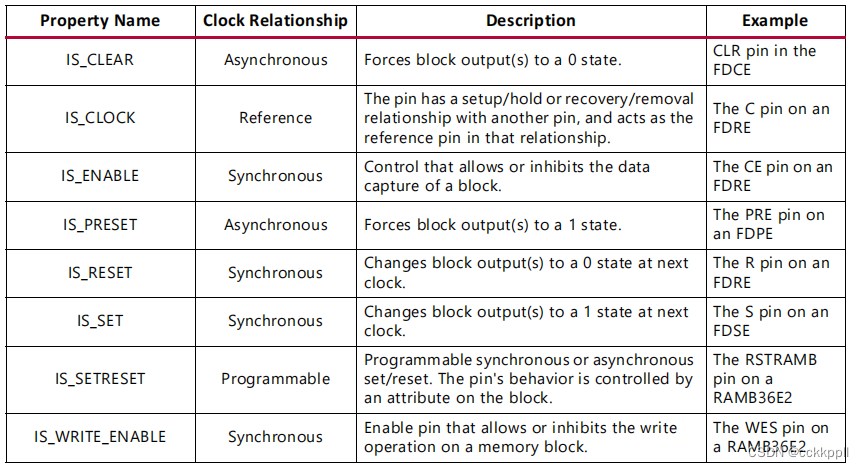

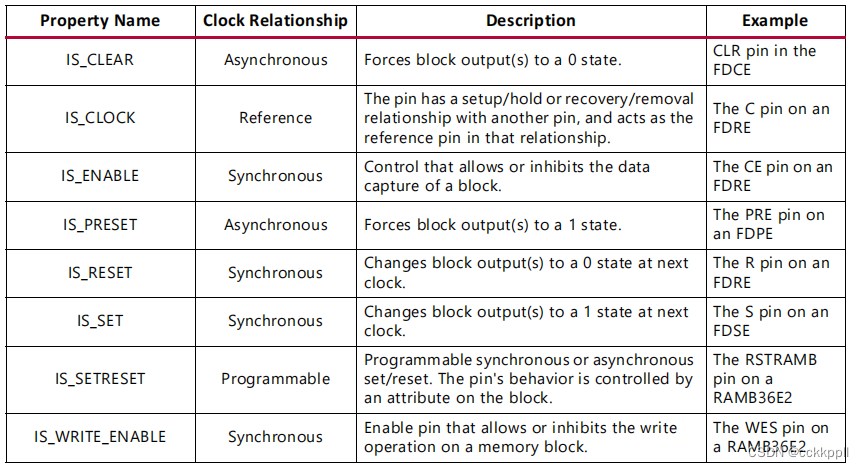

属性

PIN对象包括一组属性,这些属性定义了时钟和

控制引脚。在编写Tcl时,可以使用这些属性按类型筛选引脚列表

脚本,或使用PIN对象。下表列出了这些特性。

除了这些定义端号类型的属性之外,pin上的各种属性

对象包括以下内容:

Property Type Read-only Visible Value

BEL string false true

BUS_DIRECTION enum true true

BUS_NAME string true true

BUS_START int true true

BUS_STOP int true true

BUS_WIDTH int true true

CLASS string true true pin

CLOCK_DEDICATED_ROUTE enum false true

DCI_VALUE int false true

DIRECTION enum true true IN

ESSENTIAL_CLASSIFICATION_VALUE int false true

FB_ACTIVE bool false true

HD.ASSIGNED_PPLOCS string* true true

HD.CLK_SRC string false true

HD.LOC_FIXED bool false false 0

HD.PARTPIN_LOCS string* false true

HD.PARTPIN_RANGE string* false true

HD.PARTPIN_TIEOFF bool false true

HD.TANDEM int false true

HIERARCHICALNAME string true false

top.cpuEngine.dwb_biu.\retry_cntr_reg[0] .C

HOLD_DETOUR int false true

HOLD_SLACK double true true needs timing update***

IS_CLEAR bool true true 0

IS_CLOCK bool true true 1

IS_CONNECTED bool true true 1

IS_ENABLE bool true true 0

IS_INVERTED bool false true 0

IS_LEAF bool true true 1

IS_ORIG_PIN bool true true 0

IS_PRESET bool true true 0

IS_RESET bool true true 0

IS_REUSED bool true true 0

IS_SET bool true true 0

IS_SETRESET bool true true 0

IS_WRITE_ENABLE bool true true 0

LOGIC_VALUE string true true unknown

MARK_DEBUG bool false true

NAME string true true

cpuEngine/dwb_biu/retry_cntr_reg[0]/C

ORIG_PIN_NAME string true true

PARENT_CELL cell true true

cpuEngine/dwb_biu/retry_cntr_reg[0]

REF_NAME string true true FDCE

REF_PIN_NAME string true true C

SETUP_SLACK double true true needs timing update***

TARGET_SITE_PINS string* false true

XLNX_LINE_COL int false false

XLNX_LINE_FILE long false false

The properties of pins can be listed with the following command:

report_property -all [lindex [get_pins] 0]

这篇关于vivado PIN的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!