本文主要是介绍【紫光同创盘古PGX-Nano教程】——(盘古PGX-Nano开发板/PG2L50H_MBG324第十章)SRAM 读写实验例程,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

适用于板卡型号:

紫光同创PG2L50H_MBG324开发平台(盘古PGX-Nano)

一:盘古盘古PGX-Nano开发板简介

PGX-Nano 是一套以紫光同创 FPGA 为核心的开发板,选用紫光同创 logos2 系列 28nm 工艺的 FPGA(PG2L50H_MBG324)。集成下载器芯片,极大的便利 了用户的使用。 板卡搭载一颗容量为 2MB 的 SRAM 用于数据缓存,DAC 芯片用于产生模 拟信号进行测试验证,esp32 模组进行 WIFI、蓝牙透传;预留了丰富的扩展 IO 用于用户验证、测试外接模块电路功能,一组串口进行串行通信;同时为用户提 供基础的硬件电路资源,例如 led 灯、按键、拨码开关等。

PGX-Nano 开 发 板 搭 载 了 一 颗 2Mbit 的 16 位 宽 SRAM , 型 号 为 IS61WV12816DBLL-10TLI。此型号 SRAM 不需要时钟,只需使信号满足相应时序 要求与状态保持时间,即可完成数据的存取操作。

二:实验目的

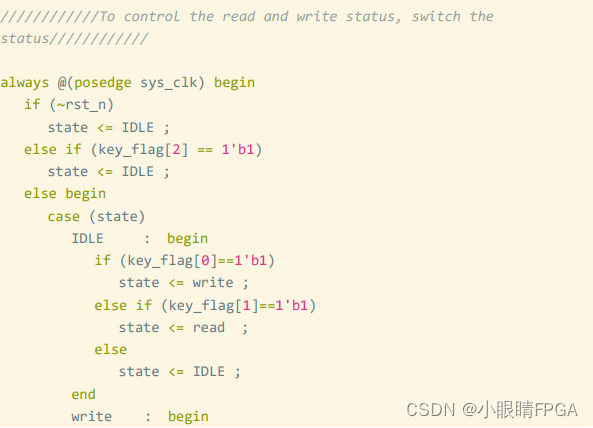

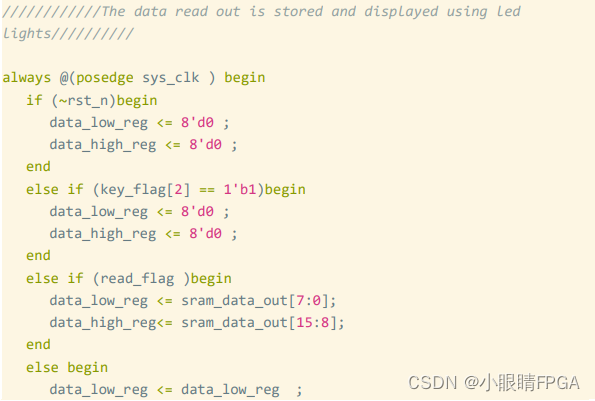

实验在 SRAM 的 17’h00011 地址位置写入 16bit 数据,按下 S0 按键为写入; 再按下 S1 按键读出 17’h00011 地址位置的 16bit 数据,led 灯每隔 0.5s 分别显示 读出数据的高 8bit 与低 8bit。按下 S3 使 LED 恢复为全灭状态。

三:实验原理

此型号 SRAM 共有 5 个控制信号,16 位数据信号,17 位地址信号(开发板 原理图对 SRAM 预留了 19 位地址信号,但最高位与次高位两位地址信号无效)。

关于 IS61WV12816DBLL10TLI 的详细描述请参考 IS61WV12816DBLL 数据手册 (-10 表示访问时间 10ns)。

控制信号共有 5 个,均为低电平有效入下表所示:

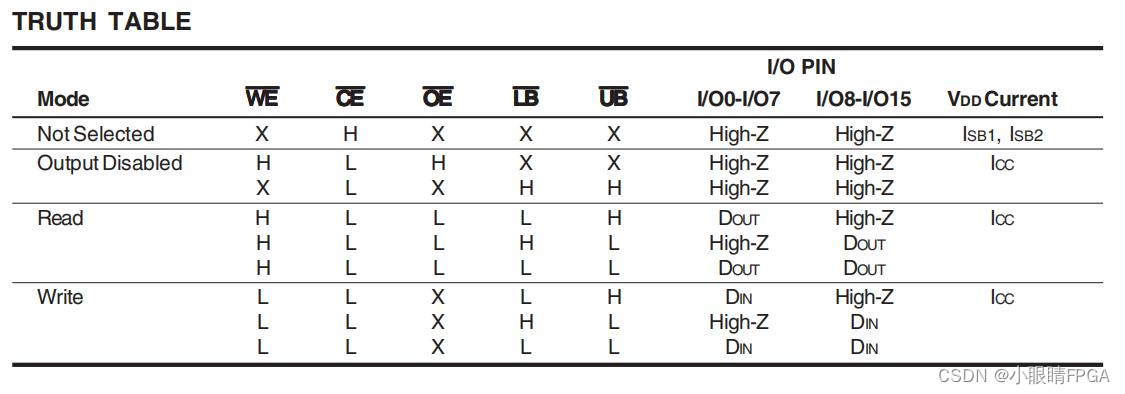

有关控制信号与数据信号的真值表如下图所示:

分析上表所知:

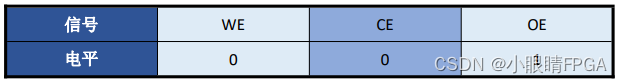

SRAM 写状态对应控制信号电平如下表所示(0 表示低电平,1 表示高电平):

此时,SRAM 将数据存入地址信号对应位置。

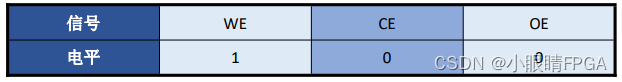

SRAM 读状态对应控制信号电平如下表所示:

此时,SRAM 将地址信号对应位置数据取出。

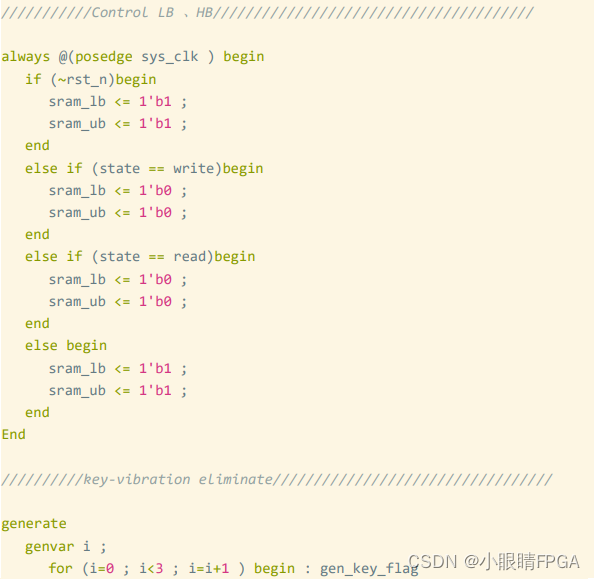

如果需要控制低字节\高字节输出、低字节\高字节输入,则就需要使用 LB、 HB 两个控制信号,LB 为低电平时,数据的低字节可以存入 SRAM,或者地址信 号对应位置数据的低字节可以取出,同理,HB 为低电平时,数据的高字节可以 可以存入 SRAM,或者地址信号对应位置数据的高字节可以取出。

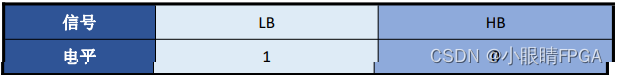

取出\存入 16bit 完整数据时:

仅取出\存入低 8bit 数据时:

仅取出\存入高 8bit 数据时:

在对 SRAM 进行读写操作时,因为此型号 SRAM 不需要时钟,所以相关信号 需要满足指定的时间条件才能对 SRAM 进行读写操作。详细描述请参考 IS61WV12816DBLL 数据手册。

板卡晶振为 50MHz,周期为 20ns,此型号 SRAM 的访问时间时 10ns,因此 通过查阅 SRAM 数据手册可知,控制 SRAM 控制信号在一个时钟周期内保持相应 电平,即可满足时间条件与时序要求;例如在一个时钟周期内将 CE、WE 信号拉 低(LB、HB 依据情况拉高或拉低,OE 信号拉高),即可将数据写入 SRAM 对应 地址位置;在一个时钟周期内将 CE、OE 信号拉低(LB、HB 依据情况拉高或拉低, WE 信号拉高),即可读出 SRAM 对应地址位置的数据。

四:实验源码设计

五:实验现象

按下S0按键在SRAM的17’h00011地址位置写入16bit数据1010_1010_0101_0101 ;再按下 S1 按键读出 17’h00011 地址位置的 16bit 数据 1010_1010_0101_0101 ;led 灯 0.5s 显示 LED0、LED2、LED4、LED6 灯亮、LED1、LED3、LED5、LED7 灯 灭;0.5S 显示 LED0、LED2、LED4、LED6 灯灭、LED1、LED3、LED5、LED7 灯亮。 按下 S3 使 LED 恢复为全灭状态。

这篇关于【紫光同创盘古PGX-Nano教程】——(盘古PGX-Nano开发板/PG2L50H_MBG324第十章)SRAM 读写实验例程的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!