sram专题

国产SRAM存储芯片替代方案

为满足客户对更大更快的SRAM 的普遍需求,伟凌创芯SRAM产品线,容量最高可达64Mb。产品线包括提供256Kb~64Mb不同容量的器件,为传统的并行SRAM产品提供成本更低的替代方案,并在SRAM存储器中包含可选的电池备份切换电路,以便在断电时保留数据。 EMI串行SRAM器件采用成本较低的8引脚封装,并采用高速SPI/SQI通信总线,只需要4-6 个MCU I/O 引脚即可轻松集成。这减少

STM32必知必会之启动文件的选择、Flash、SRAM

一、STM32系列命名规则 STM32 F 103 C 6 T 7 xxx 1 2 3 4 5 6 7 8 第1部分:产品系列名,固定为STM32 第2部分:产品类型;F表示这是Flash产品,目前没有其它选项 第3部分:产品子系列;103表示增强型产品,101表示基本型产品105表示集成一个全速USB 2.0 Host/Device/OTG接口

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR*(一篇文章就懂)

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR* 内存 内存(Memory)指的是内存存储器,又称为主存,是CPU用来直接寻址和存储的空间,它相当于一座桥梁,用以负责诸如硬盘、主板、显卡等硬件上的数据与处理器之间数据交换处理,我们可以把内存看作数据缓存区,一个高速的缓存区。内存之所以称为内存,是相对于硬盘这些外存而言,我们要用的软件数据都安装存放在外存上,但是当我

【紫光同创盘古PGX-Nano教程】——(盘古PGX-Nano开发板/PG2L50H_MBG324第十章)SRAM 读写实验例程

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com) 适用于板卡型号: 紫光同创PG2L50H_MBG324开发平台(盘古PGX-Nano) 一:盘古盘古PGX-Nano开发板简介 PGX-Nano 是一套以紫光同创 FPGA 为核心的开发板,选用紫光同创 logos2 系列 28nm 工艺的 FPGA(PG2L50

SRAM和Flash的区别

什么是SRAM SRAM的特点 什么是Flash Flash存储器的特点 SRAM和Flash的区别 什么是SRAM SRAM:全称为Static Random Access Memory,即静态随机存取存储器,是一种常见的计算机内存类型。 SRAM电路通常由存储矩阵、地址译码器和读/写控制电路三部分组成,存储矩阵

【IC前端虚拟项目】axi ddr/sram验证组件思路与编写

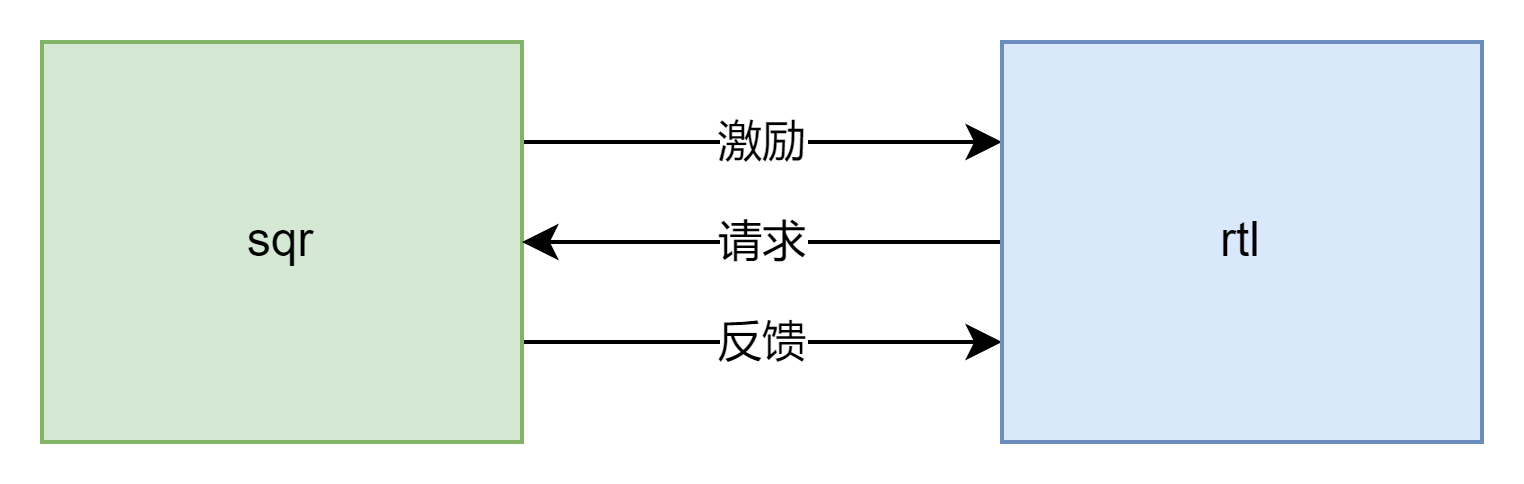

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 在完成了所有的utils包括apb_utils之后,就要进行验证环境的整体搭建,因此我们再把验证环境拿出来看一下: 按照由底至顶层的思路,接下主要有五大部分需要我们完成:ram_model、reference_model、env、base_test和harness,这一篇从最难的ram_model开始说起。这

TL2837x-EasyEVM开发板 处理器、NOR FLASH、SRAM

前言 TL2837x-EasyEVM是一款基于广州创龙SOM-TL2837x核心板所设计的高端单/双核浮点开发板,它为用户提供了SOM-TL2837x核心板的测试平台,用于快速评估SOM-TL2837x核心板的整体性能。 图 1 TL2837x-EasyEVM正面图 处理器 TI TMS320F2837x单/双核具有200MHz的高速处理能力,双核拥有多达12路的PWM输

S32K144之FlexMem,FlexNVM,FlexRAM,System RAM, SRAM 区别与联系

参考手册中常常见到有关memory的关键字,如FlexMem,FlexNVM,FlexRAM,System RAM, SRAM,那么它们到底是什么意思呢?有什么区别和联系? 参考资料 [1]S32K144 参考手册 [2]FlexNVM Memory应用笔记:AN12003 [3]EEPROM Functionality应用笔记:AN11983 1.汇总 2.简

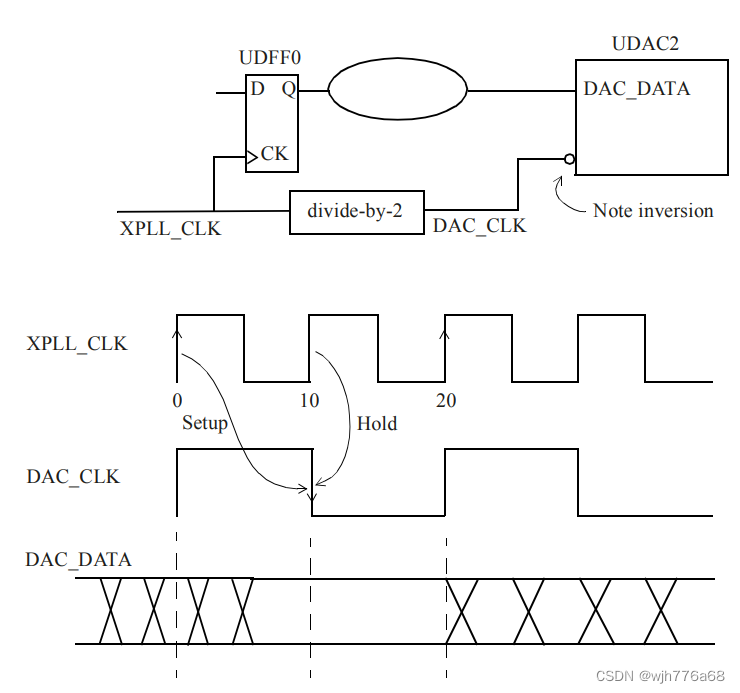

【STA】SRAM / DDR SDRAM 接口时序约束学习记录

1. SRAM接口 相比于DDR SDRAM,SRAM接口数据与控制信号共享同一时钟。在用户逻辑(这里记作DUA(Design Under Analysis))将数据写到SRAM中去的写周期中,数据和地址从DUA传送到SRAM中,并都在有效时钟沿处被锁存在SRAM中。在DUA从SRAM中取数据的读周期中,地址信号从DUA传送到SRAM中去,数据信号由SRAM输出给DUA。 DUA与SRA

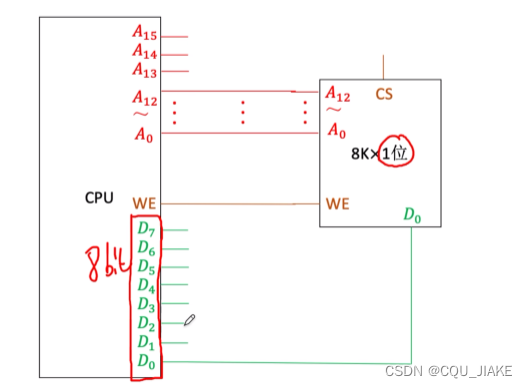

2.15SRAM,DRAM,ROM,主存与CPU连接

MDR取出数据,然后通过数据总线传递给CPU, 地址总线传递信号给到MAR 就是说片选线是用来选择操作哪个芯片 8*8位 第一个代表存储单元的数量,第二个代表存储字长 有几个存储单元,就对应多少位地址以及多少的地址线 存储字长决定数据线的数量 字节寻址,1B是一字节8BIT,总容量=个数*大小,寻址的时候变的是大小,因此变的是个数 充电的过程是写的过程,放电

DRAM,SRAM,SDRAM,DDR SDRAM区别!

http://blog.sina.com.cn/s/blog_5146fb2d0100hsar.html 问题1:什么是DRAM、SRAM、SDRAM? 答:名词解释如下 DRAM--------动态随即存取器,需要不断的刷新,才能保存数据,而且是行列地址复用的,许多都有页模式 SRAM--------静态的随机存储器,加电情况下,不需要刷新,数据不会丢失,而且一般不是行列地址复用的 SDRAM

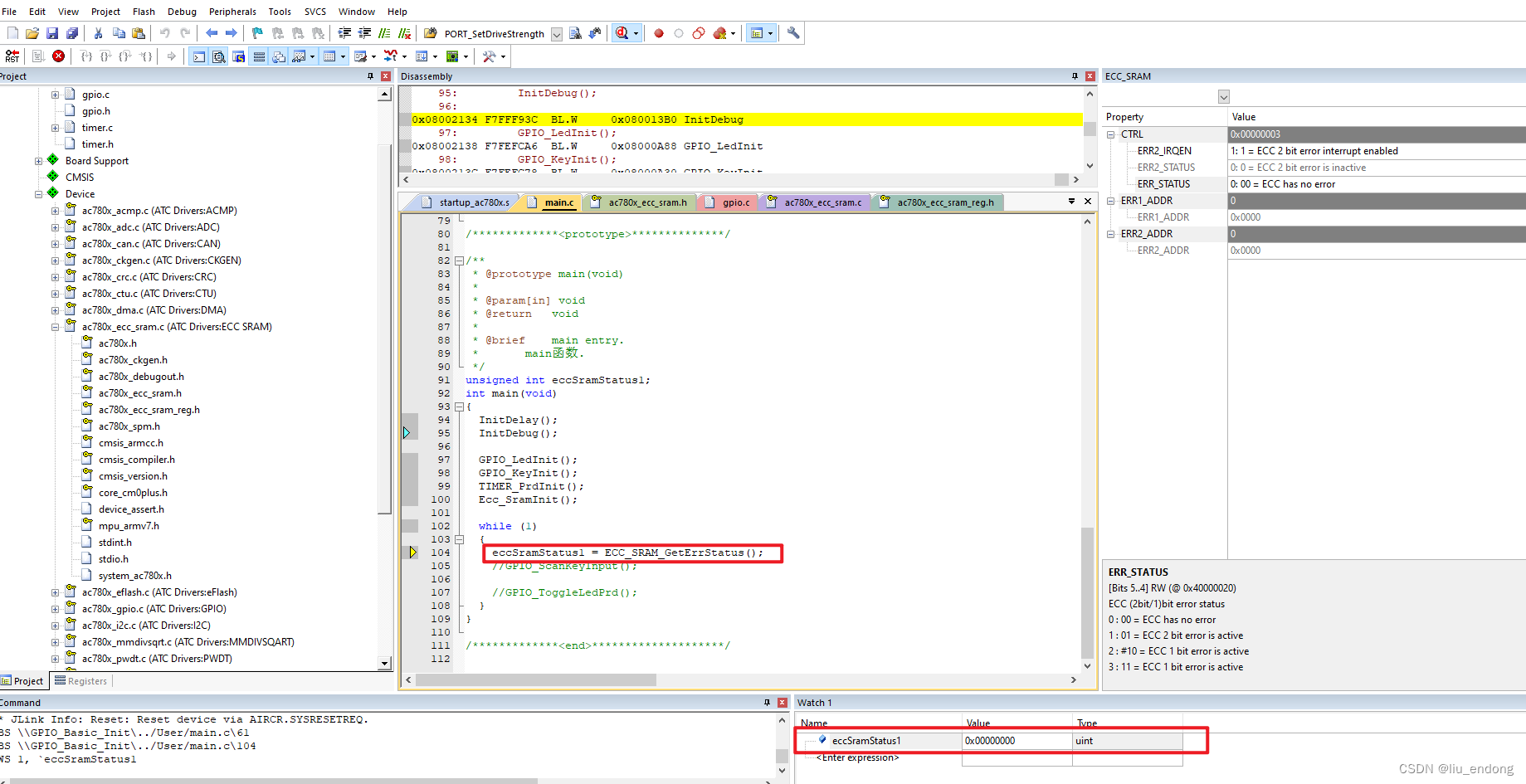

杰发科技AC7801——SRAM 错误检测纠正

0.概述 7801暂时无错误注入,无法直接进中断看错误情况,具体效果后续看7840的带错误注入的测试情况。 1.简介 2.特性 3.功能 4.调试 可以看到在库文件里面有ecc_sram的库。 在官方GPIO代码里面写了点测试代码 成功打开2bit中断 因为没有错误注入,没法直接测试,回头瞅瞅7840加了错误注入的测试结果 调试看到状态值始终为0。回头找个有问题的芯片

SRAM、SDRAM、FLASH三者的区别

Sram的好处是接口简单,速度快容易操作,用资源也比较少;sdram的最大好处是容量大,当然速度也比较快,但是接口复杂些,也耗逻辑资源多些;flash是非易失性存储器,速度慢。 目前,相同容量的SRAM价格是SDRAM的8倍左右,面积则将近大4倍,所以SRAM常用于快速存储的较低容量的RAM需求,比如Cache(缓存),比如CPU内部的L1 Cache和主板上的L2 Cache,一般只有几百K。

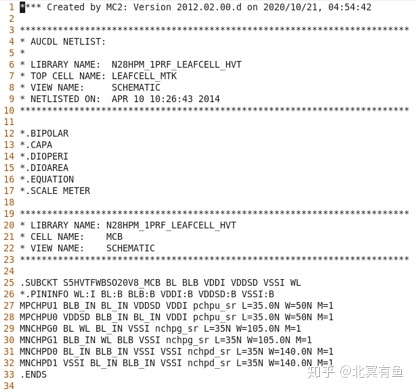

双稳态电路的两个稳定状态是什么_一张SRAM电路结构图引发的思考

直接上图 这个是一张经典的sram电路的6管存储单元结构 sram是什么? sram全称:(Static Random Access Memory)静态随机存取存储器 从图中可以看出,这个是一种由交叉耦合的反相器构成的双稳态结构 特点:读写速度快,断电数据消失 这张SRAM的电路结构图引起了我的兴趣,于是我又玩起了Memory Compiler 北冥有鱼:Memory Compiler所

存储器(ROM、SDRAM、RAM、DRAM、SRAM、FLASH)的区别

个人学习,侵删 ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写。ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是在掉电之后就丢失数据,典型的RAM就是计算机的内存。 RAM有两大类,一种称为静态RAM(Static RAM/SRAM),另一种称为动态RAM(Dynamic RAM/DR

STM32Cube高效开发教程<基础篇>(十七)----FSMC连接外部SRAM

声明:本人水平有限,博客可能存在部分错误的地方,请广大读者谅解并向本人反馈错误。 本专栏博客参考《STM32Cube高效开发教程(基础篇)》,有意向的读者可以购买正版书籍辅助学习,本书籍由王维波老师、鄢志丹老师、王钊老师倾力打造,书籍内容干货满满。 一、 FSMC连接外部SRAM的原理 1.1 FSMC控制区域的划分 FSMC控制器的存储区分为4个区(Bank),每个区256

推荐可兼容IS61WV12816DBLL-10BLI的低功耗SRAM EMI502NL16LM-55I

SRAM是随机存取存储器的一种。这种存储器只要保持通电,里面储存的数据就可以恒常保持。SRAM不需要刷新电路即能保存它内部存储的数据。 介绍一款可替代IS61WV12816DBLL-10BLI高速低功耗异步SRAM芯片EMI502NL16LM-55I 推荐一款国产SRAM芯片,型号EMI502NL16LM-55I产品,该系列由EMI先进的全CMOS工艺技术制造。位宽为128Kx 16的2Mbi

DRAM、SDRAM和SRAM的区别

特点简介: SRAM : 静态 RAM , 不用刷新, 速度可以非常快, 像 CPU 内部的 cache , 都是静态 RAM , 缺点是一个内存单元需要的晶体管数量多,因而价格昂贵,容量不大。 DRAM : 动态 RAM ,需要刷新,容量大。 SDRAM :同步动态 RAM ,需要刷新,速度较快,容量大。 DDR SDRAM : 双通道同

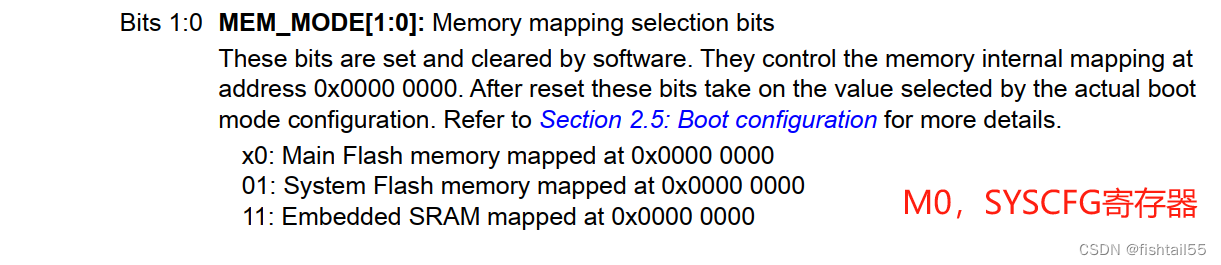

【STM32】程序在SRAM中运行

程序在RAM中运行 1、配置内存分配。 2、修改跳转文件 FUNC void Setup(void) { SP = _RDWORD(0x20000000); PC = _RDWORD(0x20000004); } LOAD RAM\Obj\Project.axf INCREMENTAL Setup(); 3、修改下载ROM地址和RAM地址; 中断向量表映射 中断向量表映射到SR

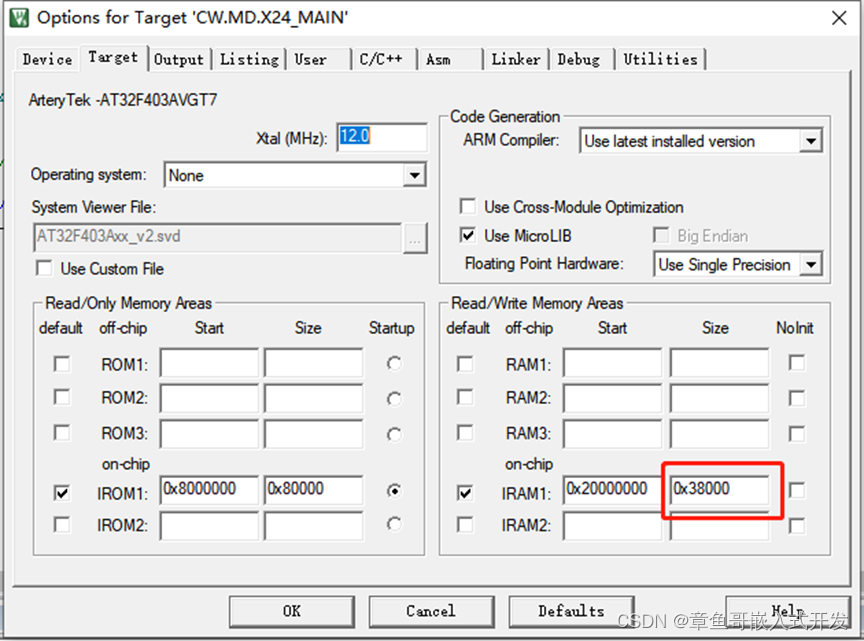

AT32F403如何扩大SRAM

配置方法 使用雅特力的ICP 进行配置(可在官网下载) (1)当连接上芯片后,点击设备操作->选择字节 (2)选择224KB SRAM (3)然后点击应用到设备,(可以点击从设备加载,来看当前的配置) (4)打开keil5魔术棒图标 ,将Target中的IRAM1第二个选项从0x10000改为0x3800。(0x10000/1024=64kb,0x38000/1024=224kb)

【计算机组成体系结构】SRAM和DRAM

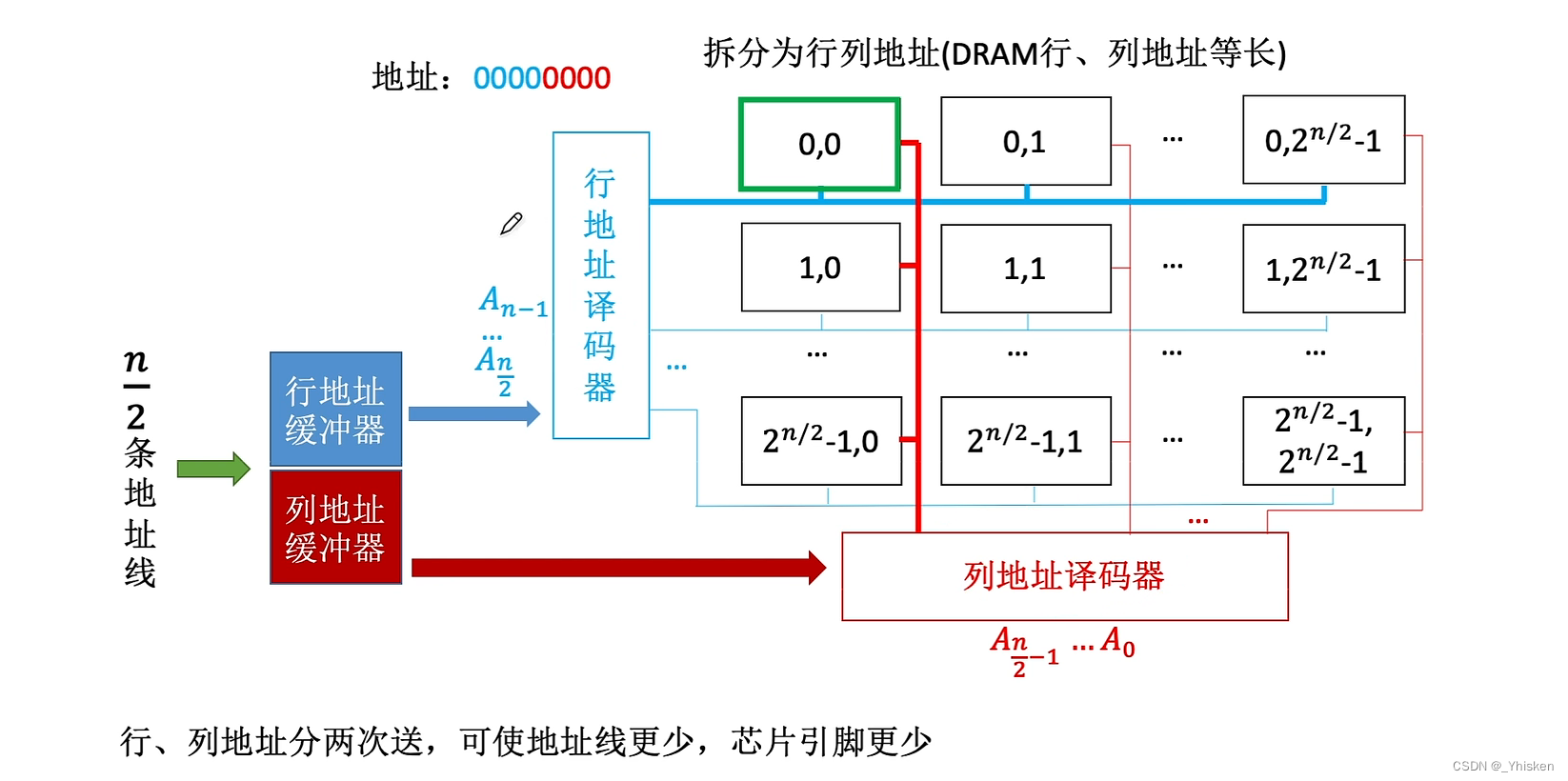

RAM — Random Access Memory 随机访问存储器 —指定某一存储单元地址的时候,存储单元的读取速度并不会因为存储单元的物理位置改变 SRAM即为 Static RAM 静态随机访问存储器 — 用于主存DRAM即为 Dynamic RAM 动态随机访问存储器 — 用于Cache 一、SRAM和DRAM的特性差异 DRAM采用栅极电容存储二进制0/1,线端是否有

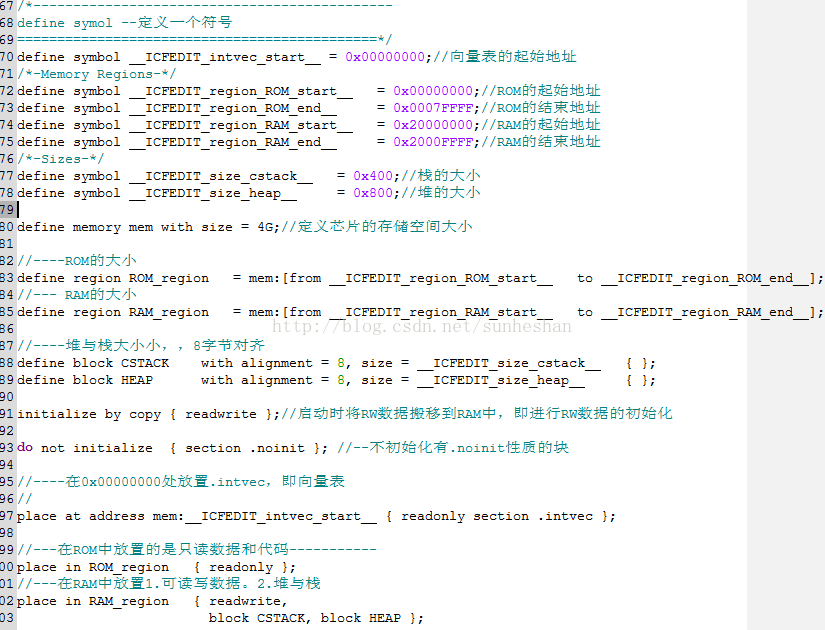

外加SRAM 配置ICF文件

每个芯片开发商都会针对每款芯片来编写一个.icf文件就是传说中的链接文件。对于基本的应用,这个.icf文件足以满足你的工程需要。但有时也会需要改动,比如当你的项目要添加外部RAM时就要修改一下icf。 1、Icf到底干了啥呢? 定义了芯片存储空间的大小。定义ROM的大小和起始、结束地址。定义RAM的大小和起始、结束地址。 当然这些都是最基本的,你也可以设置以下的东西来匹配你的具体项目

AMD或将3D堆叠SRAM和DRAM用于其CPU和GPU

十次方消息,AMD高级副总裁Norrod最近在Rice Oil and Gas HPC会议上发表讲话,并透露公司正在进行自己的3D堆叠技术,角度与英特尔的略有不同。 此前AMD已经将HBM2内存堆叠在其GPU核心旁边,这意味着它与处理器位于同一个封装中,但该公司计划在不久的将来转向真正的3D堆叠。Norrod解释说,AMD正致力于在CPU和GPU之上直接堆叠SRAM和DRAM内

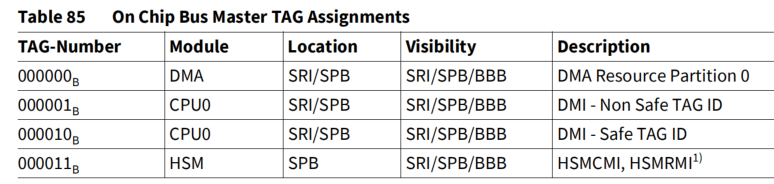

英飞凌TC3xx的LMU SRAM保护机制(一)

目录 1.基本概述 2.理解Master Tag ID 3.LMU memory保护使能 4.测试结果分析 5.小结 1.基本概述 在英飞凌TC3xx中,每个CPU除了有自己的DLMU外,在SRI总线还挂着几块SRAM,这几块SRAM由LMU(Local Memory Unit)进行权限控制。 RAM的具体地址(上述9H

RT-Thread memheap 开启多块 SRAM的方法

验证环境 NUCLEO-L476RG 开发板,板载 STM32L476RGT6(96K SARM1 + 32K SRAM2) Win10 64 位 Keil MDK 5.36 RT-Thread 5.0.1 版本(2023-05-28 master 主线) 功能描述 最近在研究 RT-Thread 内存的管理,熟悉了一下 memheap 的功能实现,并且了解到, memheap