本文主要是介绍vivado HW_BITSTREAM、HW_CFGMEM,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

HW_比特流

描述

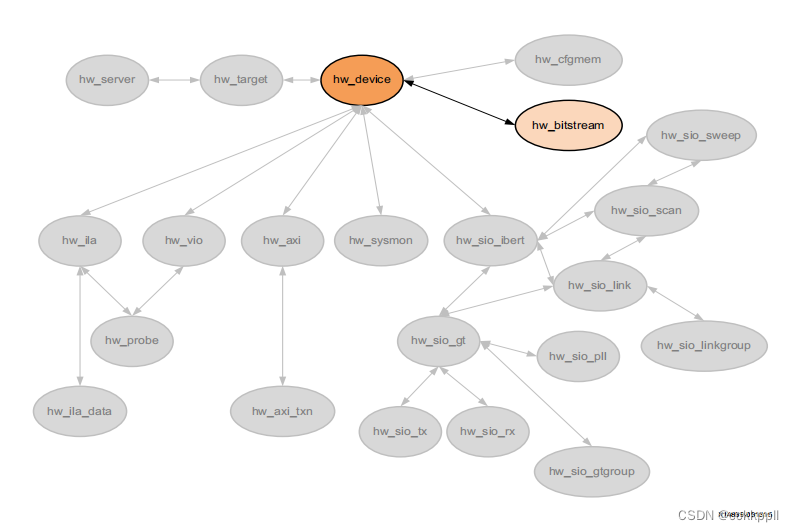

从比特流文件创建的硬件比特流对象hw_bitstream,用于关联

在Vivado的硬件管理器功能中使用硬件设备对象hw_device

设计套件。

比特流文件是从具有write_bitstream的放置和路由设计创建的

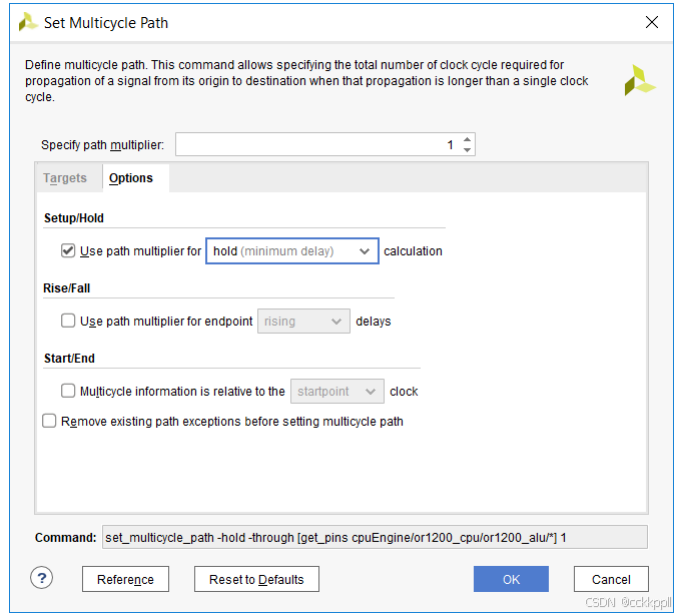

命令硬件位流对象是使用

create_hw_bitstream命令,或在硬件设备

用program_hw_device命令编程。

hw_bitstream对象通过

设备上的PROGRAM.HW_BITSTREAM属性。此属性由自动设置

create_hw_bitstream命令。PROGRAM.FILE属性包括的文件路径

指定的位流文件。

相关对象

hw_bitstream对象通过

PROGRAM.BITSTREAM属性。可以使用查询hw_bitstream对象

get_property命令返回特性中的对象,如下所示:

get_property PROGRAM.HW_BITSTREAM[current_HW_device]

属性

可以使用report_property命令报告指定给的特性

硬件位流对象。请参阅Vivado Design Suite Tcl命令参考指南

(UG835)[参考文献13]了解更多信息。hw_bitstream对象的特定属性

包括以下内容和示例值:

命令返回在上的PROGRAM.HW_BITSTREAM属性中定义的对象

Vivado逻辑分析器中的hw_device。可以将以下命令复制并粘贴到

Vivado Design Suite Tcl外壳或Tcl控制台:

描述

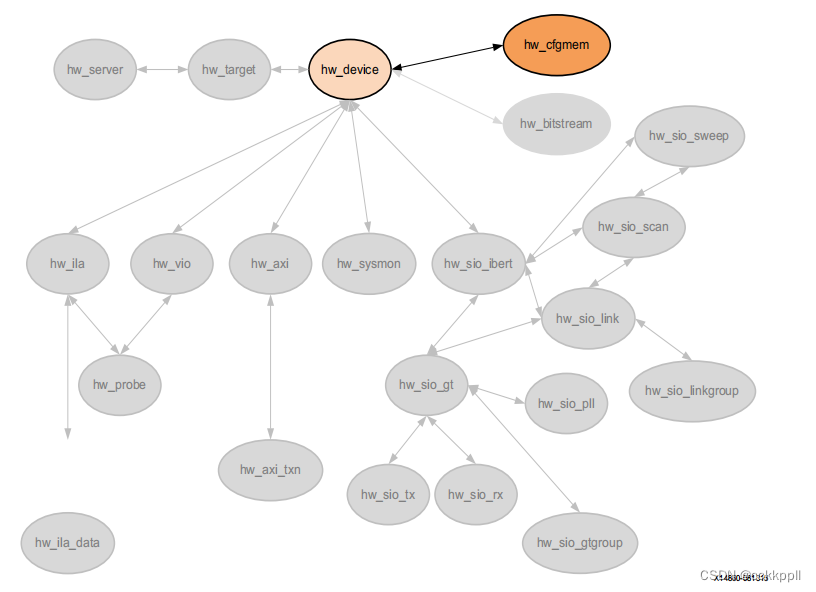

Xilinx FPGA是通过加载特定于设计的配置数据来配置的,其形式为

比特流文件)存储到hw_device的内部存储器中。hw_cfgmem定义了一个闪存

用于在硬件管理器中配置和引导Xilinx FPGA的存储设备

Vivado设计套件的特色。

hw_cfgmem对象是使用create_hw_cfgmems命令创建的。一旦

创建hw_cfgmem对象,并将配置与hw_device相关联

可以使用

program_hw_cfgmem命令。

相关对象

设备对象上的PROGRAM.HW_CFGMEM属性。使用hw_cfgmem

对象,使用get_property命令从hw_device获取对象:

get_property PROGRAM.HW_CFGMEM[current_HW_device]

属性

可以使用report_property命令报告指定给的特性

hw_cfgmem对象。请参阅Vivado Design Suite Tcl命令参考指南(UG835)

[参考文献13]了解更多信息。hw_cfgmem对象的属性包括

以下,具有示例值:

当硬件管理器

功能已打开:

这篇关于vivado HW_BITSTREAM、HW_CFGMEM的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!