本文主要是介绍【时序约束】如何确定输入输出信号的时序约束值,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

确定输入输出信号的时序约束值是 FPGA 设计中的一个重要步骤,它涉及到对信号传输时间和 FPGA 内部时序要求的准确理解。以下是确定时序约束值的一些关键步骤:

1. 理解信号特性

- 输入信号:考虑输入信号的来源、传输距离、走线长度以及是否经过任何缓冲或驱动器。

- 输出信号:考虑信号的负载、走线长度、以及是否需要满足特定的电气规范。

2. 分析时序要求

- 建立时间(Setup Time):数据在时钟边沿到来之前需要保持稳定的最小时间。

- 保持时间(Hold Time):数据在时钟边沿到来之后需要保持稳定的最小时间。

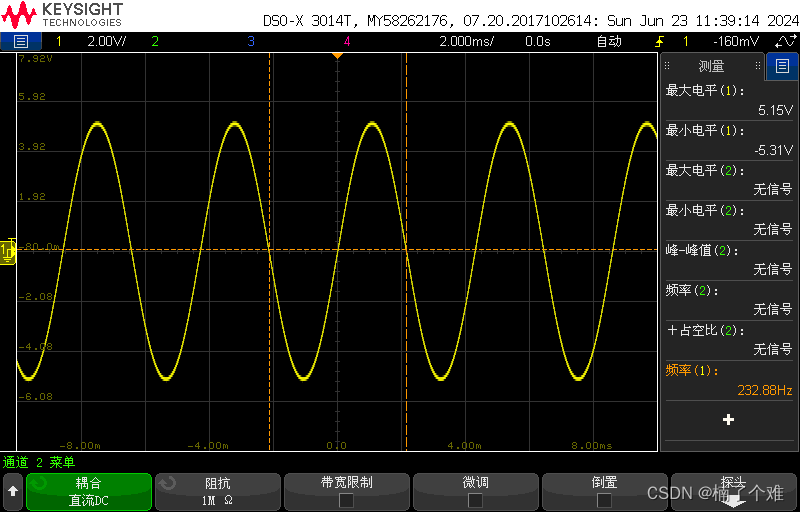

- 时钟周期(Clock Period):时钟信号的周期,决定了设计中最快的时钟频率。

3. 考虑外部接口

- 接口标准:如 LVCMOS、LVDS、HSTL 等,每个标准都有其特定的时序要求。

- 协议规范:例如,接口是否遵循某种通信协议,如 PCIe、Ethernet、AMBA 等,这些协议可能有自己的时序规范。

4. 使用数据手册

- FPGA 数据手册:提供 FPGA 芯片的时序参数,如输入输出延迟、时钟到输出(C2O)延迟等。

- 外部器件数据手册:如果信号与外部器件接口,需要参考这些器件的数据手册来确定时序要求。

5. 进行时序分析

- 静态时序分析(STA):使用时序分析工具来预测信号在不同条件下的时序表现。

- 仿真:通过仿真来验证信号在实际工作条件下的行为。

6. 考虑最坏情况

- 温度:高温可能会增加延迟。

- 电压:电压变化会影响信号的传播速度。

- 工艺变异:半导体制造过程中的变异可能导致性能差异。

7. 与 PCB 设计师合作

- 走线长度:与 PCB 设计师合作,确保走线长度符合时序要求。

- 走线层:考虑信号走线在 PCB 上的层级,不同层可能有不同的电气特性。

8. 使用经验值和历史数据

- 类似项目:参考类似项目的设计和时序约束。

- 经验公式:在某些情况下,可能有一些经验公式可以帮助估计延迟。

9. 留出余量

- 保守设计:在确定时序约束时,留出一定的余量以应对不确定性。

10. 验证和迭代

- 验证:在设计的不同阶段进行时序验证,确保约束满足要求。

- 迭代:根据验证结果调整约束,并重新进行验证。

11. 工具和自动化

- 自动化工具:使用 Vivado 等工具提供的自动化约束生成功能。

- 脚本:编写脚本以自动化约束的生成和验证过程。

确定时序约束值是一个需要综合考虑多种因素的过程,需要设计师具备对 FPGA 架构、电路设计、信号完整性和时序分析的深入理解。在实际操作中,通常需要结合工具、经验和设计目标来确定这些值。

这篇关于【时序约束】如何确定输入输出信号的时序约束值的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[FPGA][基础模块]跨时钟域传播脉冲信号](/front/images/it_default.gif)