本文主要是介绍xilinx mii to rmii核使用,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

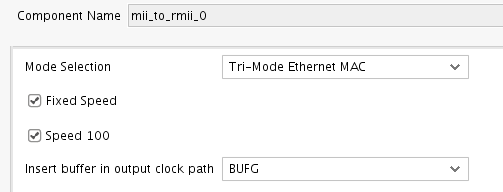

在使用AXI 1G/2.5G Ethernet Subsystem若要使用rmii接口的phy则需要使用xilinx mii to rmii的ip核,如下图:

需要说明:

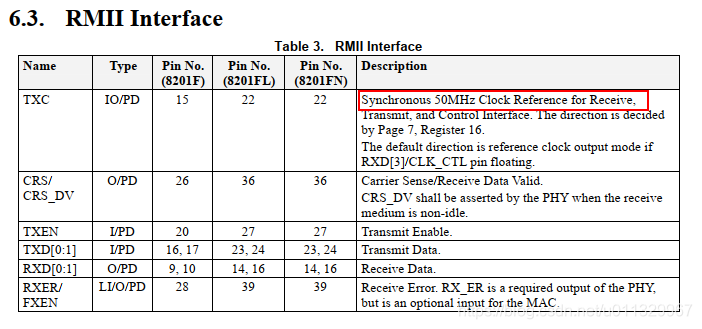

rmii接口的时钟系统和mii接口并不一样,rmii接口是系统同步,收发端使用同一个时钟源(ip核从ref_clk输入);

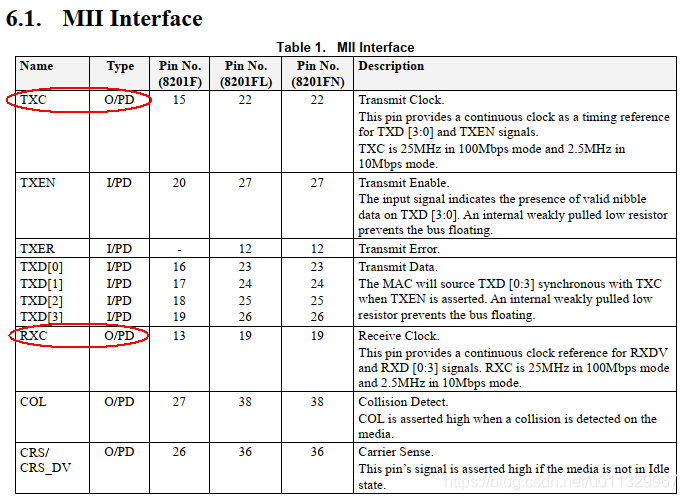

而mii是源同步系统,收发端都有对应的clk信号。(虽然mii有独立的收发时钟但PHY的rxclk\txclk都是输出,所以并不是完全源同步,需要注意PHY的tx/rx定义是对应与mac来说的)

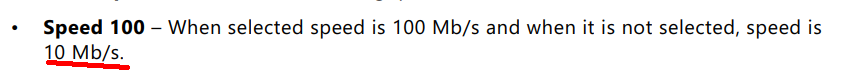

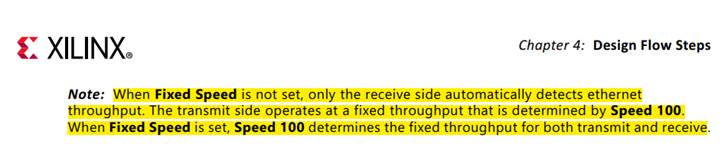

1、这个核并不是自适应的10M/100M,它的速度是固定的(默认我们需要选择:Speed 100M/实际工作环境不太可能遇到10M的情况):

一开始没有勾选导致数据发送失败,我用板卡和PC通信,PC端无法抓取到子卡的网络报文,使用ila监测时序发现发送周期不正确,正常31个时钟周期的网络报文前导码(7个0x55,一个0xd5)竟然用了331个周期:(起始点为4096)

手册给出来的时序:

备注:添加ila找不到时钟源时记得可以选择时钟域类型:

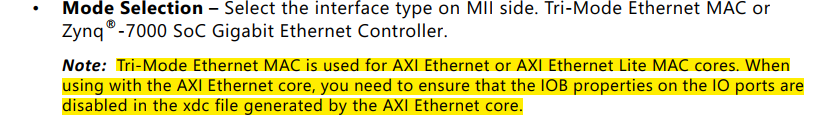

2、需要对rmii引脚添加iob xdc约束,因为ip核并没有对引脚做约束,手册上已说明:

3、需要禁用Ethernet Subsystem ip核的管脚xdc约束:

手册上没有给出具体的做法:我是直接disable掉了ip核生成的一个xdc(因为它是只读属性我无法更改),更改后成功生成了bit,测试也没有问题。

参考:

pg146-mii-to-rmii.pdf

https://www.xilinx.com/support/documentation/ip_documentation/mii_to_rmii/v2_0/pg146-mii-to-rmii.pdf

±15kV ESD Protected MII/RMII 10/100 Ethernet Transceiver

https://docs.rs-online.com/58cd/0900766b80d9640b.pdf

这篇关于xilinx mii to rmii核使用的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!