rmii专题

xilinx mii to rmii核使用

在使用AXI 1G/2.5G Ethernet Subsystem若要使用rmii接口的phy则需要使用xilinx mii to rmii的ip核,如下图: 需要说明: rmii接口的时钟系统和mii接口并不一样,rmii接口是系统同步,收发端使用同一个时钟源(ip核从ref_clk输入); 而mii是源同步系统,收发端都有对应的clk信号。(虽然mii有独立的收发时钟但PHY

SOC内部集成网络MAC外设+ PHY网络芯片方案:MII/RMII 接口与 MDIO 接口

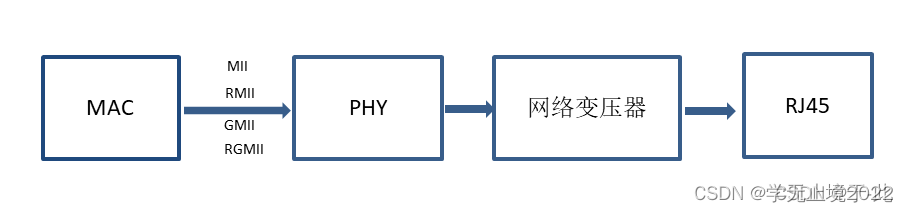

一. 简介 本文来了解一下常用的一种网络硬件方案:SOC内部集成网络MAC外设+ PHY网络芯片方案。 其中涉及的 MII接口,RMII接口(MII接口与RMII接口二选一),MDIO接口,RJ45。 二. MII/RMII 接口,MDIO 接口 ,RJ45 本文简单了解一下内部带网络MAC的 SOC+外接一个PHY芯片,这种网络硬件方案涉及到的接口连接。 内部 MA

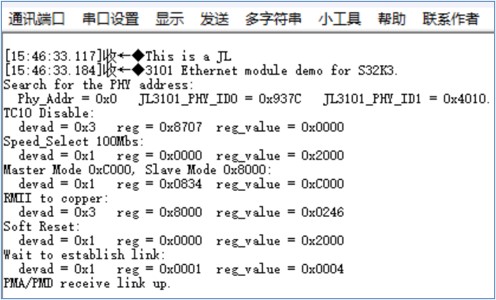

【S32K 进阶之旅】 NXP S32K3 以太网 RMII 接口调试(2)

前言 前文介绍了 NXP S32K3 以太网 RMII 接口调试的开发环境搭建,下面开始详解软件调试步骤。没看过第一节的小伙伴请移步《【S32K 进阶之旅】 NXP S32K3 以太网 RMII 接口调试(1)》,话不多说我们直接进入正题。 lwip Stack 介绍 TCP/IP Stack 是 TCP/IP 协议套件的轻量级实现,而实现 lwIP TCP/

MII、RMII、GMII、RGMII接口是什么 用在什么地方

mac芯片和phy芯片之间的通信接口 MII(Media Independent interface):媒体独立接口,也叫介质无关接口。它是MAC和PHY之间的通信接口。MII数据接口有2根控制线和16根数据线组成。当CLK信号为25MHz(对应100Mb/s)或2.5MHz(对应10Mb/s)。 RMII(Reduced Media Independent Interface):独立于介质接

MII、RMII、 SMII、GMII、RGMII、SMI接口介绍

简要介绍 这几种接口是我们常说的网卡中应用的接口,应用于MAC和PHY直接的通信接口,符合IEEE定义的标准,不同厂家生产的网卡也都是按照标准生产的,所以我们能直接换网卡使用。 接口说明 SMI接口是MAC对PHY的控制接口,叫做站管理接口,总共两根线,一根时钟线,一根数据线。 MII接口是MAC与PHY之间的数据通信接口,叫做介质独立接口。 而RMII、 SMII是对MII的简化,缩减了