本文主要是介绍ARM IHI0069F GIC architecture specification (7),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

3.1 GIC逻辑组件

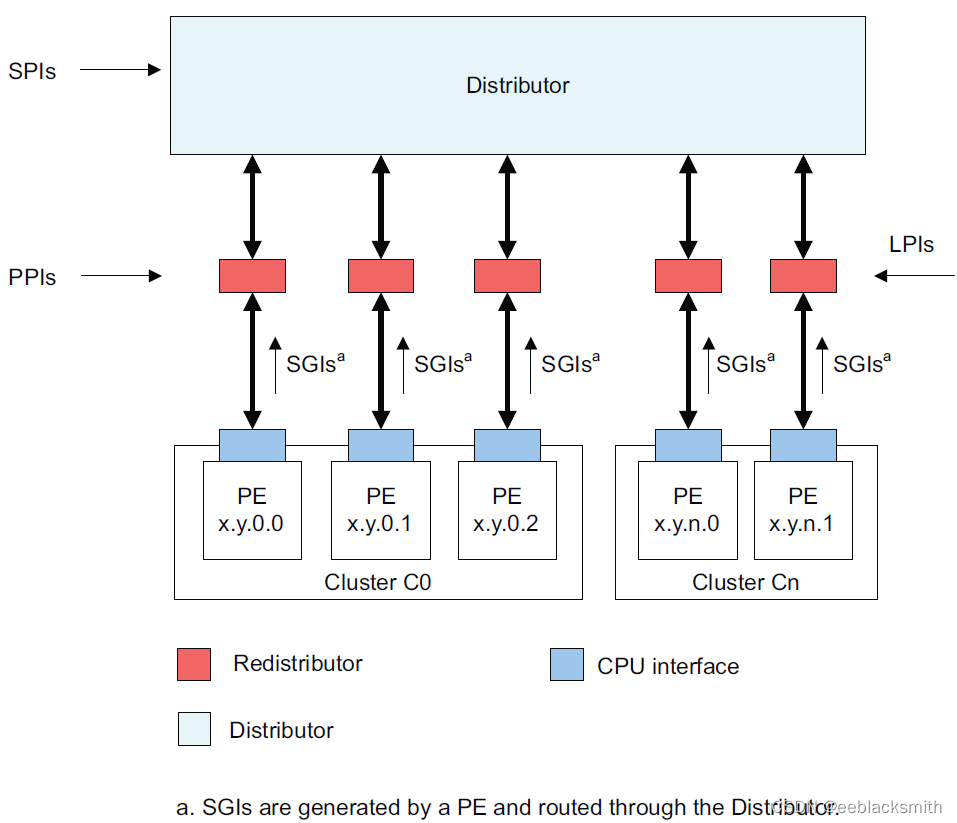

GICv3体系结构由一组逻辑组件组成:

•Distributor。

•每个受支持的PE都有一个Redistributor。

•支持的每个PE都有一个CPU interface。

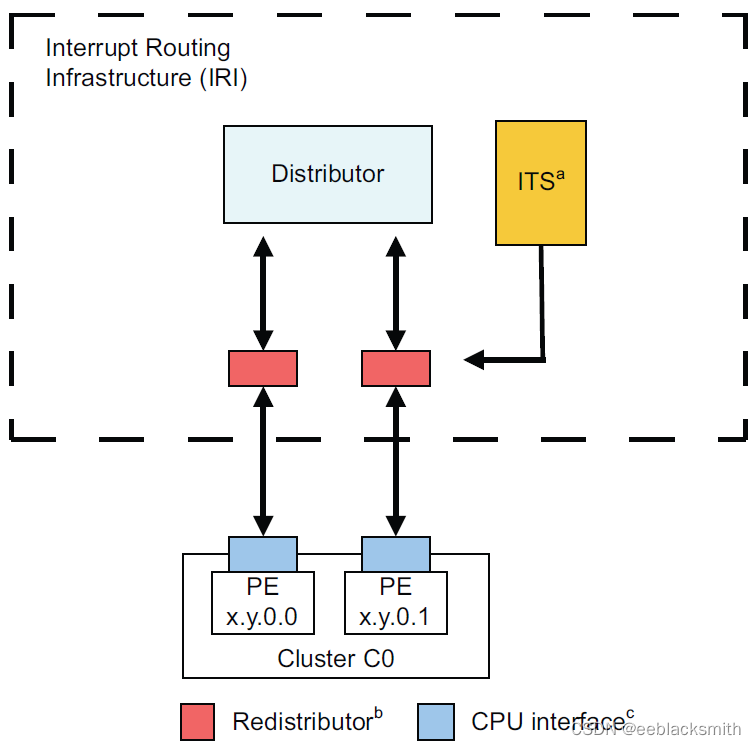

•中断翻译服务组件(ITS),支持将事件翻译为LPI。

Distributor, Redistributor和ITS统称为IRI。

a.ITS是可选的,IRI中可能有多个ITS。

b.每个PE有一个Redistributor。

c.每个PE有一个CPU interface。

CPU interface处理所有实现的异常级别的物理中断:

•可选择通过ITS将转换为LPI的中断路由至Redistributor和CPU interface

•PPI直接从源路由到本地Redistributor。

•SPI从源通过分发服务器路由到目标Redistributor和相关的CPU interface

•SGI由软件通过CPU interface和Redistributor生成。然后通过Distributor路由到到一个或多个目标Redistributor和相关联的CPU interface。

在GICv3中,ITS是一个可选组件,可将事件转换为物理LPI。该体系结构还支持不需要使用ITS的直接LPI。如果支持LPI,可以通过下面两个方式中的任意一个来实现:

•通过访问Redistributers中的寄存器来支持直接LPI。

•LPI支持由ITS提供。

一个实现必须只支持其中一种方法。

在GICv4中,必须包含至少一个ITS,以提供对虚拟LPI直接注入的支持。

ITS和Redistributor之间的通信机制由具体实现定义的。

CPU interface 和 Redistributor 之间的通信机制由具体实现定义的。

以下列表更详细地描述了上面第一张图所示的组件:

Distributor

Distributor执行中断优先级排序,并将SPIs和SGI分配给PE的Redistributor和CPU interface。

GICD_CTLR为以下各项提供全局设置:

•启用亲和路由。

•禁用安全性。

•启用安全和非安全组1中断。

•启用组0中断。

对于SPI,分发服务器为以下各项提供编程接口:

•启用或禁用SPI。

•设置每个SPI的优先级。

•每个SPI的路由信息。

•将每个SPI设置为电平敏感型或边缘触发型。

•生成基于消息的SPI。

•将每个SPI分配给一个中断组。

•控制SPI的挂起状态和活动状态。

分发服务器寄存器由GICD_前缀标识。

有关详细信息,请参阅第2章中断的分布和路由。

ITS

ITS是GICv3体系结构中的一种可选硬件机制,用于将LPI路由到适当的Redistributor。软件使用命令队列来配置ITS。存储器中与ITS相关联的表结构将与设备相关联的EventID转换为PE的未决INTID。

ITS在GICv4中不是可选的,并且所有GICv4实现必须至少包括一个ITS。

有关更多信息,请参阅第5-85页的中断翻译服务。

Redistributor Redistributr是IRI中连接到PE的CPU interface的部分

Redistributor使用内存中的数据结构来保存所有物理LPI的控制、优先级和挂起信息。Redistributor中的两个寄存器指向以下数据结构:

•GICR_PROPBASER。

•GICR_PENDBASER。

在GICv4中,Redistributor还包括用于处理虚拟LPI的寄存器,这些虚拟LPI由ITS转发到Redistributer并直接转发到VM,而不涉及系统管理程序。这被称为将虚拟中断直接注入到VM中。

在GICv4中,Redistributers使用内存中的数据结构共同托管所有虚拟LPI的控制、优先级和挂起信息。Redistributor中的两个寄存器指向以下数据结构:

•GICR_VPROPBASER。

•GICR_VPENDBASER。

在支持LPI但不包括ITS的实现中,GICR_*寄存器包含一个简单的内存映射接口,用于信号和控制物理LPI。

Redistributers提供了一个编程接口,用于:

•识别、控制和配置支持的功能,以启用实施的中断和中断路由。

•启用或禁用SGI和PPI。

•设置SGI和PPI的优先级。

•将每个PPI设置为水平敏感型或边缘触发型。

•将每个SGI和PPI分配给一个中断组。

•控制SGI和PPI的未决状态。

•控制SGI和PPI的活动状态。

•为连接的PE提供电源管理支持。

•在支持LPI的情况下,内存中支持相关中断属性及其挂起状态的数据结构的基地址控制。

•在支持GICv4的情况下,内存中支持相关虚拟中断属性及其挂起状态的数据结构的基地址控制。

Redistributor寄存器由GICR_前缀标识。

有关Redistributor的更多信息,请参阅第2-35页的Affinity routing和第2-30页的The Distributor and Redistributers。

CPU interface

GIC体系结构支持CPU interface,该接口为系统中的PE提供寄存器接口。每个CPU interface提供一个编程接口,用于:

•一般控制和配置,以根据实施的安全状态和遗留支持要求实现中断处理。

•确认中断。

•执行优先级下降。

•中断的停用。

•为PE设置中断优先级掩码。

•定义PE的抢占策略。

•确定PE的最高优先级未决中断。

CPU interface有几个组件:

•一种允许软件监控级别控制物理中断处理的组件。与此相关联的寄存器由ICC_前缀标识。

•一种允许软件监控级别控制虚拟中断处理的组件。与此相关联的寄存器由ICV_前缀标识。

•允许系统管理程序控制一组挂起中断的组件。与此相关联的寄存器由ICH_前缀标识。

注

CPU interface中的系统寄存器与在物理域中处理中断的软件相关联,或者与作为VM一部分的非安全EL1的执行相关联。HCR_EL2的配置确定访问是对物理资源还是对虚拟资源。

在EL2可访问的系统寄存器,用于控制PE的活动、挂起、活动和挂起虚拟中断的列表,由ICH_前缀标识。

有关处理物理中断的更多信息,请参阅第4章物理中断处理和优先级。

有关处理虚拟中断的更多信息,请参阅第6章虚拟中断处理和优先级。

这篇关于ARM IHI0069F GIC architecture specification (7)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!