ihi0069f专题

ARM IHI0069F GIC architecture specification (7)

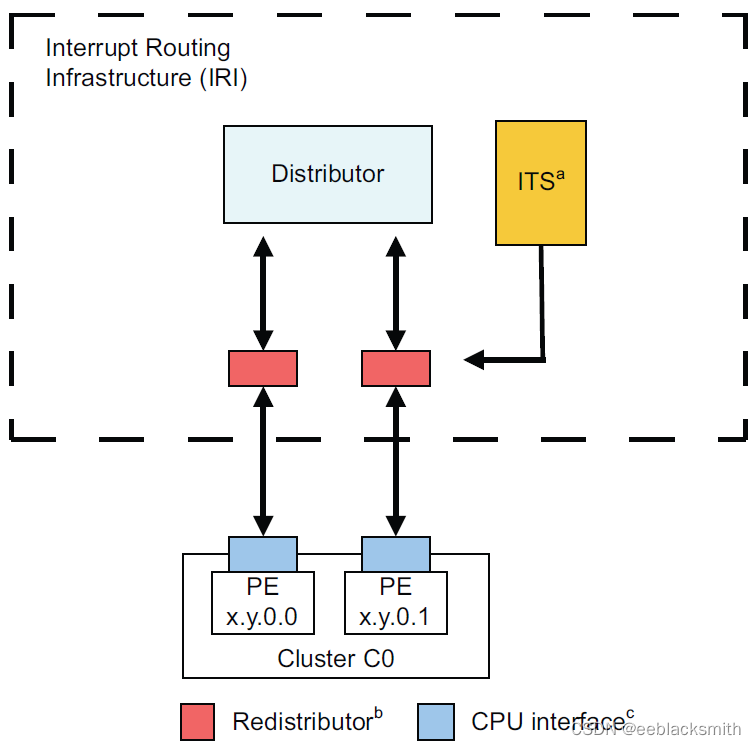

3.1 GIC逻辑组件 GICv3体系结构由一组逻辑组件组成: •Distributor。 •每个受支持的PE都有一个Redistributor。 •支持的每个PE都有一个CPU interface。 •中断翻译服务组件(ITS),支持将事件翻译为LPI。 Distributor, Redistributor和ITS统称为IRI。 a.ITS是可选的,IR

ARM IHI0069F GIC architecture specification (8)

3.2中断旁路支持 CPU interface可以支持中断信号旁路,使得当接口发出的中断信号被禁用时,传统中断信号被传递到PE上的中断请求输入,从而绕过GIC功能。 是否支持旁路由实际设计决定。 用于确定是否使用GICv3 FIQ和IRQ输出或旁路信号的控制取决于是否启用系统寄存器访问。 启用系统寄存器访问时,旁路禁用在最高实现的异常级别使用ICC_SRE_EL1、ICC_SRE-EL2或ICC_

ARM IHI0069F GIC architecture specification (1)

CH1.1 关于通用中断控制器 (GIC) GICv3 架构设计用于与 Armv8-A 和 Armv8-R 兼容的处理元件、PE 一起运行。 通用中断控制器 (GIC) 架构定义: • 处理连接到GIC 的任何PE 的所有中断源的架构要求。 • 适用于单处理器或多处理器系统的通用中断控制器编程接口。 GIC 是一种支持和控制中断的架构资源。 它提供: • 用于管理中断源、中断行为以及将中断路由

ARM IHI0069F GIC architecture specification (2)

1.1.1 GICv2 以来 GIC 架构的变化 GIC 可扩展性 GICv2架构仅支持最多8个PE,因此具有无法扩展到大型系统的功能。 GICv3 通过更改中断路由机制(称为关联路由)以及在中断分配中引入一个新组件(称为重新分配器)来解决此问题。 有关详细信息,请参阅第 3 章 GIC 分区。 通过将 GICD_CTLR.ARE_S 或 GICD_CTLR.ARE_NS 设置为 1 来启用安全