高云专题

【FPGA】高云FPGA之数字钟实验->HC595驱动数码管

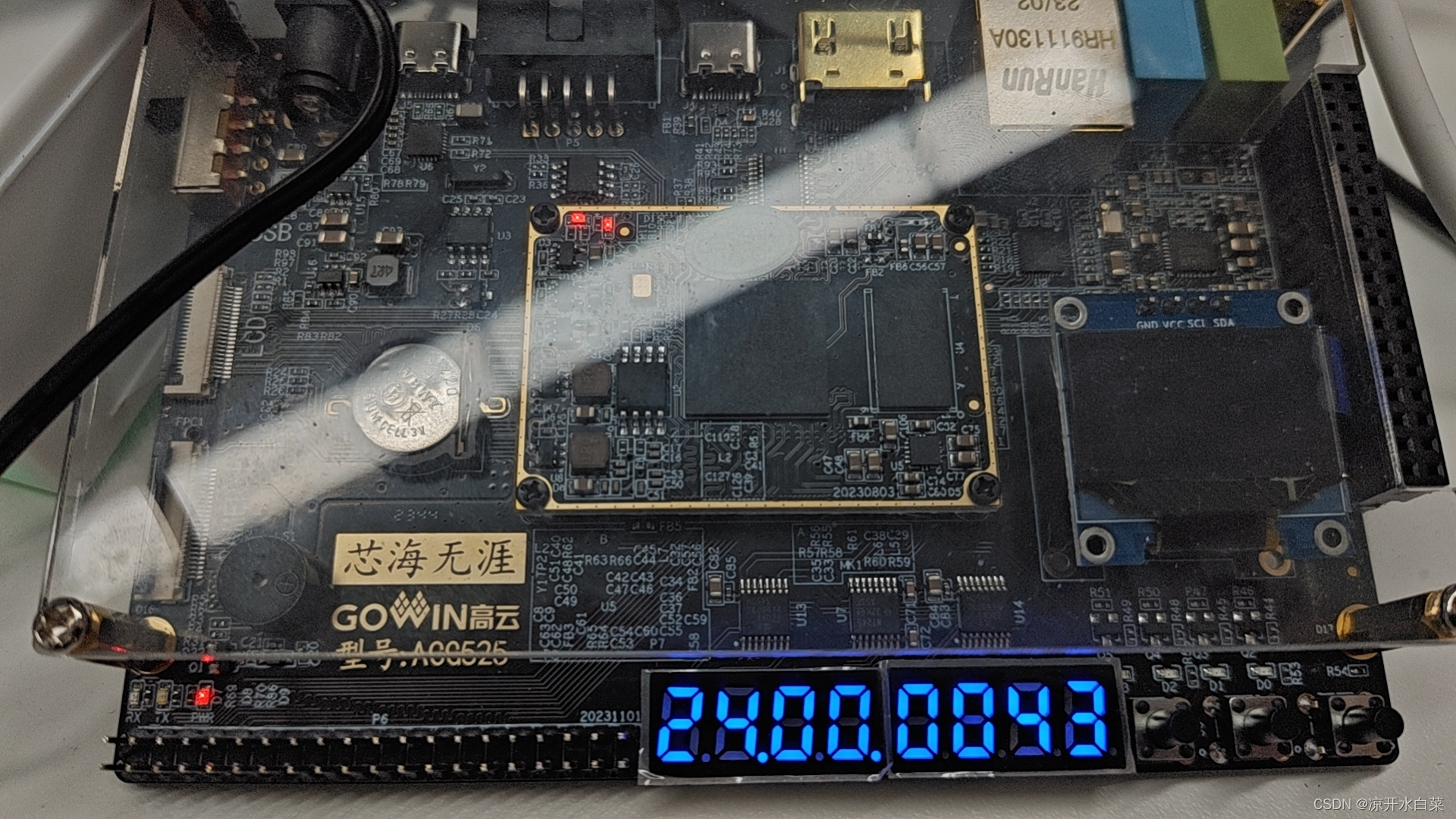

高云FPGA之IP核的使用 1、设计定义2、设计输入2.1 数码管译码显示2.2 74HC595驱动2.3 主模块设计 3、分析和综合4、功能仿真6.1 hex8模块仿真6.2 HC595模块 5、布局布线6、时序仿真7、IO分配以及配置文件(bit流文件)的生成8、配置(烧录)FPGA9、在线调试 1、设计定义 通过74HC595芯片点亮8位数码管,通过计时器实现数码管计时显

Fpga开发笔记(一):高云FPGA芯片介绍,入手开发板套件、核心板和底板介绍

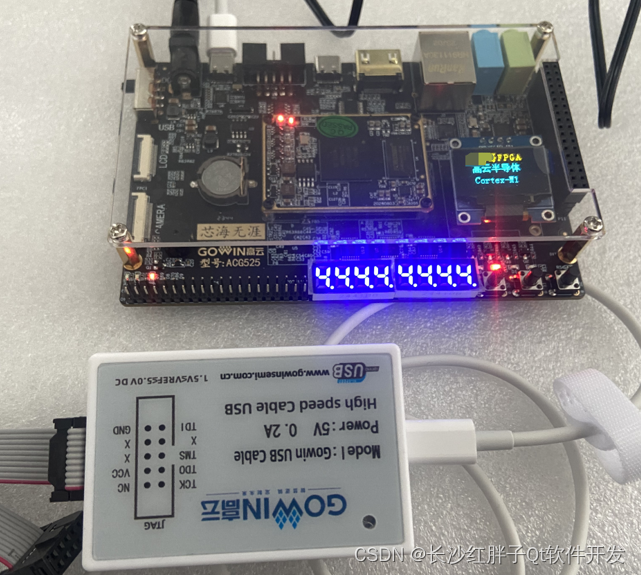

若该文为原创文章,转载请注明原文出处 本文章博客地址:https://hpzwl.blog.csdn.net/article/details/135551179 红胖子网络科技博文大全:开发技术集合(包含Qt实用技术、树莓派、三维、OpenCV、OpenGL、ffmpeg、OSG、单片机、软硬结合等等)持续更新中… FPGA开发专栏 上一篇:没有了 下一篇:敬请期待… 前言 FP

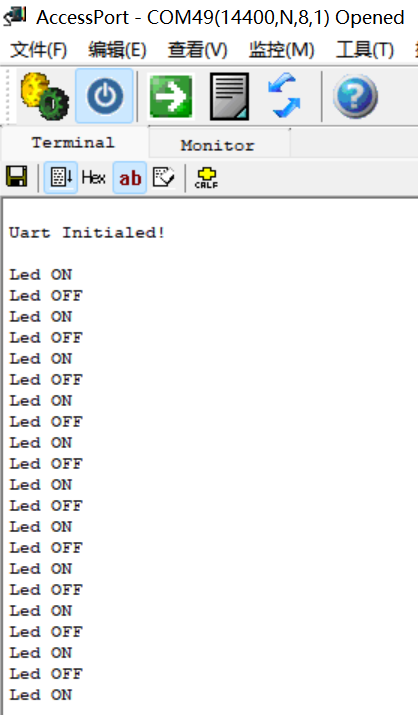

高云GW1NSR-4C开发板M3核串口通信

1.PLLVR频率计算 高云的M3核要用到PLLVR核,其输出频率=FCLKIN*(FBDIV_SEL+1)/(IDIV_SEL+1),但同时要满足FCLKIN*(FBDIV_SEL+1)*ODIV_SEL)/(IDIV_SEL+1)的值在600MHz和1200MHz之间。例如官方示例,其输入频率FCLKIN=50MHz,要输出80MHz,则pllvr_inst.IDIV_SEL = 4,pll

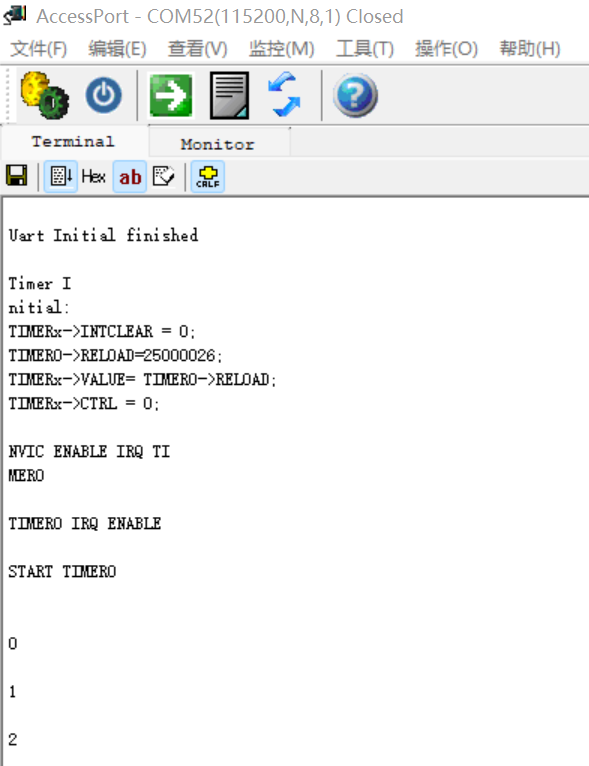

高云GW1NSR-4C开发板M3硬核应用

1.M3硬核IP下载:Embedded M3 Hard Core in GW1NS-4C - 科技 - 广东高云半导体科技股份有限公司 (gowinsemi.com.cn) 特别说明:IDE必须是1.9.9及以后版本,1.9.8会导致编译失败(1.9.8下1.1.3版本IP核可用) 以下根据官方提供的开发包,在GW1NSR-4C开发板上实现8个led点灯及串口通信测试。 2.FPGA综合:

高云GW1NSR-4C开发板上手使用

1.开发板 核心板,主芯片GW1NSR-LV4CQN48P,丝印文字“奥陶纪Octet,QQ群808770961”: 晶振:27MHz,22引脚 两个按键:靠近中间,23引脚,按下为低电平;靠近外侧,20引脚,按下为低电平 靠近USB接口右侧6针为JTAG接口,引脚定义为左侧丝印文字,在6针下侧有4个拨码开关,“on”位置对板载FPGA编程。 底板,丝印文字“Mini_Star Basi

国产高云FPGA:纯verilog实现视频图像缩放,提供6套Gowin工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐国产高云FPGA相关方案推荐国产高云FPGA基础教程 3、设计思路框架视频源选择OV5640摄像头配置及采集动态彩条跨时钟FIFO图像缩放模块详解设计框图代码框图2种插值算法的整合与选择 Video Frame Buffer 图像缓存DDR3 Memory Interface 4、Gowin工程1:640x480不缩放操作5、Gowin工程2:640x

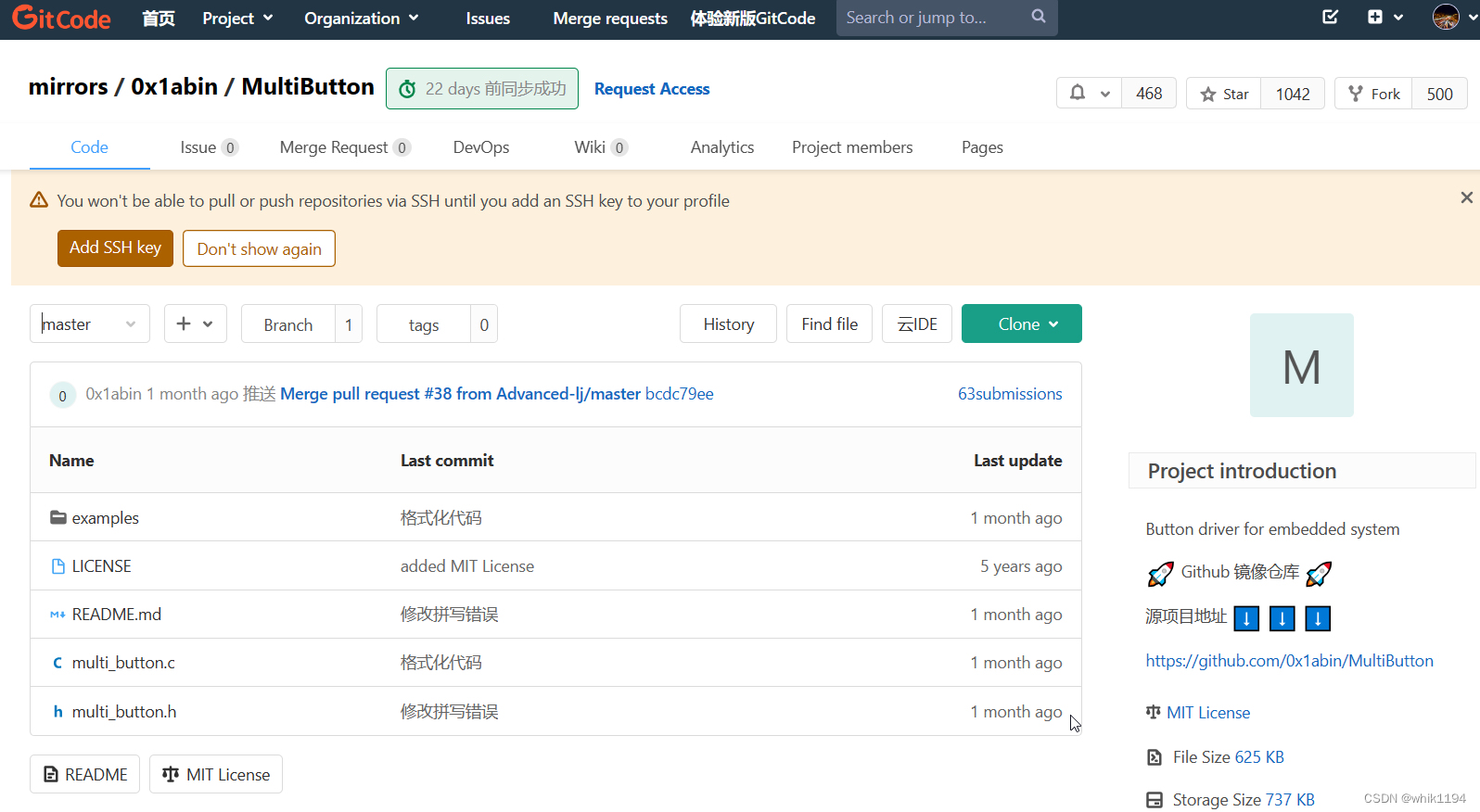

高云FPGA系列教程(11):MultiButton按键驱动模块移植

文章目录 1. MultiButton简介2. MultiButton代码获取3. MultiButton移植4. 测试与运行 本文是高云FPGA系列教程的第11篇文章。 1. MultiButton简介 MultiButton, 一个小巧简单易用的事件驱动型按键驱动模块,可无限量扩展按键,按键事件的回调异步处理方式可以简化你的程序结构,去除冗余的按键处理硬编码,让你

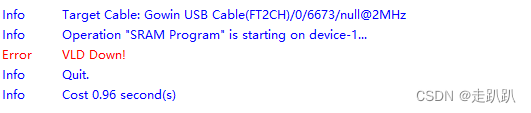

国产FPGA 高云 GOWIN FPGA 遇到的VLD POR ERR奇葩现象和问题

这次遇到的奇葩问题是高云的FPGA,芯片的型号是GW1N-LV1QN48C6I5。 具体遇到的问题是 用下载器读取芯片ID 功能时一切正常 如图。 当要下载到芯片(SRAM 或者EFLASH(内部flash))时就报错,而报错的原因主要是两个 一个是POR报错 一个是VLD报错 如下图 而读取芯片ID是完全正常的 ,这说明芯片至少在JTAG口这