时隙专题

LIN线调度表测试-顺序 时隙

文章目录 "slot delay"(时隙延迟)jitter 抖动时间故障示例 “slot delay”(时隙延迟) 在 LIN 总线中,“slot delay”(时隙延迟)指的是分配给发送报文的时间隙。不同的报文可能有不同的发送时隙,这个时隙延迟决定了报文可以被发送的时间。 LIN 协议是一种主从结构的通信协议,通信只能由主机节点发起。主机任务负责发送报头,从机任务根据

【时隙ALOHA,CSMA(载波侦听多路访问)carrier sense mltiple access,无线局域网: CSMA/CA】

文章目录 时隙ALOHA时隙ALOHA的效率( Efficiency )纯ALOHA(非时隙)----效率低CSMA(载波侦听多路访问)carrier sense mltiple accessCSMA冲突CSMA/CD(冲突检测)边说边听(提高了信道利用率)以太网就是用的这个无线局域网: CSMA/CA无线局域网中的 MAC:CSMA/CA无线局域网: CSMA/CA冲突避免(续)

5G/4G:空口帧结构之帧、子帧、时隙、符号、RB。

5G引入了参数集的概念,针对不同环境选择不同的参数集大大增加了通信的灵活性。 子载波:不同参数集下,子载波间隔的变化,在上一篇中做了比较详细的介绍。 帧结构: 帧(Frame)的时间仍然是10ms,分为10个子帧(Subframe),编号为#0~#9,每个子帧时间为1ms,一个时隙所包含的OFDM符号数为14个(normal cp),每一帧又可以分为两个半帧(half-frame),编号

HFC-S mini芯片时隙设置

HFC-S mini芯片有4个HDLC通道,分别是B1、B2、AUX1、AUX2,至于为什么编号不是一直顺序到4,我也不知道。 HFC-S mini芯片的工作模式有如下2种: Simple Mode:在该模式下,4个FIFO通道对应4个PCM时隙。 Channel Select Mode:该模式下,可以把多个FIFO连接到一个PCM时隙上,一般不用这种模式。 该芯片可以连接2MB

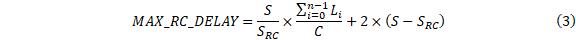

芯准TTE宏时隙调度机制 —— RC帧延时分析

芯准TTE的宏时隙机制将TT流量与RC流量占用的输出接口带宽进行固定划分,实现TT帧的离线规划与调度和RC帧的调度完全解耦,极大地简化了TTE网络中对RC帧延时评估的复杂度。本文从理论上推导在宏时隙RC调度中的RC队列长度上限和RC帧延时上限,对TTE混合流量调度的性能评估具有重要意义。 1. TTE网络中的RC帧延时评估问题 现有TTE输出调度不静态划分TT帧使用带宽和RC帧使用带宽[

华为和其他厂家设备时隙换算

SDH时隙划分的方式,和设备对接中时隙如何选择。支路位置编号通常有2种方式,时隙编号和线路编号: RAISECOM和华为采用时隙编号方式,中兴、烽火、MARCONI、朗讯公司采用线路编号方式。 如果不需要特别指定3-7-3结构,只需要知道互相对应的时隙编号,可以利用一下简便算法计算: 需要计算的时隙编号=已知的时隙编号+20 ×(TU12编号-TUG3编号) 如已知华为28号时隙,那么

华为和其他厂家设备时隙换算

SDH时隙划分的方式,和设备对接中时隙如何选择。支路位置编号通常有2种方式,时隙编号和线路编号: RAISECOM和华为采用时隙编号方式,中兴、烽火、MARCONI、朗讯公司采用线路编号方式。 如果不需要特别指定3-7-3结构,只需要知道互相对应的时隙编号,可以利用一下简便算法计算: 需要计算的时隙编号=已知的时隙编号+20 ×(TU12编号-TUG3编号) 如已知华为28号时隙,那么