制程专题

(南京观海微电子)——半导体制程介绍

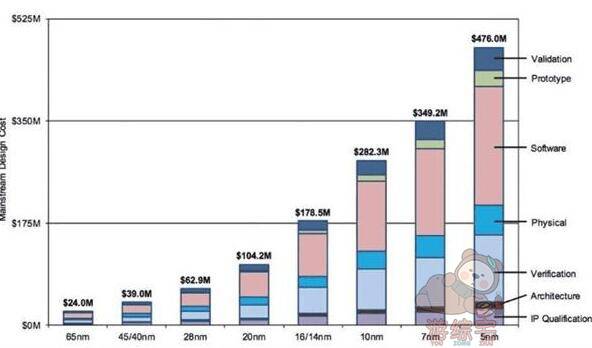

半导体的制程: 1. IC 设计: 预先规划芯片的功能,功能包含算术逻辑、记忆功能、 浮点运算、 数据传输,各功能分布在芯片上各区域,并制作所需的电子元件,工程师使用(HDL)设计电路图,在将 HDL 程序码放入自动化电子设计工具(EDA Tool),计算机把程序码转换成电路图。 2. 晶圆制造: 将硅纯化、溶解成液态,从中拉成柱状的硅晶柱,上面有一格一格的硅晶格,将晶体管放置在硅

[激光原理与应用-125]:南京科耐激光-激光焊接 - 焊中无损检测技术 - 智能制程监测系统IPM介绍 - 25-传统的时域波形分析法、时域包络线分析法

目录 前言: 一、时域波形分析法 1.1 时域波形分析法的基本概念 1.2 时域波形分析法的具体步骤 1.3 时域波形分析法的特点 二、时域包络线分析法 2.1 单信号的包络线 1. 定义 2. 分析步骤 3. 应用领域 4. 优点与局限性 2.2 多个时域信号组成的包络线:极值包络信号 三、激光焊接焊中缺陷检测:时域包络线分析法 3.1 激光焊接中的常见缺陷 3.2

4nm制程工艺的真·锐龙7000处理器功耗

4nm制程工艺的真·锐龙7000处理器功耗很低;但在购机帮你评的一篇对比文章上,又说真·锐龙7000的续航竟然给10nm的第13代酷睿追平了,真·锐龙7000处理器的功耗到底是高还是低啊? 答: ●我们说真·锐龙7000处理器功耗低,说的是在“满载”或者“高负载”情况下,它的功耗相对于英特尔处理器平台低。比如8核/16线程的“基础款”,仅需65W功率,就能跑到全核最高频率;而16核32线程的顶规

芯片制程的疑问? 真的 1.4nm 有必要吗?

第一 大家都知道 单位 面积的 “ 硅晶片上 刻录 的 “道” 数,与晶体管的个数有相关”, 单位 面积的 刻的道数 越多 刻的 晶体管 数就越多。 这个生产能力 叫 “制程” 现在我们都知道: 1、20nm以上 (28,27,25,24... <=10),这些 制程 是 大规模及超大规模数字集成电路,在基础数字电路,基础CPU芯片,这些芯片 应用 速度 稳定 功耗 价格 完全接受;

【深亚微米CMOS前段工艺制程】

深亚微米CMOS前段工艺制程(温德通集成电路制造工艺与工程应用) 深亚微米特征尺寸的CMOS前段工艺,与亚微米CMOS工艺最大的区别在于:1)利用STI结构隔离技术;2)形成Co-Salicide;3)是双阱结构(NW和PW),如果要全隔离的NMOS器件,那么就需要DNW(deep NW),为形成Non-Salicide区域还需要用到SAB掩模版;4)如果考虑高阻值多晶硅电阻,还要用到HRP(H

台积电纳米芯片突破2nm制程 2023年试产

根据最新报导,台积电已经在2nm制程上取得一项重大的内部突破,虽未披露细节,但是据此乐观预计,2nm制程有望在2023年下半年进行风险性试产,2024年就能步入量产阶段。 台积电还表示,2nm的突破将再次拉大与竞争对手的差距,同时延续摩尔定律,继续挺进1nm制程的研发。台积电预计,苹果、高通、NVIDIA、AMD等客户都有望率先采纳其2nm制程。华为就没机会享受了。 2nm

7纳米duv和euv_要超车台积电,三星采用 EUV 技术 7 纳米制程完成验证

在晶圆代工市场中,台积电与三星的竞争始终是大家所关心的戏码。其中,三星虽然有高通这样的VIP 客户,但在 7 纳米制程节点上,高通预计会转投回台积电的情况下,三星要想受到更多的客户的青睐,只能从工艺技术上着手了。 这也是三星为什么跳过非 EUV 技术的 7 纳米制程,直接上 7 纳米 LPP EUV 制程技术的原因。如今,三星终于公布了他的 7 纳米 LPP 制程已经完成了新斯科技(Synops

7纳米duv和euv_EUV光刻技术竞争激烈,三星7纳米EUV制程已完成新思科技物理认证,台积电紧追其后...

在晶圆代工市场,台积电与三星的竞争始终是大家关心的戏码。三星虽然有高通等VIP客户,但在7纳米制程节点,高通预计会转投台积电,三星要想受更多客户的青睐,只能从制程技术着手了。这也是三星为什么跳过非EUV技术的7纳米制程,直接上7纳米LPPEUV制程技术的原因。如今,三星终于公布了7纳米LPP制程已完成新思科技(Synopsys)物理认证,意味着7纳米EUV制程将可全球量产了。 目前全球前几大晶

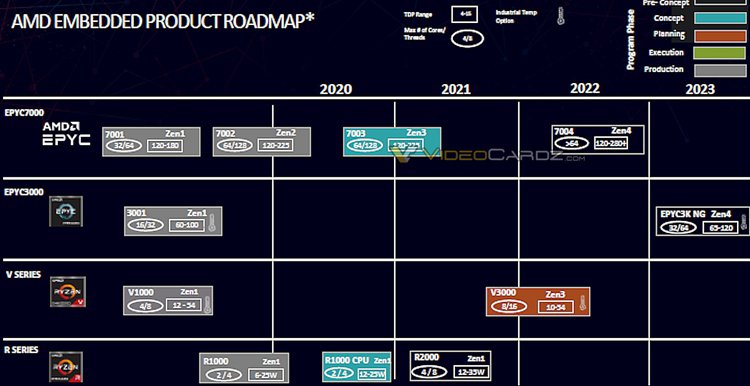

280nm芯片服务器,AMD Zen 4霄龙处理器曝光:核心超96核,5nm制程

与消费级处理器一样,AMD的服务器级别处理器也就是霄龙处理器几年来也大受数据中心或者服务器厂商的欢迎,目前AMD已经发布了基于Zen 3架构的霄龙处理器,此外除了即将发布的线程撕裂者之外,其他的Zen 3架构处理器布局的也差不多了。接下来就是大家十分期待的Zen 4架构产品,按照AMD在新一代处理器上的发布惯例,首先采用Zen 4架构的应该就是霄龙服务器。 目前网上曝光了一张关于AMD今后处理

(02)半导体前道制程工艺概览

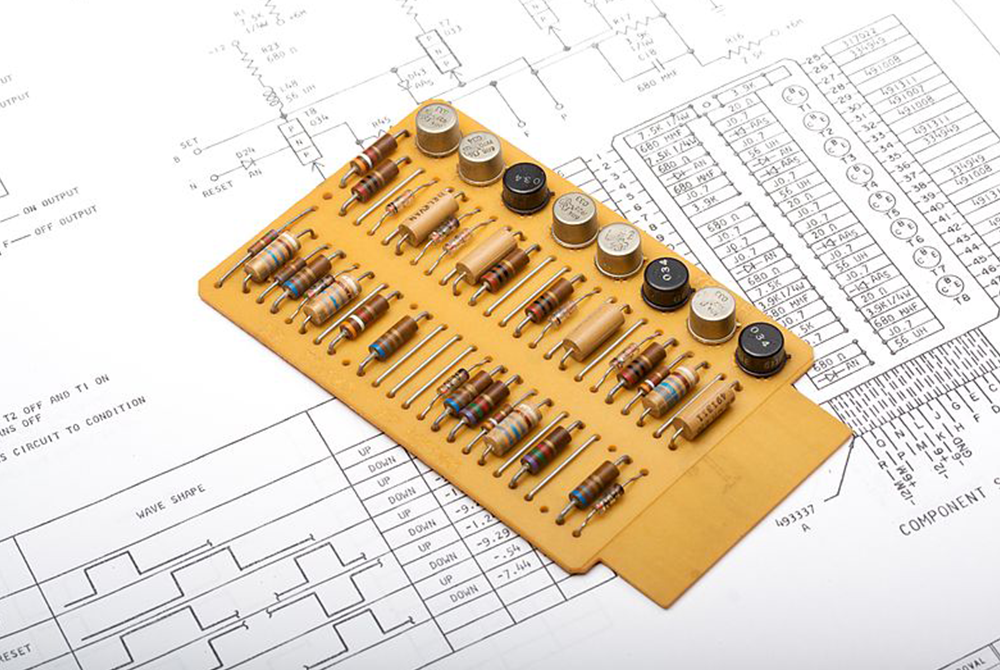

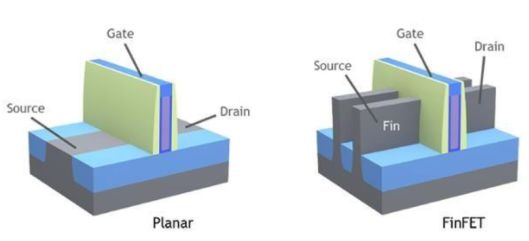

01、半导体制程工艺概览 在第一篇的最后,我们说到金属氧化物半导体场效应晶体管(MOSFET)的平面式结构让人们可以在晶圆上同时制造出好几个MOSFET。且与第一代晶体管BJT¹不同,MOSFET无需焊接过程。本期内容就让我们来详细了解一下具体的制程工艺。 为方便讲解,我们先来看一下普通电子零件是怎么制成的。只要拆解身边的任何一件电子产品,我们便不难发现:其基本结构都是把晶体管、干电池、蓄电池

Xilinx 产品制程工艺

A – 45nm 供货至2030年 Sparton6 xx 提供卓越的连接功能,例如高逻辑引脚比、小尺寸封装、MicroBlaze™ 软处理器,以及多种受支持的 I/O 协议。 B – 28nm 供货至2035年 spartan-7\artix-7 \kintex-7\virtex-7\Zynq™ 7000 SoC 工艺节点上的持续创新使新器件能够以更低的功耗在整个产品系列中实现最佳性能,

ASIC芯片设计全流程项目实战课重磅上线 ,支持 65nm制程流片 !

全流程项目实战课学什么? 此次推出【 ASIC芯片设计全流程项目实战课】,基于IPA图像处理加速器,以企业级真实ASIC项目为案例,学员可参与全流程项目实践,以及65nm真实流片! 众所周知,放眼整个IC硕士圈,有实力安排流片的也就那么几家高校。所以正经参与过流片的同学也属实是凤毛麟角。 这次IC修真院推出可流片的项目,就是为了帮助有需要的同学解决这个难题。 这门课基于IPA,即“Im

windows缩放200模糊_半导体缩放比例真的到头了吗? 3nm、5nm制程了解一下

半导体工艺在进入14nm/16nm制程之后,最经常被提到就是鳍式场效应晶体管(FinFET),它的出现满足了7nm至14nm之间的工艺制造。不过在进入更小的5nm、甚至3nm之后,FinFET工艺已经难以满足半导体芯片的制造需求,业界也在对新一代晶体管进行研究。 为此,几大晶圆厂正在市场上加速5nm制程,但现在客户必须决定是围绕当前的晶体管类型设计他们的下一个芯片,还是转移到3nm及以上的不

![[激光原理与应用-125]:南京科耐激光-激光焊接 - 焊中无损检测技术 - 智能制程监测系统IPM介绍 - 25-传统的时域波形分析法、时域包络线分析法](https://i-blog.csdnimg.cn/direct/105bb2facaea44d2aa57b021af22404e.png)