zc706专题

TQZC706开发板教程:在ZC706上运行ADRV9371(vivado2018.3)

首先需要在github上下载两个文件,本例程用到的文件以及最终文件,我都会放在网盘里面,地址在本文的末尾,需要自行提取 在github上搜索hdl选择第一个-->选择版本-->我所使用的vivado是2018.3版本,所以这里我下载的是hdl_2019_r1-->在附录中下载资源-->下载对应版本的No-Os 把下载好的资源复制到虚拟机里解压缩,右键打开命令行 设置环境变量-->进入项目

TQZC706开发板教程:在ZC706上运行AD9361

首先需要在github上下载两个文件,本例程用到的文件以及最终文件,我都会放在网盘里面,地址在本文的末尾,需要自行提取 在github上搜索hdl选择第一个-->选择版本-->我所使用的vivado是2018.3版本,所以这里我下载的是hdl_2019_r1-->在附录中下载资源-->下载对应版本的No-Os 把下载好的资源复制到虚拟机里解压缩,右键打开命令行 设置环境变量-->进入

ZC706评估板IBERT调试中unlock和link问题

----写在前面:主要是针对zc706调试ibert的过程中发现unlock和link问题,找到了网上写的比较好的两篇文章,但是描述都有不足的地方,代码也有修改,我这里结合自己踩的坑,把问题和解决方法讲清楚。 一、IBERT与GT收发器概述 1. IBERT IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPG

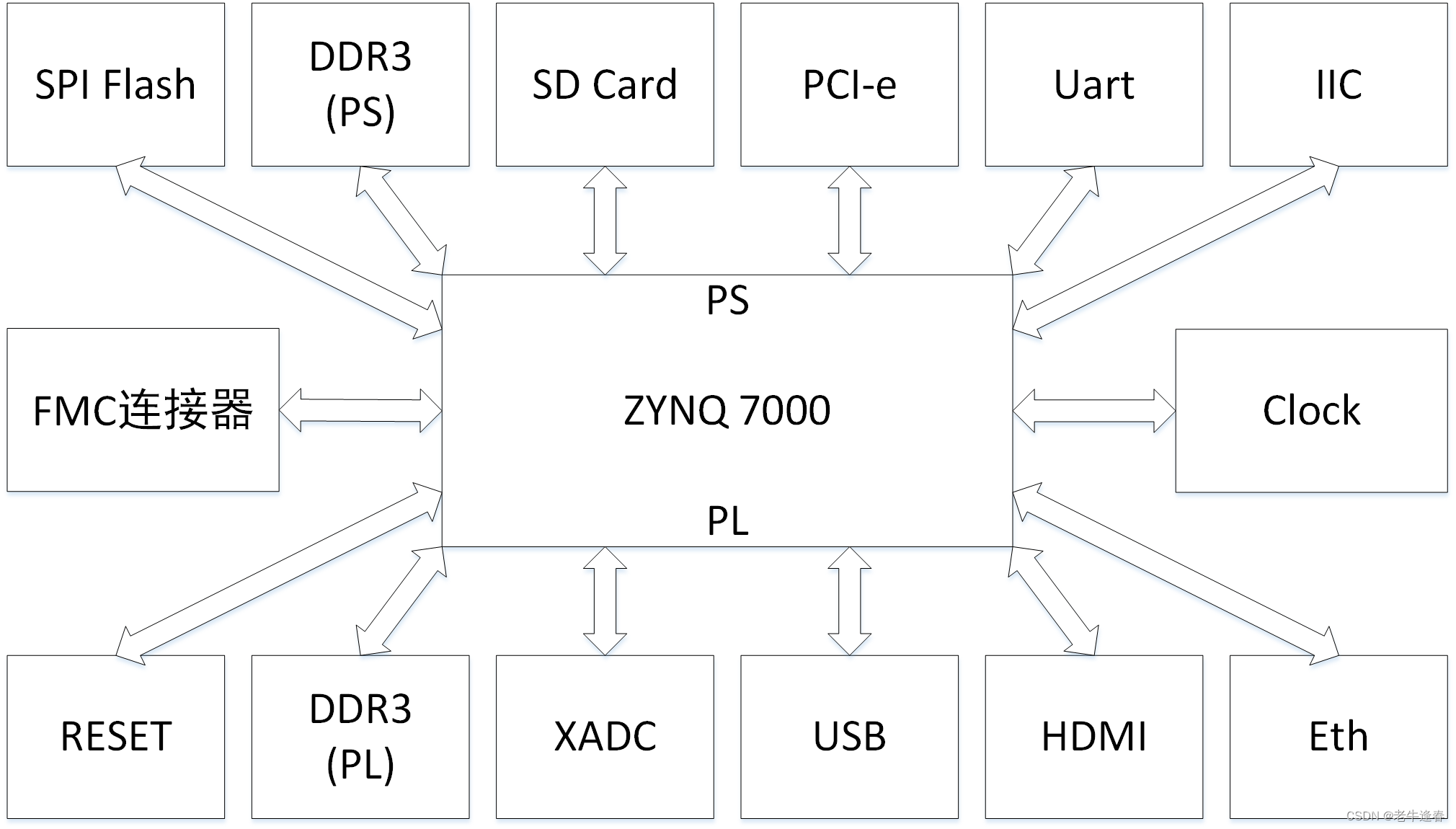

基于xilinx公司ZC706开发板的XDMA_PCIE接口设计。

基于xilinx公司ZC706开发板的XDMA_PCIE接口设计。 笔者主要是以自己的亲身经历介绍自己初学PCIE接口时的一些经验和碰到的一些问题。 开发环境:vivado2017.4;台式机电脑(含有PCIE接口)一台;ZC706可开发板一块 首先,拿到xilinx的ZC706开发板后,第一步要先熟悉整个开发板的各个功能模块,知道自己需要使用的是开发板的哪个模块。第二步的基本工作是去xilin

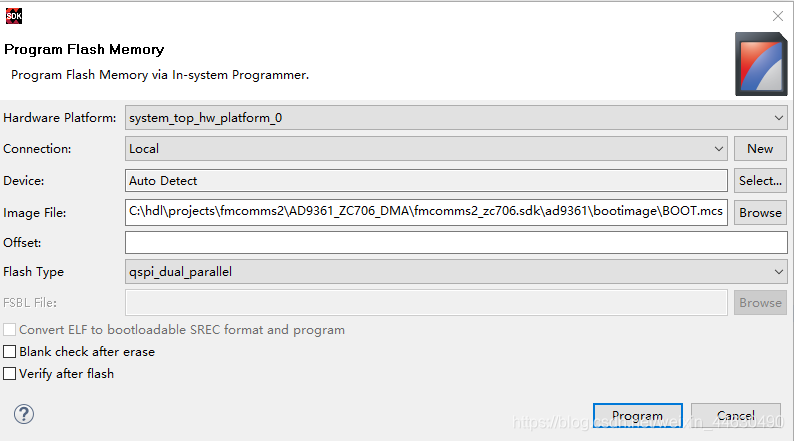

zynq zc706 JTAG调试、QSPI FLASH 程序固化及遇到的问题

接收、发送、滤波器 AD9361 介绍(上) 增益控制、时钟和PLL、ENSM AD9361 介绍 (中) 校准、数据接口 (CMOS) AD9361 介绍 (下) 数据接口(LVDS) SPI和附加接口信号在AD9361 介绍 (终) VIVADO 和 SDK 为2016.4版 一 、JTAG调试 拨码开关如图所示 SW4 0 1 SW11 0 0 0 0 0 点击Program FPG

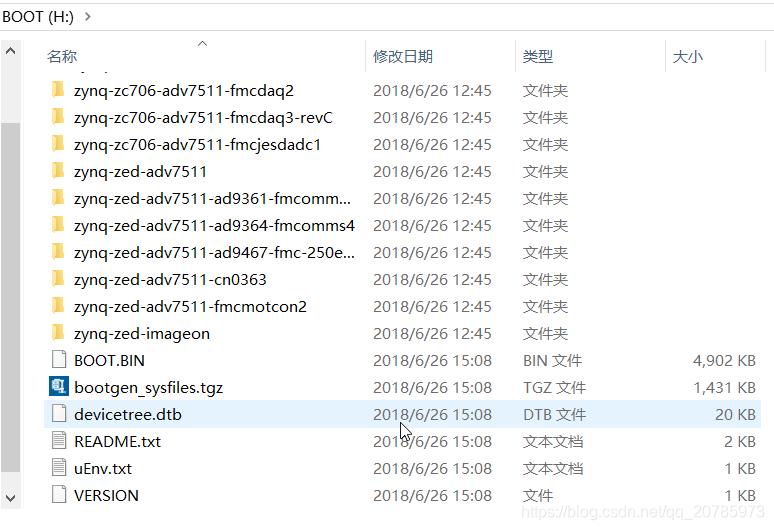

基于ZC706开发板进行SD卡烧写

基于Windows系统进行sdcard烧写: 参考链接下载对应的软件:https://wiki.analog.com/resources/tools-software/linux-software/zynq_images/windows_hosts 下载镜像文件:https://wiki.analog.com/resources/tools-software/linux-software/zy

阅读ZC706开发板资料

板级资源: 一颗Zynq-7000 SOCPL侧有1GB DDRPS侧有1GB DDR,2个128Mb SPI flashUSB 2.0接口,ULPI协议安全数字连接器(?这个是啥,目前还么有搞明白)USB接口型态的 JTAG调试接口时钟源:200MHz固定始终,I2C可编程始终,33.33MHz固定的LVCOMS时钟等GTX高速收发器PCIE从设备(1.0、2.0)SFP连接器网口 RGMII

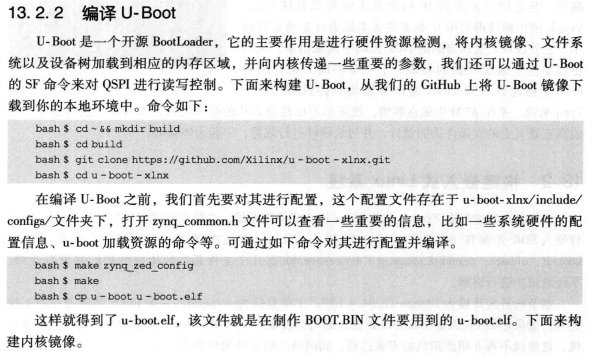

zc706 linux镜像,Zynq ZC706 传统方式移植Linux -- 编译u-boot

我用的是zc706不是zed 基本思路是: 2.下载xilinx uboot源码 git clone https://github.com/xilinx/u-boot-xlnx.git 3.编译 make zynq_zc706_defconfig make CROSS_COMPILE=arm-xilinx-linux-gnueabi- 出现如下错误: *** Your GCC is older