xdma专题

XDMA - AXI4 Memory Mapped

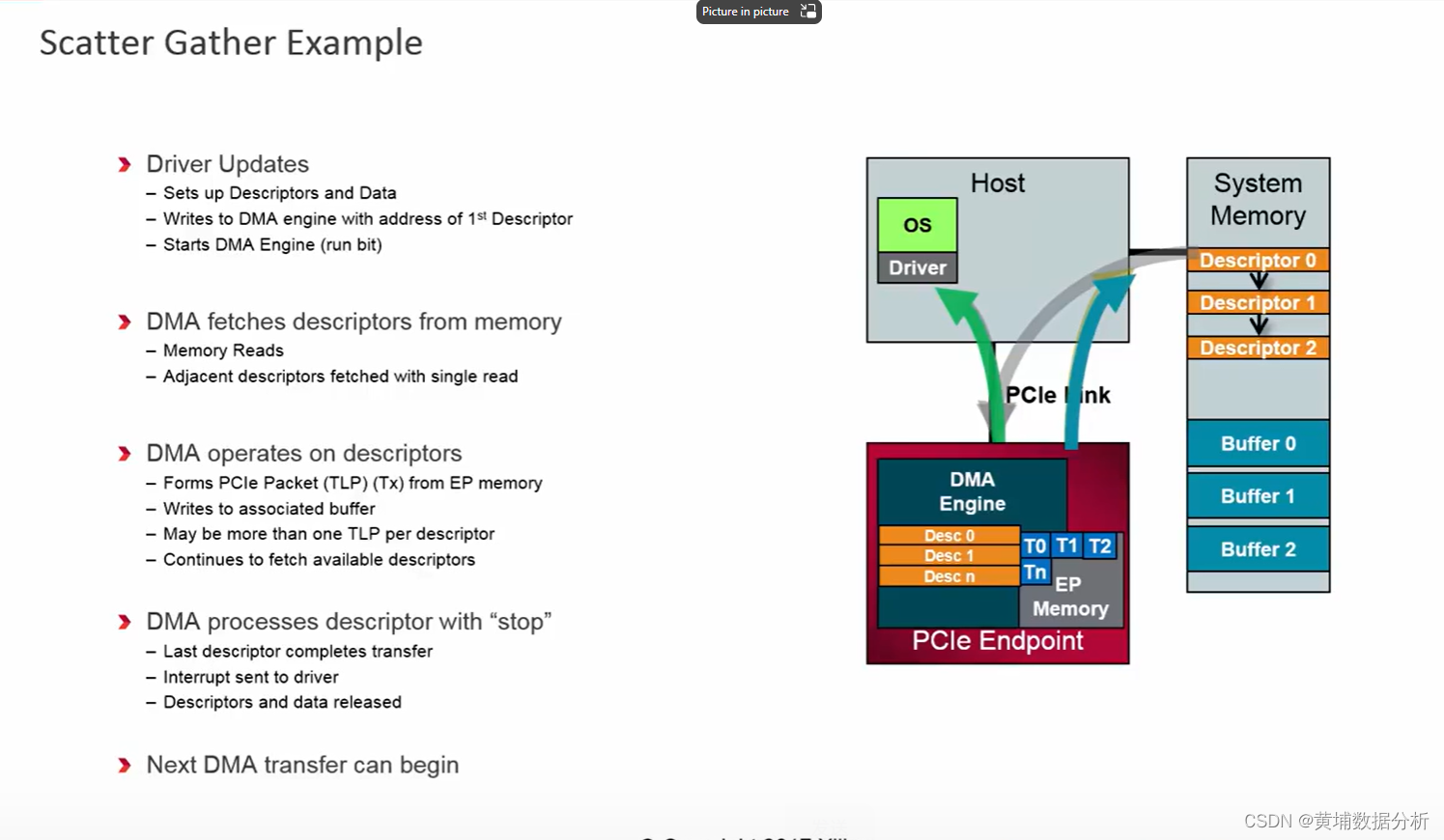

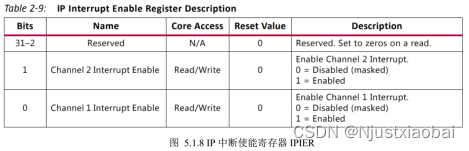

目录 1. What is SG DMA2. Descriptor3. Transfer for H2CStep 1. The host prepares stored data and creates descriptors in main memoryStep 2. The host enables DMA interruptsStep 2. The driver initializes

XILINX 7系列XDMA使用_IP核介绍以及工程搭建

文章目录 一、XDMA IP核1.1、接口说明1.2、配置页说明 二、XDMA工程搭建2.1、BD搭建2.2 Linux下XDMA驱动安装2.3 Linux下使用XDMA进行数据传输 一、XDMA IP核 1.1、接口说明 sys_clk:主机给PCIE提供的时钟信号,通过原理图查看 sys_rst_n:主机提供的冷复位,原理图查看 usr_irq_req:用户中断请求

博客摘录「 AXI三种接口及DMA DDR XDMA介绍(应用于vivado中的ip调用)」2024年6月10日

关键要点: 1.AXI Stream经过协议转换可使用AXI_FULL(PS与PL间的接口,如GP、HP和ACP)。 2.传输数据类里就涉及一个握手协议,即在主从双方数据通信前,有一个握手的过程。基本内容:数据的传输源会产生“VALID”信号,来指明何时数据有效或控制信息有效。而在目标源一方,会产生“READY”信号,来指明已经准备好接受数据或控制信息。当“VALID”信号和“READY”信号

XDMA原理及其应用和发展

XDMA原理 XDMA的主要原理是通过直接访问主机内存,实现数据的快速传输。在传统的DMA(Direct Memory Access)技术中,数据传输需要经过CPU的干预,而XDMA可以绕过CPU,直接将数据从外设读取到主机内存或者从主机内存传输到外设。这种技术依赖于PCIe(Peripheral Component Interconnect Express)总线,PCIe是一种高速串行总线

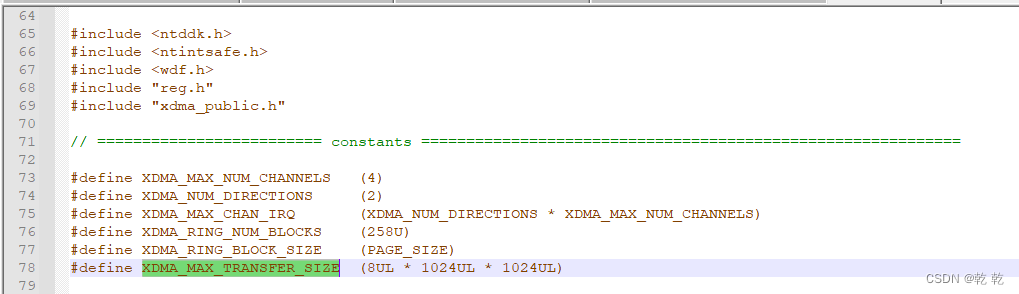

xilinx xdma drive 传输8MB以上数据受限的问题

当传输超过8 MB数据时报错error code=1359, #define XDMA_MAX_TRANSFER_SIZE (8UL * 1024UL * 1024UL) 可以修改成: #define XDMA_MAX_TRANSFER_SIZE (80UL * 1024UL * 1024UL) VS2019 + WDK环境的搭建 先准备好VS + WDK的驱动开发环境。需要下

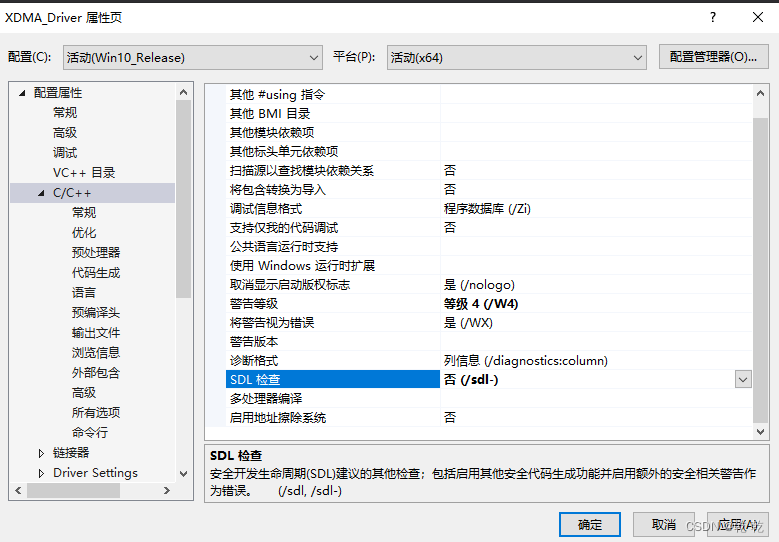

XDMA windos 编译

1、先安装 Visual Studio 2019 2、Download the Windows Driver Kit (WDK) - Windows drivers | Microsoft Learn 以前的 WDK 版本和其他下载 - Windows 驱动程序 |Microsoft学习 注意版本:下载2004的版本 3、 选择使用10.0.19041.0 安装这个sdk

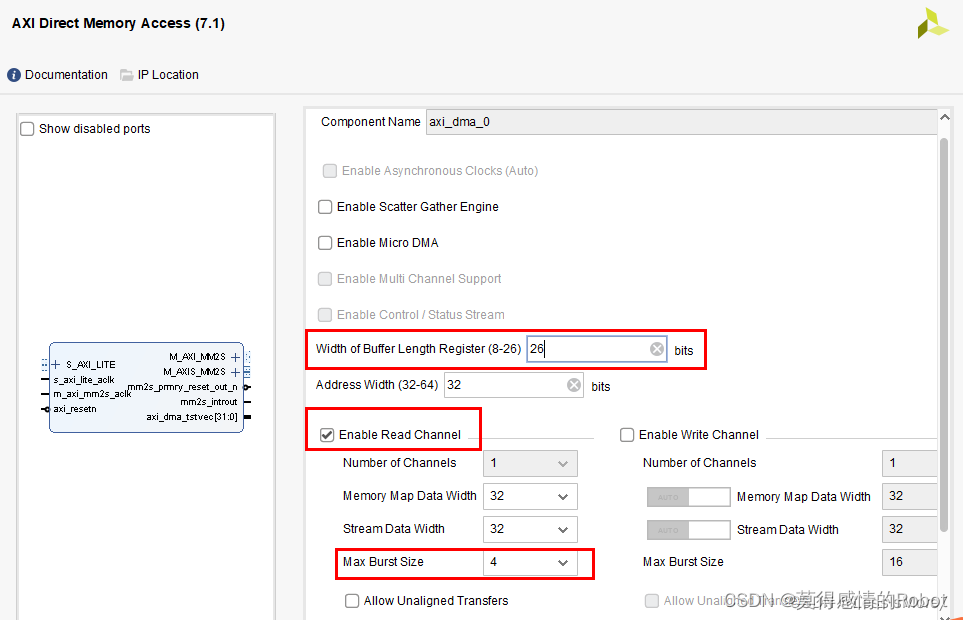

手把手教你学会 Xilinx PCIE/XDMA 读写DDR系列(二) ——XDMA详细配置步骤

因最近想通过PCIE把数据从FPGA传到PC,借此机会和大家一起学习XDMA读写DDR 制作不易,记得三连哦,给我动力,持续更新!!! 完整工程文件下载:XDMA读写DDR工程 提取码:4sxh 上一期讲到如何配置DDR的IP,相信很多小伙伴已经成功的把DDR配置成功,那么下一步就要对PCIE的IP进行配置 PCIE的IP在vivado中一般是通过XDMA实现的,XDMA有太多优点

【xdma】 pcie.bar设置

FPGA优质开源项目– PCIE通信 xdma 两者保持一致 FPGA开源项目 – PCIE I/O控制卡 xdma PCIe的XDMA应用 读写部分分为两种,一种是数据的读写,另一种是配置数据的读写,在数据读写部分,DMA通过MIG控制DDR完成数据读写。配置数据读写通过与BRAM通过AXI-lite总线连接完成,XDMA将PCIe配置信息存在BRAM,在进行配置信息读写

基于xilinx公司ZC706开发板的XDMA_PCIE接口设计。

基于xilinx公司ZC706开发板的XDMA_PCIE接口设计。 笔者主要是以自己的亲身经历介绍自己初学PCIE接口时的一些经验和碰到的一些问题。 开发环境:vivado2017.4;台式机电脑(含有PCIE接口)一台;ZC706可开发板一块 首先,拿到xilinx的ZC706开发板后,第一步要先熟悉整个开发板的各个功能模块,知道自己需要使用的是开发板的哪个模块。第二步的基本工作是去xilin

FPGA(基于xilinx)中PCIe介绍以及IP核XDMA的使用

Xilinx中PCIe简介以及IP核XDMA的使用 例如:第一章 PCIe简介以及IP核的使用 文章目录 Xilinx中PCIe简介以及IP核XDMA的使用一、PCIe总线概述1.PCIe 总线架构2.PCIe 不同版本的性能指标及带宽计算3.PCIe 接口信号 二、XDMA1.XDMA 与其它 PCIe IP 的区别2.XDMA简介 三、IP核例化BACIS标签页PCIe ID标签

Xilinx XDMA驱动代码分析及用法

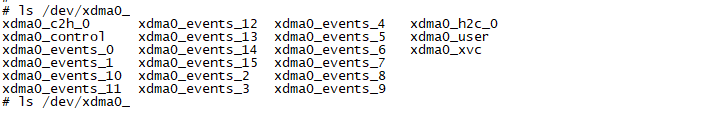

Xilinx XDMA驱动代码分析及用法 先简单的介绍一下,赛灵思的XDMA的驱动是用于做什么的、他的主要功能就类似与网卡pcie接口的网卡驱动、用于控制主机与fpga设备进行pcie的通讯。通讯的主要方式是设备文件的读写,这里不清楚的同学可以看一下我上一篇文章。通过控制设备文件的读写,操作驱动与fpga设备进行数据传输。 1、目录结构 zacha@Superman:~/nfs/xdma-d

xdma stream (timeout)

xdma 回环 vivado 里有官方示例 fpga:pcie rx – axi-stream master – axi-stream slave – pcie tx 流程:电脑启动读取,然后电脑再在超时时间内写入。或者电脑启动写入,然后电脑再在超时时间内读出。只读取或只写入会报超时,所以需要双线程进行 细节:只有电脑启动读取,pcie tx – axi-stream slave 才会使能 re