versal专题

【xilinx】Versal Soft DDR4 内存控制器 - XCVP1902-2M 速度等级设备上某些存储体的时序收敛问题

描述 当在 XCVP1902 设备上使用软核内存控制器时,如果速度等级为 -2M,目标 Fmax 为 2933 Mbps,某些设计可能无法满足某些存储体的时序要求。 解决方案 如果软核存储控制器使用 SLR0 中的存储体 704/707、SLR3 中的存储体 714/719、SLR1 中的存储体 804/807 或 SLR2 中的存储体 814/819,那么时序收敛可能会很困难。

【xilinx】Versal Adaptive SoC DDRMC - NoC QoS 选项卡未出现

在 2024.1 之前的 Vivado 版本中,用户在使用 NoC 验证块设计时可以访问 NoC 对象窗口和 QoS 选项卡。 Vivado 2024.1 中存在一个已知问题,即 NoC 对象窗口和 QoS 选项卡不出现。 要显示 NoC 对象窗口和 QoS 选项卡,请保存块设计,关闭块设计,重新打开它,然后重新验证该设计。

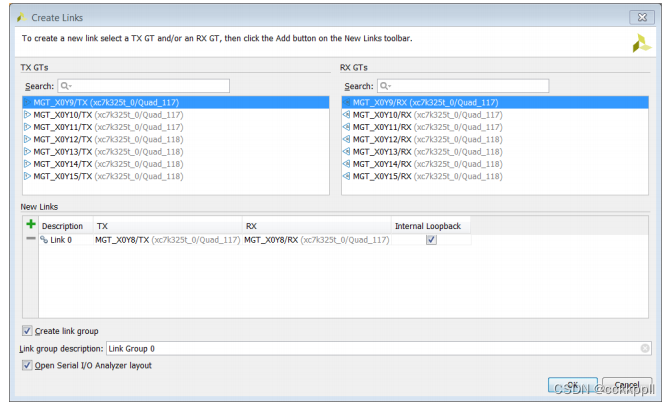

vivado Versal 串行 I/O 硬件调试流程、使用 Vivado Serial I/O Analyzer 来调试设计

Versal 串行 I/O 硬件调试流程 Versal ™ ACAP 无需再生成 IBERT IP , 因为使用系统内串行 I/O 调试所需的必要逻辑现已集成到 GTY 收发器架构内。使 用 GTY 收发器的任何设计均可用于串行 I/O 硬件调试。 Versal 串行 I/O 硬件调试流程具有 2 个不同阶段 : 1. 设计创

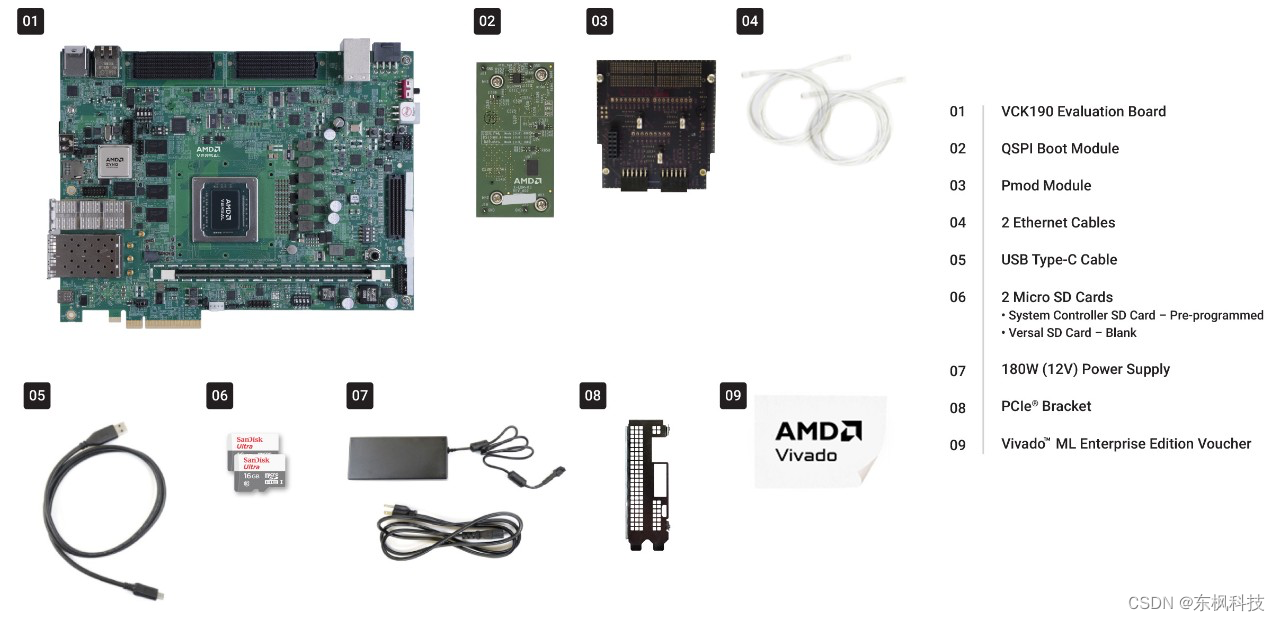

Versal Adaptive SoC Boards, Kits, and Modules

Versal™ AI Edge Series VEK280 Evaluation Kit https://www.xilinx.com/products/boards-and-kits/vek280.html#whatsInside The VEK280 Evaluation Kit, equipped with the AMD Versal™ AI Edge VE2802 adaptive

[versal ] PS noc interface

Coherent interface Ps to noc interface0 Rpu to noc(rpu =LPD) pmc to noc

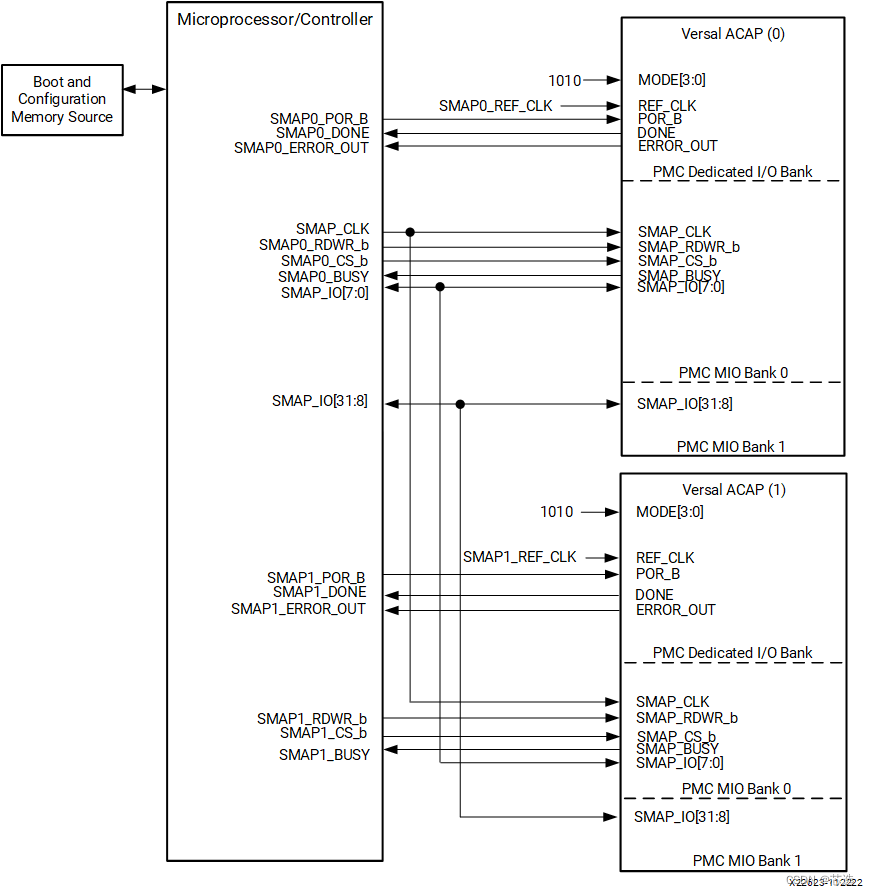

Versal 自适应 SoC SelectMAP 启动检查表

Versal 自适应 SoC SelectMAP 启动检查表 本文档提供了有关 SelectMAP 启动设置的技巧和指南。在提交个案服务请求之前,应认真查看以下检查表。SelectMAP 启动模式的常规检查表: 是否已查看 SelectMAP 文档,了解连接和电源轨的用法? 请参阅相应的 Versal DC 和 AC 数据手册,了解电源轨和 SelectMAP 接口规格,并确保满足这些规格

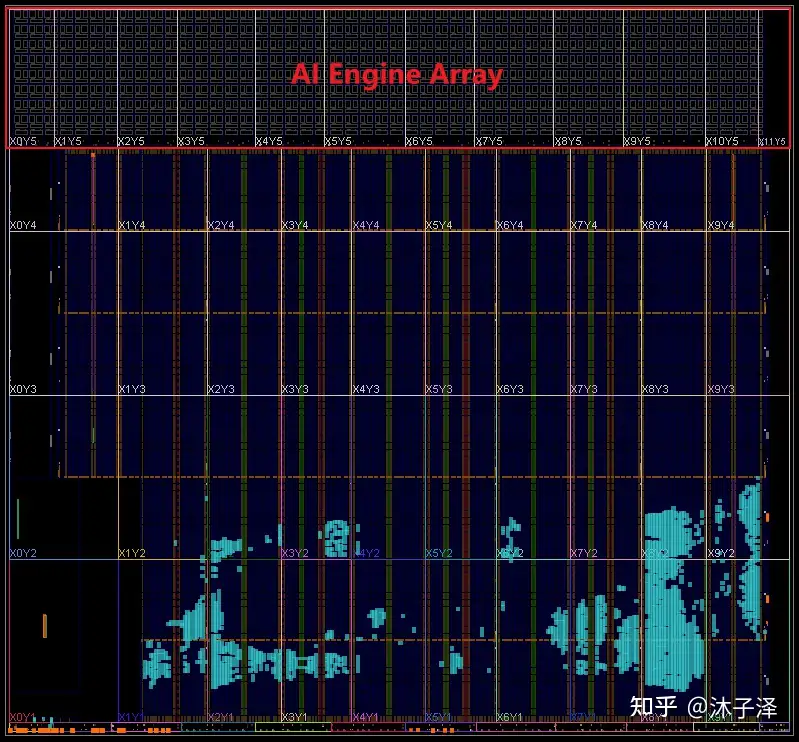

Versal系列0-AI Engine与Systolic Array

最近在开发VCK190时,发现Xilinx Versal系列的AI engine(AIE),其实和Systolic Array(SA)有着很相似的地方。Xilinx工程师在研发AIE时,应该是有所借鉴SA的。 Systolic Array最早是H. T. Kung于1982年在论文《Why systolic architectures?》中提出,但是由于过于过于专用性,在通用处理器当道的年代并没

![[versal ] PS noc interface](https://img-blog.csdnimg.cn/direct/bdf0d035ddce41759e112f65ed762278.png)