v9专题

MapBox Android版开发 3 地图样式v9

MapBox Android版开发 3 地图样式v9 前言MapBox样式对比主要类和方法Style类Style类成员变量Style类Layer方法默认的MapBox样式OnStyleLoaded 接口 MapboxMap类获取样式通过Style.StyleUrl设置样式通过Style.Builder设置样式Style.Builder 示例代码地图样式类界面布局控件响应事件运行效果图 附不

ARM-V9 RME(Realm Management Extension)系统架构之系统初始化流程

安全之安全(security²)博客目录导读 目录 一、重置取消 二、应用处理单元(PE)初始启动 三、MSD初始化 四、GPT初始化 五、初始启动退出(由所有应用PE执行) 六、RMSD初始化 七、PE进入丢失上下文的低功耗状态 本博客提供了RME系统初始化流程的示例,并描述了系统组件之间的关系以及系统启动序列的相应安全注意事项,不包括有关安全启动序列或软件测量流程的具体细

ARM-V9 RME(Realm Management Extension)系统架构之系统启动

本节描述了初始化RME系统的要求。 目录 一、复位需求 二、RME禁用 一、复位需求 RME系统重置(即复位)是指重置整个系统的全局功能状态的任何系统事件。 RME系统重置包括处理单元(PEs)、处理单元集群(PE-clusters)、系统核心逻辑和辅助逻辑、所有系统总线以及所有系统外围设备的重置。 从MSD的角度来看,RME系统重置事件被视为逻辑上相当于对平台进行电源循环(po

【ARMv8/v9 GIC 系列 4.1 -- GIC CPU Interface 访问支持情况】

文章目录 GIC CPU Interface 访问支持Bit[27:24]: GIC CPU接口汇编代码实现访问小结 GIC CPU Interface 访问支持 在ARMv8架构中,ID_AA64PFR0_EL1是一个系统寄存器,提供了有关处理器功能的详绀信息。这个寄存器的位[27:24]专门用于描述GIC(通用中断控制器)CPU接口的系统寄存器接口支持情况。以下是对这些位

ARM-V9 RME(Realm Management Extension)系统架构之功耗管理

安全之安全(security²)博客目录导读 目录 一、系统功耗管理 1、功耗状态 2、PE功耗管理 3、系统和PE集群功耗管理 4、系统功耗状态 二、RME组件功耗管理 本节规定了RME系统的功耗管理规则。 功耗管理流程定义了系统及其组件如何在各种电源状态之间进行转换,以及如何执行与此相关的操作,如切断电源域和管理上下文。 本章节描述的RME电源管理要求包括以下内容:

phpcms V9 安装后台无法打开解决方案

第一种可能:phpcms v9 登录是采用session ,保存session 有两种方式,一种是数据库存储的方式,一种是文件存储方式,默认是数据库存储方式。有时数据库这种方式不行,可以在 \caches\configs\system.php 中修改sesion 的存储方式//Session配置 'session_storage' => 'mysql',将其改为//Session配置'sessio

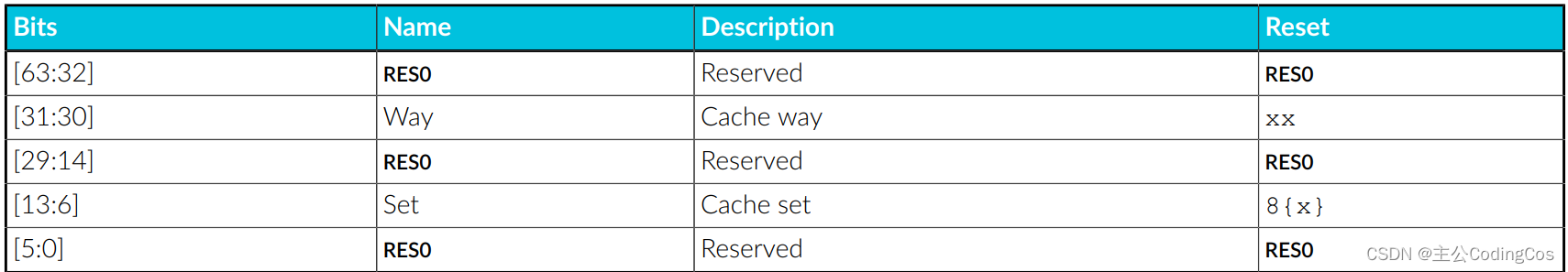

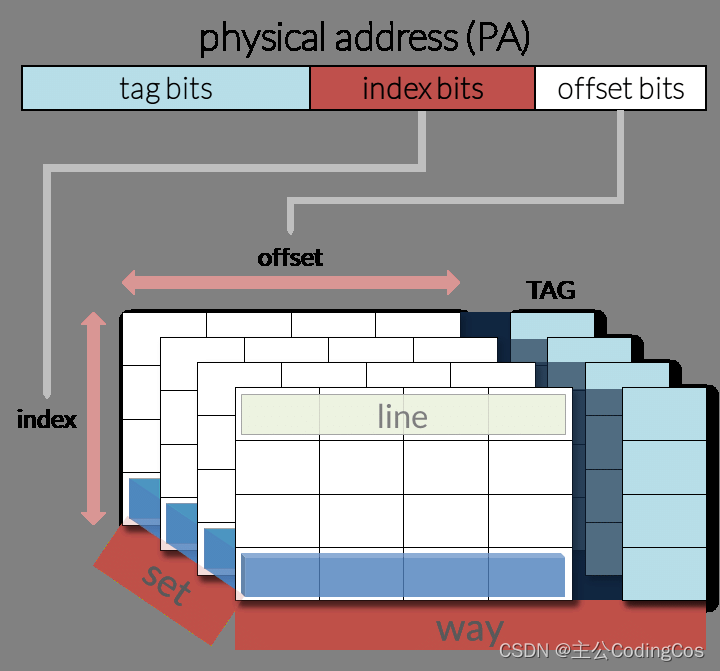

【ARM Cache 及 MMU 系列文章 6.4 -- ARMv8/v9 如何读取 Cache Tag 及分析其数据?】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 Cache Tag 数据读取测试代码 Cache Tag 数据读取 在处理器中,缓存是一种快速存储资源,用于减少访问主内存时的延迟。缓存通过存储主内存中经常访问的数据来实现这一点。为了有效地管理这些数据,缓存被组织成行(lines)或块(blocks),每个行或块包

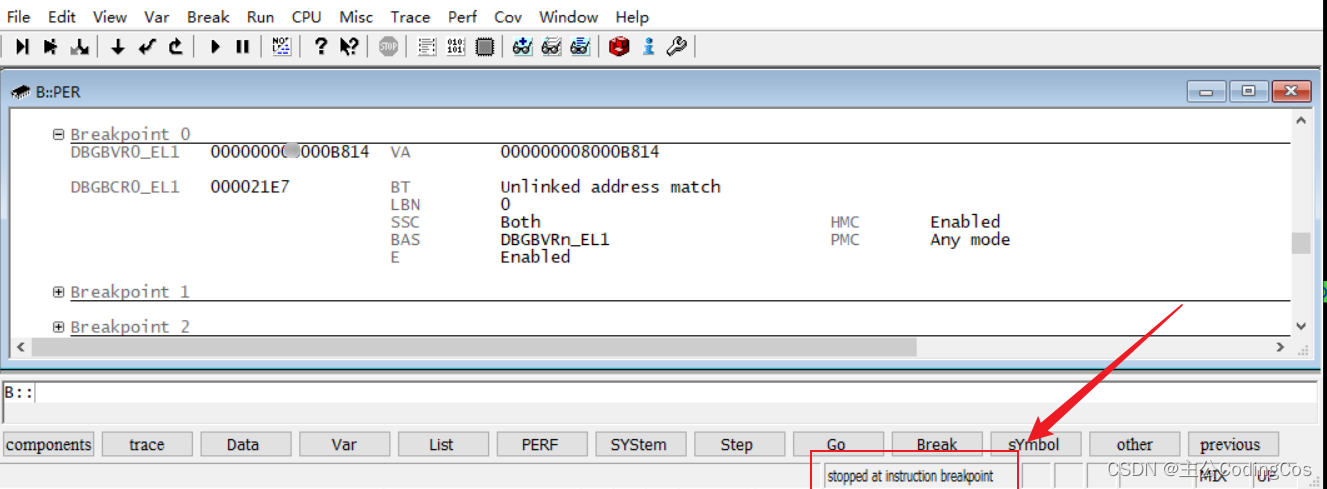

【ARM Coresight Debug 系列 -- ARMv8/v9 软件实现断点地址设置】

请阅读【嵌入式开发学习必备专栏 】 文章目录 ARMv8/v8 软件设置段带你断点地址软件配置流程代码实现 ARMv8/v8 软件设置段带你 在ARMv8/9架构中,可以通过寄存器 DBGBVR0_EL1 设置断点。这个寄存器是一系列调试断点值寄存器中的第一个DBGBVRn_EL1,其中n表示寄存器编号,对于ARMv8/9,通常可以有多个这样的寄存器,具体数量取决于实现

【ARM Cache 及 MMU 系列文章 6.3 -- ARMv8/v9 Cache Tag数据读取及分析】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 Cache Tag 数据读取测试代码 Cache Tag 数据读取 在处理器中,缓存是一种快速存储资源,用于减少访问主内存时的延迟。缓存通过存储主内存中经常访问的数据来实现这一点。为了有效地管理这些数据,缓存被组织成行(lines)或块(blocks),每个行或块包

【ARM Cache 及 MMU 系列文章 6.2 -- ARMv8/v9 Cache 内部数据读取方法详细介绍】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 Direct access to internal memoryL1 cache encodingsL1 Cache Data 寄存器 Cache 数据读取代码实现 Direct access to internal memory 在ARMv8架构中,缓存(Cach

【ARM Cache 系列文章 7.2 – ARMv8/v9 MMU 页表配置详细介绍 03 】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 表描述符 Table descriptor52-bit OA 颗粒为4KB 和16KB52-bit OA 颗粒为64KB48-bit OA 颗粒为4KB 和16KB Stage 1 和 Stage 2 介绍第一阶段(Stage 1)转换的表描述符属性字段第二阶段(Stage 2)

ARM-V9 RME(Realm Management Extension)系统架构之系统安全能力的RAS

安全之安全(security²)博客目录导读 目录 一、RAS 错误记录中的机密信息 二、RAS 错误信号 三、内存保护引擎的 RAS ARM架构安全手册提供了使用 Arm RAS 架构在处理单元(PE)和系统组件中实现 RAS 的要求。本节为本规范中描述的系统组件提供了附加规则。 一、RAS 错误记录中的机密信息 ARM架构安全手册描述了机密信息

手把手教你使用O2OA(翱途v9)开发应用平台(1)-平台初始化

今天我们就来搭建O2OA服务,并初始化基础数据。 服务器安装启动 获取O2OA O2OA平台以及其所有源码,都是可以免费获取的,要获取可运行的O2OA平台,有三种方式: 1、容器化部署 2、从官网下载可运行版本 3、下载源码,自行编译可运行版本。(后面的课程会介绍源码编译) 为了快速上手,本篇讲述前面两种2种方式 容器化部署 每一次O2OA版本发布都会制作docker 镜像,

jlink系列 v9 和 v11 调试器版本区别

纵览 csdn 居然找不到一个关于 jlink 调试器最近几个版本的基本说明,这实在是太扯了,我找了找资料版本说明如下: Jlink 用途 :嵌入式 arm 内核调试器。Jlink 截止目前硬件售卖版本 :v12。Jlink 最新固件:见官网。Jlink v9 与 v11 版本主要区别:支持的内核不同,少量比较新的内核 v9 不支持,消费类不涉及系统 90% 场景下使用 v9 即可满足日常调试,

ARM-V9 RME(Realm Management Extension)系统架构之系统安全能力的系统隔离属性

安全之安全(security²)博客目录导读 目录 一、系统隔离属性 1、系统配置完整性 1.1、时间隔离 2、关键错误的报告 一、系统隔离属性 1、系统配置完整性 MSD必须确保任何可能危及其安全保证的系统寄存器的正确性和完整性。例如,MSD必须确认内存控制器配置是一致的,以及任何控制物理地址空间映射到内存控制器的配置。 INKJLK MSD受保护寄存器(MPR)是一个存储

ARM-V9 RME(Realm Management Extension)系统架构之系统能力的内存隔离和保护

安全之安全(security²)博客目录导读 目录 一、内存隔离和保护 1、颗粒PAS过滤Granular PAS filtering 2、Cache的一致性维护 2.1 物理别名点 Point of Physical Aliasing (PoPA) 2.2 加密点 3、内存(DRAM)保护 3.1 内存加密和完整性 3.2 DRAM scrubbing 本博客探讨 RME

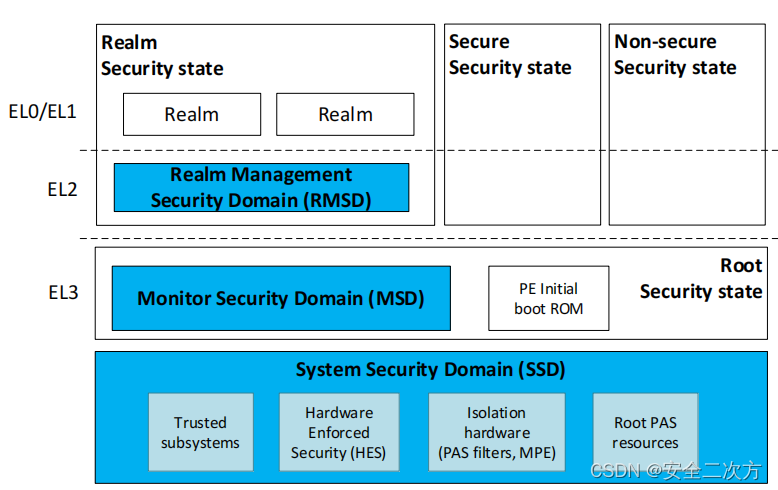

ARM-V9 RME(Realm Management Extension)系统架构之系统能力的执行隔离

安全之安全(security²)博客目录导读 目录 一、执行隔离 1、安全状态 2、安全模型 本博客探讨 RME 所需的系统能力,以保证 Arm CCA 对于 Realms 的安全性和隔离特性。 一、执行隔离 1、安全状态 RME 系统支持以下安全状态: 非安全 (Non-secure)安全 (Secure)RealmRoot 术语“requester 请求者”指能够发起访

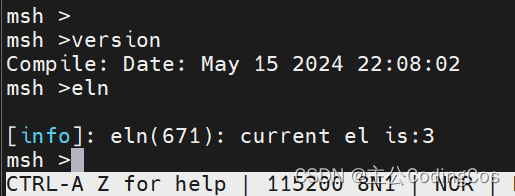

【ARMv8/v9 系统寄存器 6 -- EL 异常等级判定寄存器 CurrentEL 使用详细将介绍】

文章目录 ARMv8/v9 EL 等级获取EL 等级获取函数实现EL 等级获取测试 ARMv8/v9 EL 等级获取 下面这个宏定义是用于ARMv8/v9架构下,通过汇编语言检查当前执行在哪个异常级别(Exception Level,EL)并据此跳转到不同的标签。 异常级别是ARM架构中定义的用于隔离和保护系统资源的机制,不同的级别有不同的权限,一般来说: EL0是用户模

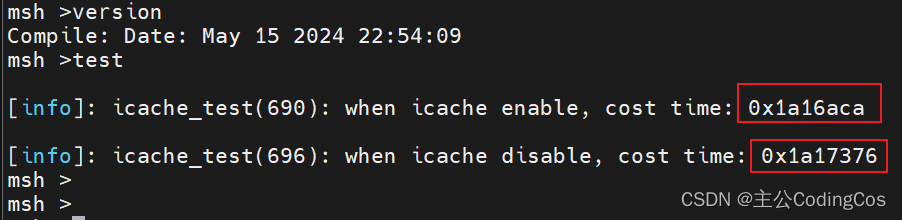

【ARMv8/v9 系统寄存器 5 -- ARMv8 Cache 控制寄存器 SCTRL_EL1 使用详细介绍】

关于ARM Cache 详细学习推荐专栏: 【ARM Cache 专栏】 【ARM ACE Bus 与 Cache 专栏】 文章目录 ARMv8/v9 Cache 设置寄存器ARMv8 指令 Cache 使能函数测试代码 ARMv8/v9 Cache 设置寄存器 关于寄存器SCTRL_EL1 的详细介绍见文章:【ARMv8/v9 异常模型入门及渐进2 - 系统控制寄存器

【ARMv8/v9 系统寄存器 5 -- CPU ID 判断寄存器 MPIDR_EL1 使用详细介绍】

文章目录 寄存器名称: MPIDR_EL1寄存器结构:主要功能和用途亲和级别(Affinity Levels)简介CORE ID 获取函数 在ARMv8-A架构中, MPIDR_EL1寄存器是一个非常重要的系统寄存器,它提供了关于处理器在其物理和逻辑配置中的位置的信息。这个寄存器的内容对于多核处理器系统或者多处理器系统中核的标识尤为重要。在ARMv9架构中, MPID

【ARMv8/v9 系统寄存器 4 -- ARMv8 通用寄存器详细介绍】

文章目录 ARMv8 通用寄存器通用寄存器X30 寄存器和链接寄存器(LR)程序计数器(PC)ARMv8 X30和PC之间的关系小结 ARMv8 通用寄存器 在ARMv9架构中(这也适用于ARMv8,因为ARMv9是其进化版本),有31个64位的通用目的寄存器(General Purpose Registers, GPRs),编号从x0到x30。这些寄存器用于日常的数据操作和

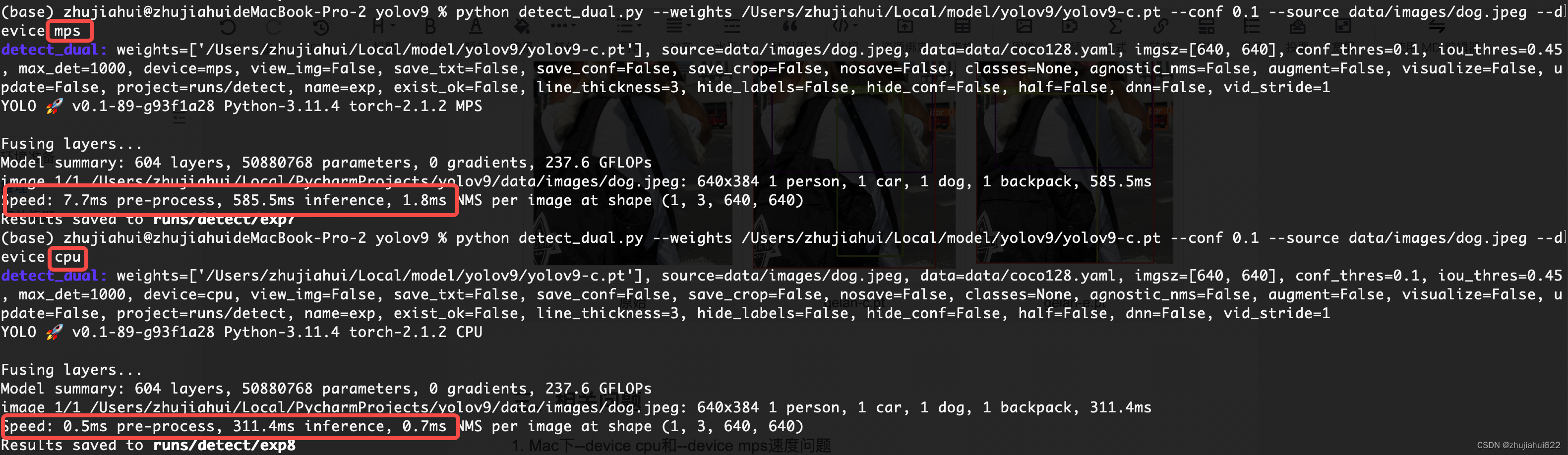

Mac YOLO V9推理测试

环境: Mac M1 (MacOS Sonoma 14.3.1) Python 3.11+PyTorch 2.1.2 一、准备工作 工程及模型下载:https://github.com/WongKinYiu/yolov9 git clone https://github.com/WongKinYiu/yolov9.git 克隆后安装相关依赖(没啥依赖好装的)

【ARMv8/v9 系统寄存 3 -- system counter CNTPCT_EL0】

文章目录 ARMv8/v9 system countersystem counter读取函数实现 ARMv8/v9 system counter 所有使用Arm处理器的系统中都会包含一个标准化的通用定时器(Generic Timer)框架。这个通用定时器系统提供了一个系统计数器(System Counter)和一组定时器(Timer)。其结构类似下图: 系统计数器是全局唯一

【ARMv8/v9 常见汇编指令学习 6.1 - armv8 右移指令 LSR 详细介绍】

请阅读【嵌入式开发学习必备专栏 】 文章目录 armv8 右移指令 LSR语法示例注意事项 armv8 右移指令 LSR 在ARMv8架构中,lsr(Logical Shift Right)指令是一种逻辑右移指令,用于将一个寄存器中的数值向右移动指定的位数。逻辑右移操作会从左侧填充0,这与算术右移(asr,Arithmetic Shift Right)不同,后者会根

人大金仓(KingbaseES V9)的Python环境的配置和基本使用

人大金仓(KingbaseES V9)提供了Python的驱动,可以通过Python来访问人大金仓数据库,不过这个配置并不算十分友好。 要使用这个Python驱动,除了要根据架构来下载对应的版本之外,还需要从KingbaseES的部署中拷贝一些lib文件出来。为了简化这些操作,我写一个脚本对自动化整个过程,并且把相关的文件都放在ksycopg2/一个目录下,这个脚本如下(download_psy