v0专题

v0.dev快速开发

探索v0.dev:次世代开发者之利器 今之技艺日新月异,开发者之工具亦随之进步不辍。v0.dev者,新兴之开发者利器也,迅速引起众多开发者之瞩目。本文将引汝探究v0.dev之基本功能与优势,助汝速速上手,提升开发之效率。 何谓v0.dev? v0.dev者,现代化之开发者工具也,旨在简化并加速软件开发之过程。其集多种功能于一体,助开发者高效编写、测试及部署代码。无论汝为前端开发者、后端开发者

Vercel 的 AI 工具 V0.dev:如何使用它?

几个月前,Vercel 宣布推出了 V0.dev,这是一款专为开发人员和设计师设计的工具,能够使用 AI 生成 React 代码。最初,V0.dev 对外开放时采用了邀请制,但如今拥有 Vercel 帐户的任何人都可以访问并使用它。 这些工具填补了开发人员和设计人员之间的空白,并为许多公司在推出项目和产品时节省了时间。在这篇文章中,我将分享 V0.dev 的价值、它是如何运作的,以及开源对此类项

04_led_water_flow_v0 流水灯

04_led_water_flow_v0 流水灯和跑马灯都是一种常见的LED灯效,它们在灯光的变化方式上有所不同。 流水灯是一种灯效模式,LED灯在一定的时间间隔内依次点亮或熄灭,形成像水流一样的效果。而跑马灯则是LED灯在一定的时间间隔内依次从左向右或从右向左依次点亮或熄灭,形成像跑马一样的效果,每个时刻只有一个灯亮,其他灯都熄灭。 更新 使用dip开关控制跑马灯的速度和方向 知识点:

03_led_horse_run_v0 跑马灯

03_led_horse_run_v0 在Verilog中实现跑马灯通常涉及到使用一个计数器来控制LED灯的亮灭顺序。 跑马灯是一种常见的电子显示方式,它通过控制多个LED灯的顺序点亮,形成一种动态的视觉效果,看起来就像灯在“跑”一样。 知识点: 移位寄存器 module led_horse_run #(parameter CLK_FREQ = 50*1000*1000)(input

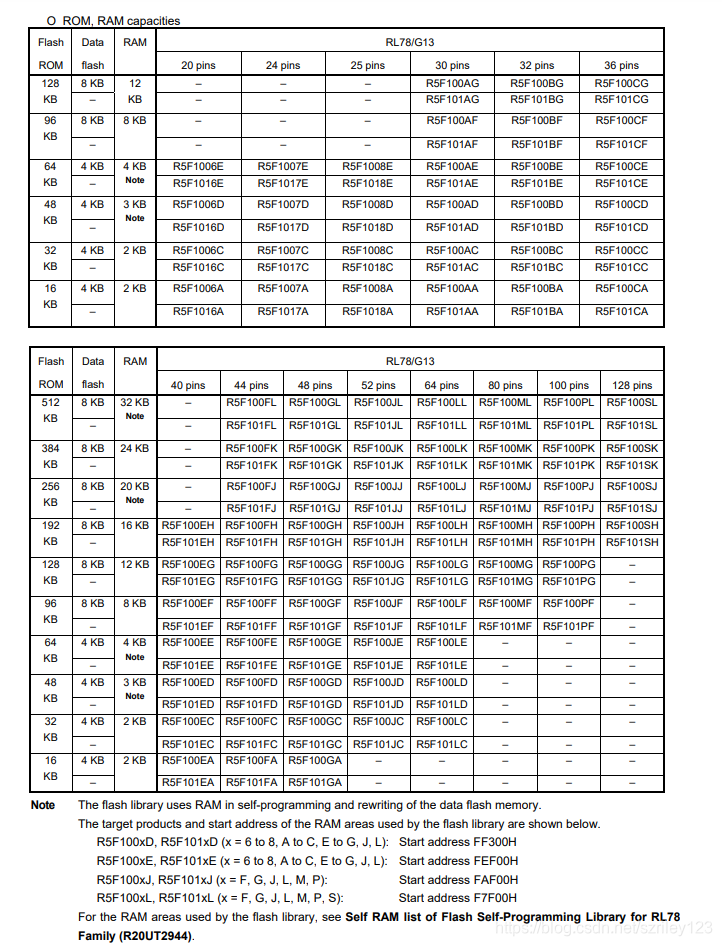

R5F100AAA100SP#V0低功耗16位微控制器MCU RENESAS

描述 R5F100AAA100SP#V0 R5F100AAA Renesas 16位微控制器 - MCU RL78 / G13 RENESAS MCU 真正的低功耗平台(低至66μA/ MHz,RTC + LVD为0.57μA),1.6 V至5.5 V工作电压, 16至512 KB闪存,32 MHz时41 DMIPS,适用于通用应用 FAE:137237 14328 超低功耗技术 VDD =

R5F100PLAFB#V0 16位微控制器超低功耗RENESAS

描述 R5F100PLAFB#V0 RL78/ G13 RENESAS MCU 真正的低功耗平台(低至66μA/ MHz,RTC + LVD为0.57μA),1.6 V至5.5 V工作电压, 16至512 KB闪存,32 MHz时41 DMIPS,适用于通用应用 特征 超低功耗技术 -VDD= 1.6至5.5 V的单电源电压 -HALT模式 -STOP模式 -SNOOZE模式 RL78 C

R5F100PJAFB#V0低功耗微控制器

R5F100PJAFB#V0 RL78 / G13 RENESAS MCU 真正的低功耗平台(低至66μA/ MHz,RTC + LVD为0.57μA),1.6 V至5.5 V工作电压, 16至512 KB闪存,32 MHz时41 DMIPS,适用于通用应用 特征 超低功耗技术 VDD =单电源电压1.6至5.5 V.HALT模式停止模式SNOOZE模式 RL78 CPU核心 具有3

[linux]undefined reference to `__gxx_personality_v0'

linux程序 #include #include #include int count=0; void ctrl_c_count(int); int main(void) { int c; void (*old_handler)(int); old_handler=signal(SIGINT,ctrl_c_count); while((c=getchar()!=' '))

V0第 第13节 数组类型

1.动态数组 与之前的定长数组相比,SV提供了可以重新确定大小的动态数组动态数组在声明时需要使用[],这表示不会在编译时为其制定尺寸,而是在仿真运行时来确定动态数组一开始为空,需要使用new[]来为其分配空间 int dyn[],d2[];//声明动态数组initial begindyn = new[5]; //分配5个元素foreach (dyn[j]) dyn[j] = j; //对元素

V0 第12节 数组操作

1. 非组合型unpacked 对于Verilog,数组经常会被用来做数据存储,例如reg[15:0] RAM [0:4095]SV 将Verilog这种声明数组的方式称为非组合型声明,即数组中的成员之间存储数据都是互相独立的Verilog也不会指定软件去如何存储数组中的成员wire[7:0] table[3:0]SV保留了非组合型的数组声明方式,并且扩展了允许的类型,包括event,logic

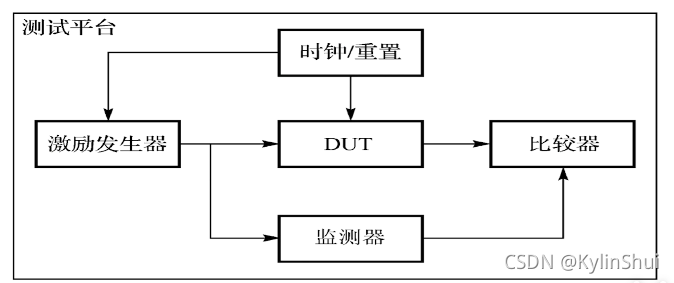

V0 第11节 验证环境组件

1. 激励发生器 Simulator (激励发生器)是验证环境的重要部件,在一些场合中,它被称为driver(驱动器)、BFM(bus function model,总线功能模型),behavioral(行为模型) 或者 generator(发生器)Simulator的主要职责是模拟与DUT相邻设计的接口协议,只需要关注如何模拟接口信号,使其能够以真实的接口协议来发送激励给DUTSimulato

V0 第10节 硬件设计描述

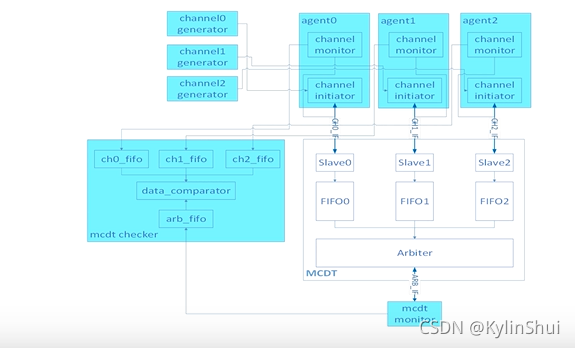

1. MCDF 简介 遵循硬件设计描述的方式,介绍它的结构、功能、寄存器和时序熟悉硬件描述的方式,也是进入验证领域的一项基本技能多通道数据整形器(MCDF, multi-channel data formatter),它可以将上行uplink多个通道数据经过内部的FIFO,最终以数据包data packet的形式送出上行数据和下行数据的接口协议不同多通道数据整形器也有寄存器的读写接口,可以支持更

V0 第9节 验证环境结构

1. 验证环境结构 测试平台(testbench)是整个验证系统的总称它包括验证结构中的各个组件、组件之间的连接关系、测试平台的配置和控制从系统的意义来讲,它还包括编译仿真的流程、结果分析报告和覆盖率量化我们主要关注验证平台的结构和组件部分,他们可以产生设计所需要的各种输入,也会在此基础上进行设计功能的检查 2. 测试平台结构图 各个组件之间是相互独立的验证组件与设计之间需要连接验证组件

V0第7节 字符串类型

1. 字符串类型 Verilog语言对于字符串的处理手段非常有限SV引入了string 类型用来容纳可变长度的字符串字符串类型变量的存储单元为byte类型字符串类型变量长度为N时,其字符成员索引值为从0到N-1不同于C语言,字符串结尾没有空字符 “\0"字符串的内存是动态分配的,用户无需担心内存空间管理 2. 字符串内建方法 str.len();返回字符串的长度str.putc(i, c);

V0 第 6 节自定义类型

1.自定义类型 通过用户自定义类型,以往Verilog的代码将可以通过更少的代码来表示更多的功能用户自定义类型使得代码的可读性更好通过typedef来创建用户自定义类型通过enum来创建枚举类型通过struct来创建结构体类型Verilog语言无法提供方便的特性来使得用户扩展变量和线网类型SV则提供了特性使得用户可以构建更高抽象层的数据类型定义了新的数据类型,就可以利用该类型声明变量 1.1

V0 第5节 数据类型

1. Verilog的数据类型 Verilog语言提供两种基本的数据类型, 变量类型variables和线网类型nets,这两种类型都是四值逻辑,即可表示0、1、X和Z值例如reg,integer和time等变量类型可以用来存储组合逻辑或者时序逻辑的值例如wire,wor,wand和其它线网类型用来连接硬件模块,以及提供特殊的线网驱动解决方案 1.1 Verilog线网类型 线网用于建模硬件

V0 第4节 SV及UVM概述

1. SystemVerilog发展历史 SV 是IEEE 1364-2005 Verilog标准的扩展此扩展包含了用来实现可综合设计的设计语言特性,也包含了用来对大型设计做验证的验证语言特性SV是用来建议一种新的硬件描述和验证语言(HDVL,Hardware Description and Verification Language)SV通过一种统一的语言来帮助工程师对大型复杂硬件系统进行建模

VT-VRPA2-1-1X/V0/T5控制4WRE6比例方向阀放大板

带阀芯位移反馈不带集成式放大器比例方向阀控制放大器,替代力士乐同型号产品,可以完全互换使用;适用于控制力士乐系列带电位置反馈的4WRE6通径和4WRE10通径2X系列比例方向阀;0~+10V、4~20mA指令控制信号任意可选;直接安装在35mm导轨上,方便连接 控制4WRE6...-2X系列比例方向阀,VT-VRPA2-1-1X/V0/T1,VT-VRPA2-1-1X/V0/T5,安装支

VT-MRPA1-151-1X/V0/0控制2FRE16模块式模拟放大器

适用于控制带有电气位置反馈的直动式比例减压阀(DBETR- 1X 类型)或带有电气位置反馈的比例流量控制阀(2FRE... 类型);控制值输入 ±1 0 V(差动输入); 可分别调节“上/下”斜坡时间的斜坡函数发生器;零位电位计;振幅衰减;选通输入;电源的极性保护;电源带直流/直流转换器,不带提高零点