nios专题

NIOS Eclipse突然报错:No rule to make target `/system.h

NIOS Eclipse突然报错:No rule to make target `/system.h 今天打开NIOS Eclipse编译昨天完好的工程,发现报错。我就纳闷了,代码没有修改,编译结果报错 控制台中problems选线中显示: No rule to make target `/system.h 控制台中的console选项中显示: **** Build of config

【INTEL(ALTERA)】Nios® II EDS 是否在 Windows 10 上受支持?

目录 说明 解决方法 说明 在 readme.txt 中提到 Windows 10 不支持Nios II EDS 标准版。/content/dam/support/us/en/programmable/kdb/others/download/os-support/readme-qp171.txt 但是,在Nios II版本中,它得到了支持。https://www.altera.co

【INTEL(ALTERA)】Nios® II无法使用基于 Ubuntu 18.04.5 的 WSL 进行构建

现象 在使用 Ubuntu 18.04.5 构建 WSL 的Nios® II处理器时,任何英特尔® Quartus® Prime 软件版本都可能会看到此问题。 原因 这是因为在 Nios® II Command Shell 中运行命令 “wslpath -u .”时返回值不同。 正常工作:命令返回”。故障:命令返回“wslpath:”。”

【INTEL(ALTERA)】采用 JTAG 频率为 24MHz 或 16Mhz 的非流水线Nios® V/m 处理器,niosv-download 失败

说明 在英特尔® Quartus® Prime Pro Edition 软件 23.3 版及更高版本中将 Nios® V 处理器软件下载到非流水线Nios® V/m 处理器时,可能会出现此问题。 这是由于处理器限制,仅影响非流水线Nios® V/m 处理器。 以下其他处理器不受此限制的影响: 管道式 Nios® V/m 处理器Nios® V/g 处理器 解决方法 要变通解决此问题,

基于NIOS-II软核流水灯和串口通信实现

文章目录 一、创建工程二、系统设计1. 在 “component library” 标签栏中找到 “Nios II Processor” 后点击 Add2. 在 ”Component Library” 标签栏中的查找窗口输入 jtag 找到 ”JTAG UART ”,然后点击 Add3. 添加片上存储器 On-Chip Memory(RAM)核4. 查找窗口输入 pio 找到 ”PIO” 后

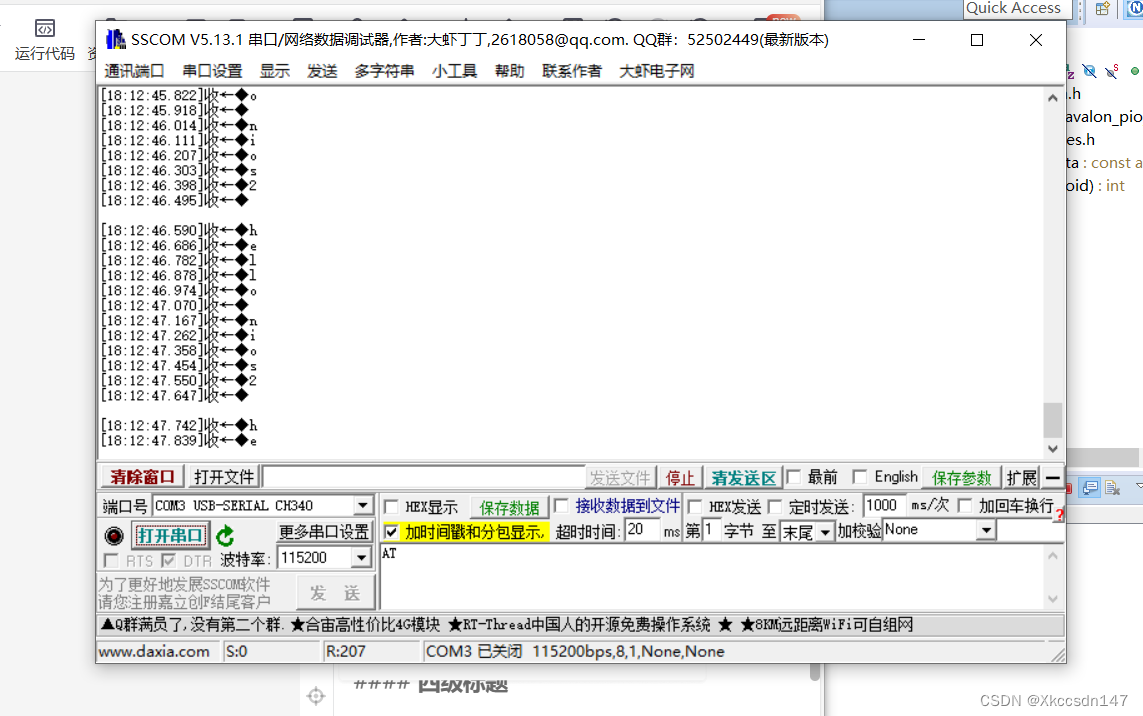

NIOS II实现LED流水灯以及串口输出(DE2-115开发板)

NIOS II实现LED流水灯以及串口输出(DE2-115开发板) 前言什么是Qsys?什么是NIOSII?注意事项1、管脚配置2、配置NIOSII时的连接3、注意中断配置好后是这样的4、注意名称的配置5、设置双功能引脚 NIOS II的报错代码以及效果演示流水灯输出到电脑串口助手 前言 具体的软件和硬件配置流程看下方的博客很详细,我主要讲一下这些博客没说到的部分和我做的过程

Nios-II编程入门实验

文章目录 一 Verilog实现流水灯二 Nios实现流水灯2.1 创建项目2.2 SOPC添加模块2.3 SOPC输入输出连接2.4 Generate2.5 软件部分2.6 运行结果 三 Verilog实现串口3.1 代码3.2 引脚3.3 效果 四 Nios2实现串口4.1 sopc硬件设计4.2 top文件4.3 软件代码4.4 实现效果 五 参考资料六 总结 一. 实验目

基于Nios软件实现流水灯+串口输出

基于NIOS-II软核实现流水灯+串口输出 引言: 在现代电子设计领域,FPGA(现场可编程门阵列)因其灵活性和并行处理能力而成为实现复杂数字系统的首选平台。Nios II,作为Altera(现为Intel旗下)提供的软核处理器,为FPGA提供了强大的处理核心,使得FPGA的应用领域得以进一步扩展到嵌入式系统设计。 · 本次实验的核心目标是利用Nios II软核处理器的软件编程能力,结合硬

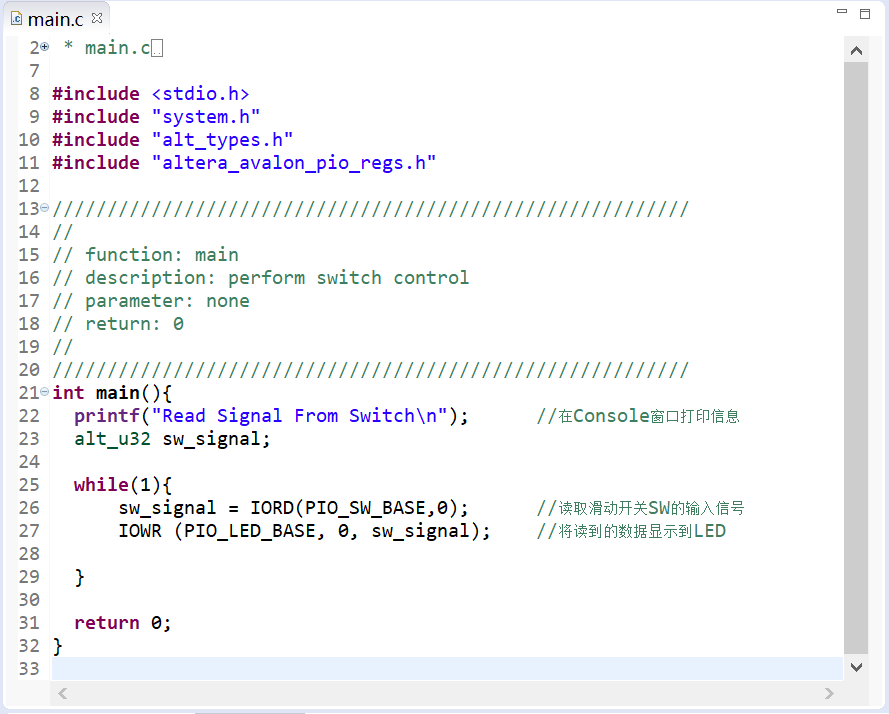

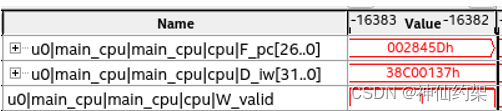

第9篇:创建Nios II工程之读取Switch的值<二>

Q:上一期我们完成了Quartus硬件工程部分,本期我们创建Nios II软件工程这部分。 A:创建完BSP和Nios II Application之后,在source文件main.c中添加代码:system.h头文件中新增了Switch PIO IP的硬件信息,包括基地址、数据位宽等;altera_avalon_pio_regs.h头文件定义的两个读写函数IORD(base, regnum)

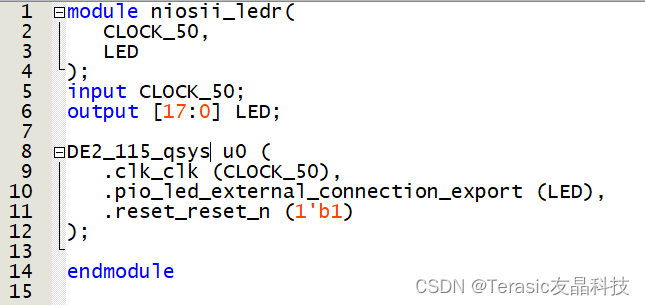

第6篇:创建Nios II工程之控制LED<一>

Q:还记得第1篇吗?设计简单的逻辑电路,控制DE2-115开发板上LED的亮与熄灭,一行Verilog HDL的assign赋值语句即可实现。本期开始创建Nios II工程,用C语言代码控制DE2-115开发板上的LED实现流水灯效果。 A:在前面我们创建的Hello_World工程的Platform Designer系统基础上添加一个PIO核,参数设置为18位和单向输出模式,表示DE2-115

第8篇:创建Nios II工程之读取Switch的值<一>

Q:本期我们再添加一个PIO组件设为输入,创建Nios II工程读取输入值显示在LED上。 A:在前2期创建的控制LED工程的Platform Designer系统基础上再添加一个PIO核,参数设置为18位和单向输入模式,表示DE2-115开发板上的18个滑动开关,这样可以分别对应18个红色LED。 Generate新的系统,并在.v顶层文件实例化系统,分配引脚最后编译Quartus硬

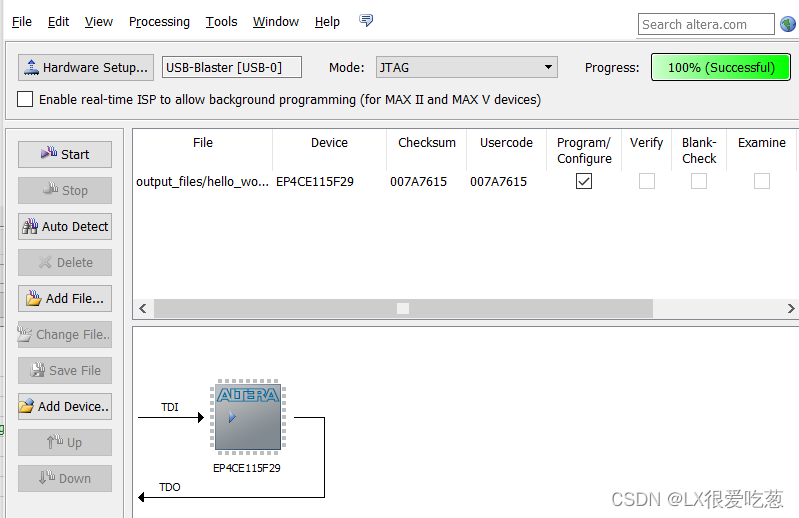

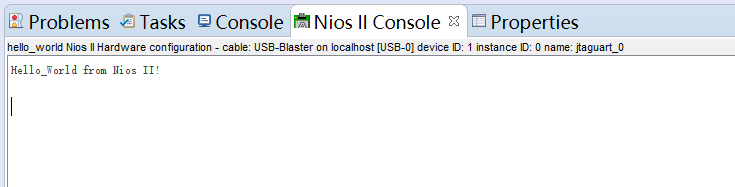

第5篇:创建Nios II工程之Hello_World<四>

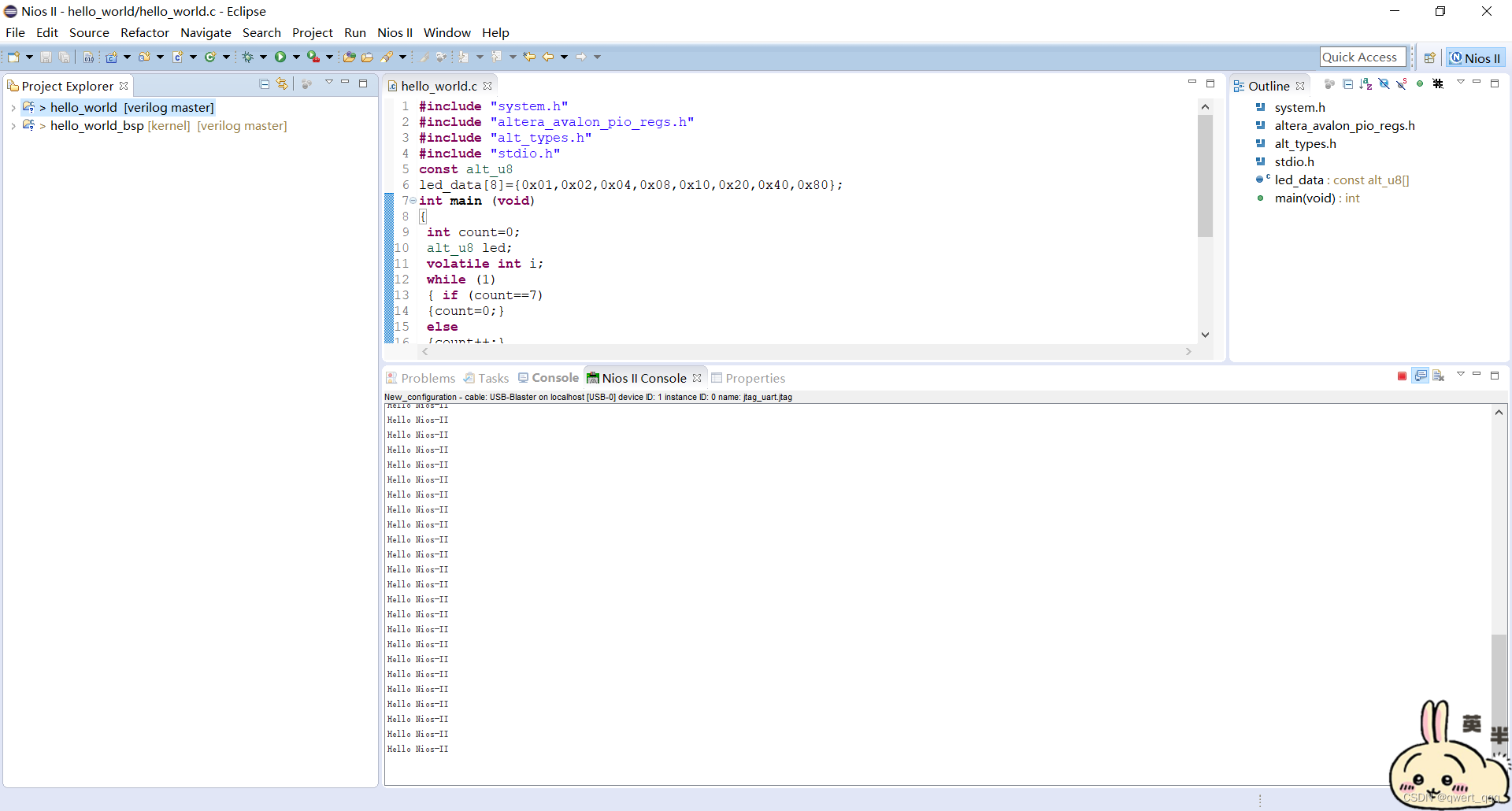

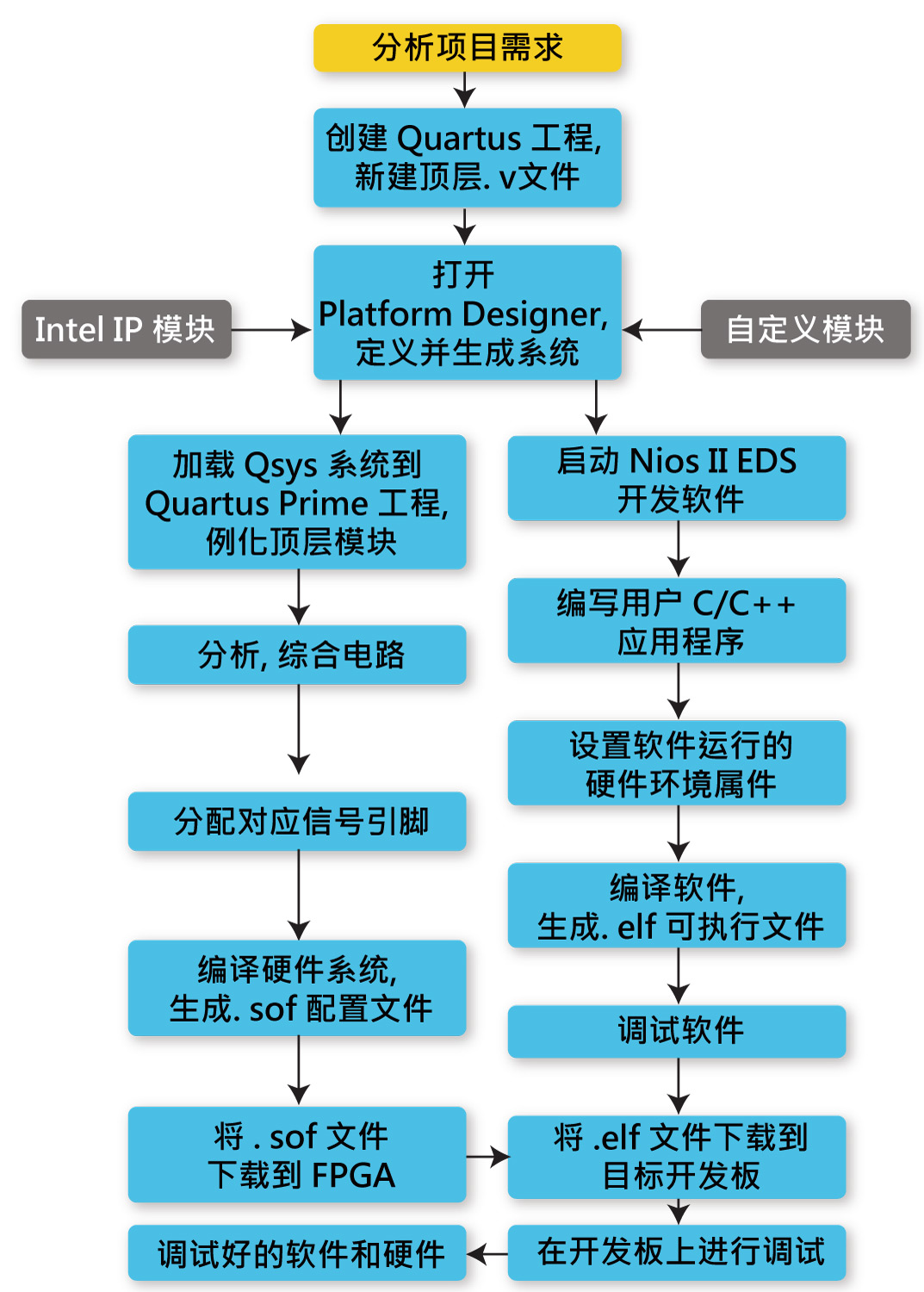

Q:最后我们在DE2-115开发板上演示运行Hello_World程序。 A:先烧录编译Quartus硬件工程时生成的.sof文件,在FPGA上成功配置Nios II系统;然后在Nios II Eclipse窗口右键点击工程名hello_world,选择Run As-->Nios II Hardware打开Run Configurations窗口,硬件Connection显示连接成功后即可点击R

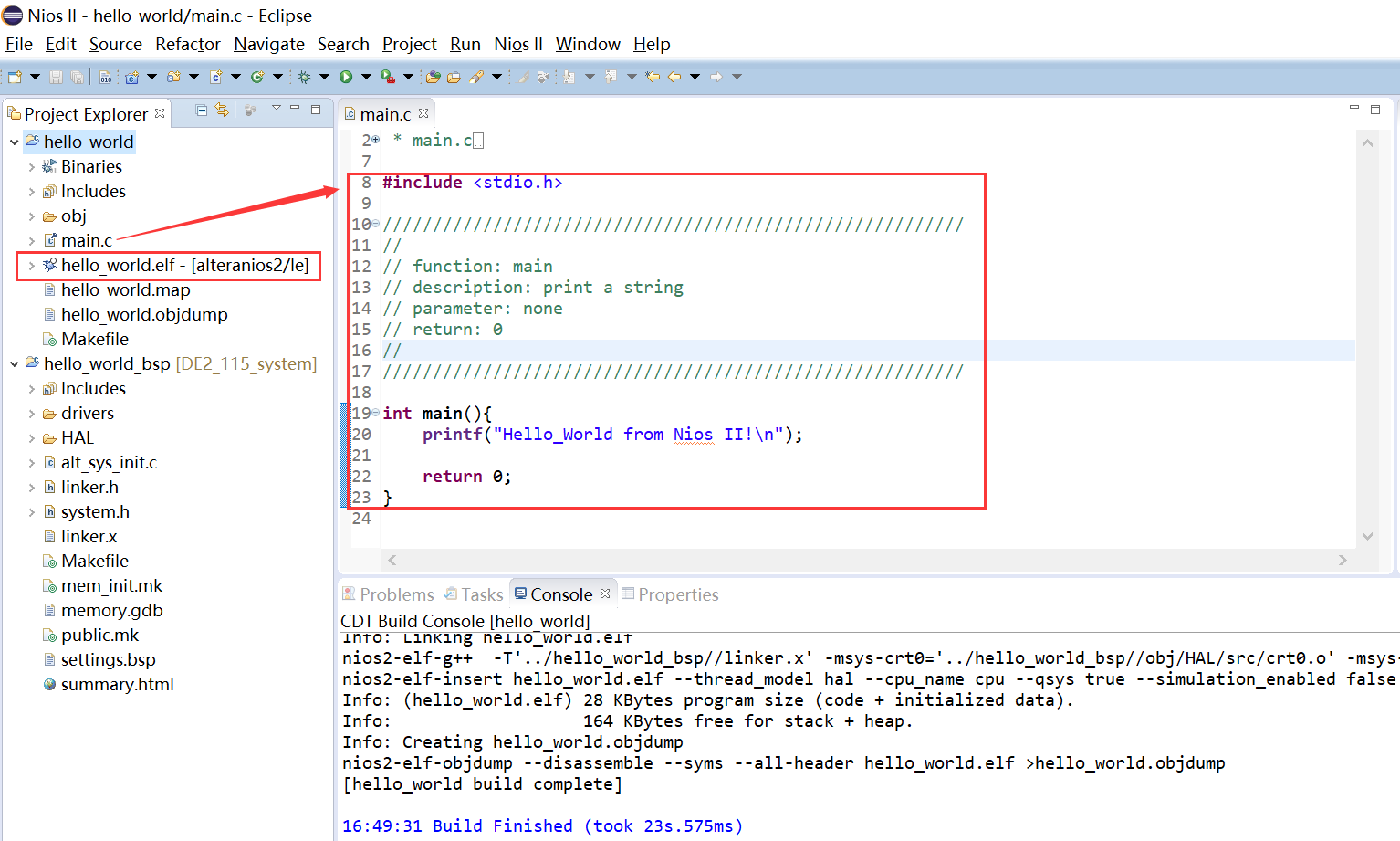

第4篇:创建Nios II工程之Hello_World<三>

Q:接着我们再来完成Nios II软件工程设计部分。 A:从Quartus Tools选择Nios II Software Build Tools for Eclipse,打开Nios II SBT软件,Workspace指定到hello_world工程的software文件夹路径;再从File-->New-->Nios II Application里打开Nios II Application创

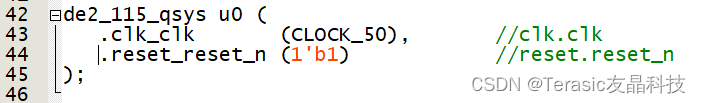

第3篇:创建Nios II工程之Hello_World<二>

Q:上一期介绍完基本设计流程和实验原理,接着我们完成系统硬件设计部分,包括Platform Designer系统及Quartus工程。 A:依次搜索并添加Nios II Processor、JTAG UART、On-Chip Memory和System ID IP组件,连接各组件并Assign Base Address后的Platform Designer系统如下图所示,本次实验各IP组件相关参

2.3 NIOS II外围组件

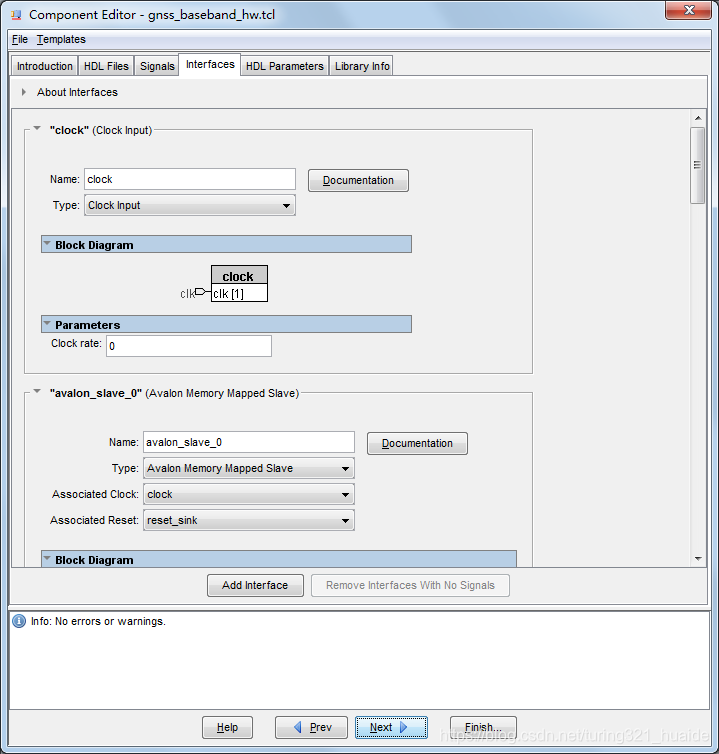

\qquad 在AGRS_GP_1项目的SOPC系统中,挂连在NIOS II CPU上的特定(非通用)外围组件包括常见的PIO (led_pio)、SPI (spi_max2769_1, spi_max2769_2)、以及UART (uart232_a, uart232_b)组件,本节对它们不予赘述。本节只对涉及时钟域管理/约束、软件速度优化的组件以及专用组件进行讨论,包括: 紧耦合存储器组件

2.2 NIOS II CPU和软件开发环境

\qquad 本节包括在AGRS_GP_1项目中创建NIOS II CPU和配置有关选项的讨论,并对NIOS II软件开发环境进行了简介。 2.2.1 NIOS II CPU创建 \qquad HD-GR接收机中唯一的处理器是作为软核在FPGA (U1)内部运行的Altera NIOS II CPU。这个CPU以及它的外围设备使用向导工具SOPC Builder构建。SOPC Builde

第58篇:创建Nios II工程之Hello_World<四>

Q:最后我们在DE2-115开发板上演示运行Hello_World程序。 A:先烧录编译Quartus硬件工程时生成的.sof文件,在FPGA上成功配置Nios II系统;然后在Nios II Eclipse窗口右键点击工程名hello_world,选择Run As-->Nios II Hardware打开Run Configurations窗口,硬件Connection显示连接成功后即可点击R

第55篇:创建Nios II工程之Hello_World<一>

Q:本期我们开始介绍创建Platform Designer系统,并设计基于Nios II Professor的Hello_world工程。 A:设计流程和实验原理:需要用到的IP组件有Clock Source、Nios II Professor、On-Chip Memory、JTAG UART和System ID外设。Nios II Processor是整个系统的核心,其他组件都会通过Avalo

Nios II terminal: exiting due to ^D on remote

【问题原因】:在nios下调试程序时,会出现如下错误:nios2-terminal: exiting due to ^D on remote 一直不知道原因,在网上找了一下也没有具体的解决方案。经过实验发现是console里如果出现类似ctrl-D的字符是,会迫使nios2-terminal执行quit中断。使系统退出调试状态。 【解决办法】:对需要输出的变量和字符串进行清理操作,

【INTEL(ALTERA)】带有浮点单元 (FPU) Nios® V/g 处理器在 英特尔® Cyclone10 GX 设备中执行不正确的浮点运算

说明 由于 英特尔® Quartus® Prime Pro Edition 软件版本 23.3 存在一个问题,当使用 Nios® V/g 处理器并在 英特尔® Cyclone® 10 GX 设备中启用 FPU 时,浮点运算无法按预期进行。 Nios® V/g 处理器 – 启用浮点单元 解决方法 请勿在 英特尔® Cyclone®Nios 10 GX 设备中启用 V/g 中的硬件

【INTEL(ALTERA)】为什么Nios® V 应用程序项目构建失败,并且观察到“找不到 -lstdc++”消息?

说明 由于 xPack GNU RISC-V 嵌入式 GCC v10.1.0-1.1 工具链 (Windows Build) 中缺少多lib arch/abi-to-directory 映射,在 Windows 中使用命令“make -C<Application project build directory>” 在 Windows 中构建Nios® V/m 处理器英特尔 FPGA IP设计应用

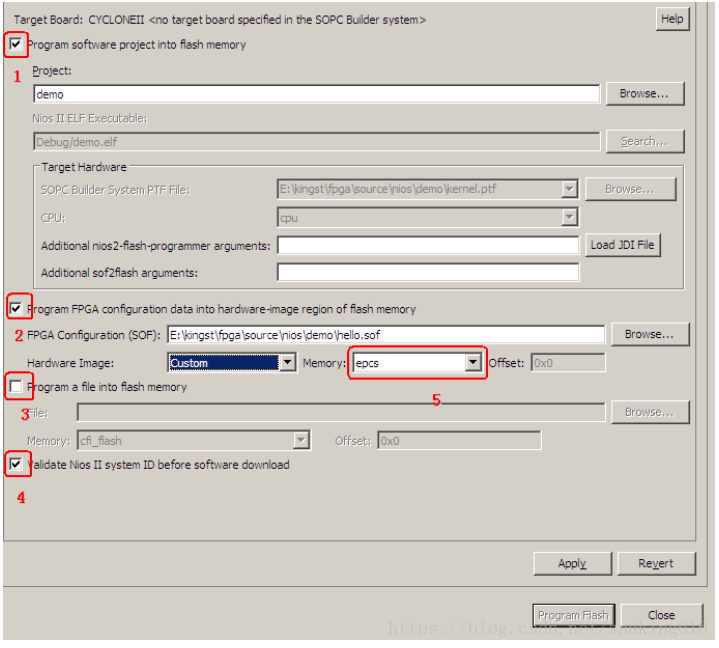

Nios II 程序固化(如何下载elf文件)

在调试Nios程序阶段,通常需要先将配置文件(*.sof)通过 JTAG 下载刡到FPGA 中,接着在Nios II IDE窗口中,右击工程名,选择Debug as -> Nios II hardware 来实现内核软件的调试,调试中的代码在开发板再次上电后会丢失,如何固化Nios程序呢,详细步骤如下: 1. 下载配置文件(*.sof) 首先,需要将 usb b

【INTEL(ALTERA)】 quartus SignalTap 逻辑分析器 – Nios® II 插件 无法检测 Nios® II/f 处理器内核

说明 使用 Nios® II 插件将 Nios® II/f 处理器内核节点添加到 SignalTap 逻辑分析器时,在 英特尔® Quartus® Prime Pro Edition 软件 23.3 版中可能会出现此问题。 错误消息: 无法完成“添加带插件的节点”命令,因为在当前设计中找不到所选 IP。 这是由于Nios® II插件中的软件问题造成的。 解决方法 1. 使用以下指

NIOS II EPCQ FLASH启动过程要点 NIOS II BOOT LOADER/COPIER

从EPCQ FLASH启动nios,并自动运行应用程序(以hello_world为例),按照bootloader(altera称之为boot copier)是否为自定义的,分为两种方法: 一,bootloader不是自定义的,是通过nios SBT软件自动生成的,该方法即 intel altera Embedded Design Handbook中5.2.3.4所述方法。 二,由于需要在多个

FPGA片上RAM、片上ROM Nios 程序不起作用的解决方法

ctrl + B 编译Nios工程 将 Nios software 的 meminit.qip onchip_rom.hex onchip_ram.hex meminit.spd 文件拷贝到FPGA目录下,再编译FPGA能起作用 Nios设置: reset 设置为 ROM 异常设置为 RAM 无优化