mpsoc专题

ZYNQ MPSOC FPGA 仿真 教程

1. **FPGA与MPSOC**: FPGA (Field Programmable Gate Array) 是一种可以通过编程配置的集成电路,适用于各种应用和功能。MPSOC (Multi-Processor System on Chip) 是集成了多个处理器(通常是微处理器)的系统芯片,用于处理复杂的应用,如图像处理、网络通信等。 2. **仿真与分析**: - **仿

【ZYNQ MPSoC开发】lwIP TCP发送用于数据缓存的软件FIFO设计

设计背景 任务是在ZYNQ的PS上使用裸机运行lwIP协议栈使用TCP把PL端通过AXI DMA传来的将近100K采样率的ADC数据发送出去,但由于数据带宽很大,有853.3mbps,所以在每一次AXI DMA简单传输结束后,lwIP未必有足够的发送buffer立即把数据发送走,如果是发送完再进行下一次简单传输的思路,则会很大地限制了整个系统的带宽,一个简单的思路是每次传输完成后判

petalinux,Zynq UltraScale+ MPSoC;WARNING: Failed to load PMUFW, doesn't exist in pre-built.

petalinux-package --pmufw ./images/linux/pmufw.elf 这个参数貌似没有生效; 解决办法: cp images/linux/pmufw.elf ./pre-built/linux/images/

【ZYNQ MPSoC开发】PS裸机多核程序的固化

写在前面 多核程序的固化总体操作流程与单核程序固化相同,针对本文中的一些操作,大家如果有不清楚的,可以参考我之前写的单核固化的博客。 共通前置步骤 这是区别于单核固话的主要不同之处。以我的程序为例,我用到了两个核心,分别跑在A53_0和A53_1上,结构如下图所示: 1,首先对各个核心的应用程序都build好,生成.elf文件。

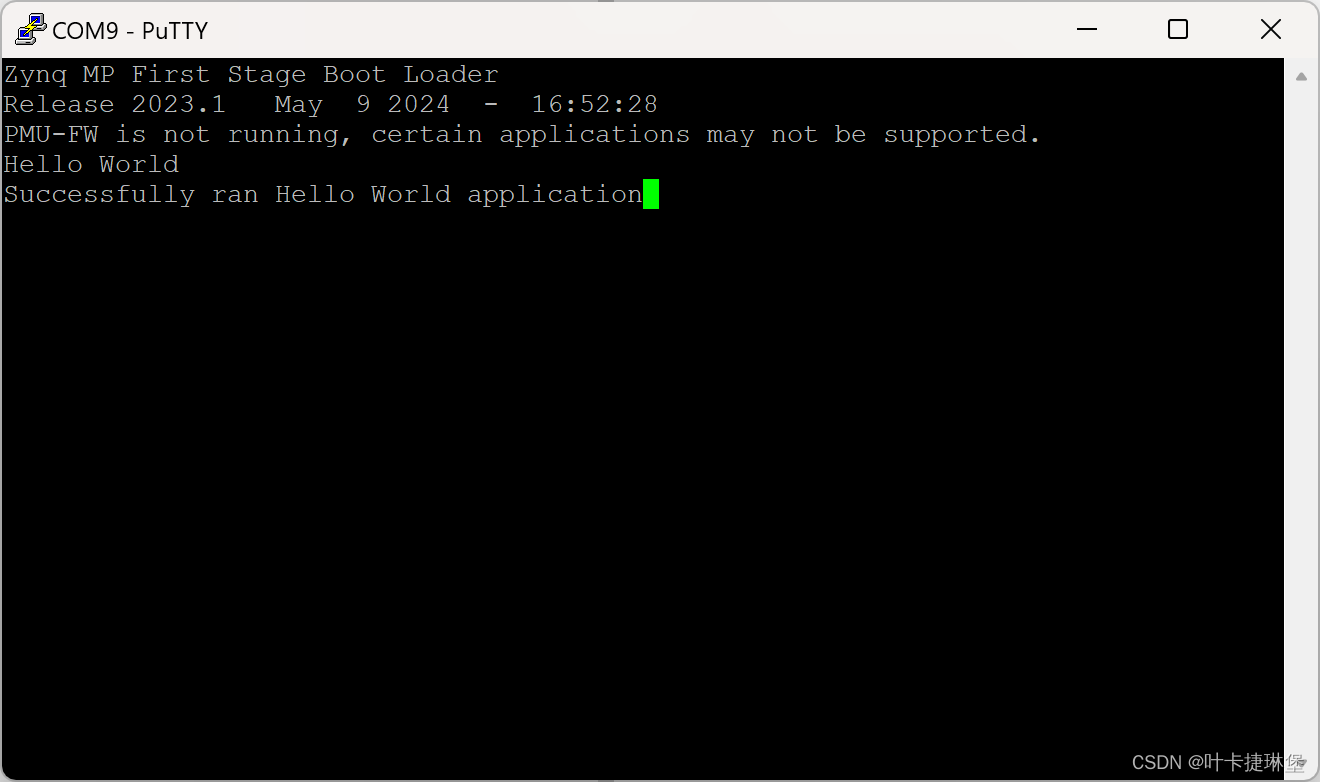

ZYNQ MPSoC zcu102 PS端运行helloworld

文章目录 一、参考资料二、需要注意的步骤三、运行结果 一、参考资料 1.zcu102 zynq Mpsoc uart hello world——CSDN博客 2.zcu102自学 —— 第一个实验 (纯PS 串口打印 Hello world)——CSDN博客 3.【02】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—MPSoC开发之Viva

Xilinx SDSoC支持16nm ZynqUltrascale+ MPSoC软件定义编程

全可编程技术和器件的全球领先企业赛灵思公司 (Xilinx, Inc. (NASDAQ:XLNX)) 今天宣布推出 SDSoC™开发环境2016.1版,支持Zynq系列SoC和MPSoC 使用 C和C++语言进行软件定义编程,并支持近期新推出的16nm Zynq® UltraScale+™ MPSoC。此外,该新版环境还凭借系统级特性分析工具,将编译时间缩减一半,从而实现了生产力的大幅提升。

【AMD Xilinx】Avnet高性价比MPSoC评估板-ZUBoard(1):基本资料和开发流程

【AMD Xilinx】Avnet高性价比MPSoC评估板-ZUBoard(1):基本资料和开发流程 一、概述1. 基本介绍2. PCB外设示意图3. 硬件框图 二、开箱体验1. 接线1)电源:15V2)串口3)网线4)扩展板5)TF卡6)usb host 2.开关机1)按SW7启动2)关机:长按SW7十秒3)复位:SW6 3. 启动模式 三、FPGA开发1. 测试时可以用来简单控制的外设2

Hobbit玩转Zynq MPSoC系列之3:HDMI输入+DP显示

Xilinx官方提供了Zynq MPSoC的应用例程,包括Base Trd和VCU Trd,从Vivado硬件到Petalinux工程介绍的很详细,源代码也都是开源的。为了做到一个工程覆盖所有设计,这些Trd的代码极其规划化和模块化,包罗万象,将所有的功能都放到了一个工程里边。拿Base Trd为例,上层应用代码就足足有12000行代码,通过指令或者QT GUI去操作控制,如下图所示,可以说是

基于 KU115+MPSOC 的 4 路 3GHz 瞬时带宽数字基带信号合成板(VPX630+FMC131)

VPX630-1 是一款基于 6U VPX 总线架构的 4 路 3GHz 带宽数字基带信号合成板,该平台采用一片 Xilinx 的 Kintex UltraScale 系列FPGA(XCKU115)作为主处理器,完成复杂的数据采集、回放以及实时信号处理算法。采用一片带有 ARM 内核的高性能嵌入式处理器ZU9EG 作为协处理器来实现通讯和管理功能。 该平台的主处理器 XCKU115 外挂两组 72

Zynq UltraScale+ MPSoC 多媒体应用

消费者渴望更高的视频质量,推动了视频技术的发展。MPSoC 基于 Zynq-7000SoC ,包括一个可编程逻辑 (PL) 的桥接处理系统 (PS),但它在 Zynq UltraScale+ MPSoC进行了额外的扩展,因而非常适合多媒体应用领域。主要的区别包括:针对 UHD-4K 集成了支持 H.264 / H.265 的视频编解码器单元,适用但不仅仅适用于监控、视频会议、嵌入式视觉和一些广

Linux下I2C调试工具--for--Zynq MPSOC/Jetson Xavier

Linux下I2C调试工具 1、简介 i2c-tools是一个专门调试i2c的工具,无需编写任何代码即可轻松调试I²C设备,可获取挂载的设备及设备地址,还可以在对应的设备指定寄存器设置值或者获取值等功能。i2c-tools有如下几个常用测试命令i2cdetect, i2cdump, i2cget, i2cset,i2ctransfer。 2、i2c-tools工具安装 2.1、Jetson

哈工大毕设记录-使用ZYNQ MPSoC开发板实现的Linux环境千兆以太网C语言UDP协议批量文件存取(上)

写在前面:本文仅为一位哈工大本科学生的毕设过程记录(吐槽),可参考性有限,供后来的广大学弟学妹们参考一下吧,我趟过的坑别再跳了。 字体区别:黑色加粗为文章结构脉络表述,红色为必须明确的重点,绿色为次重点,蓝色为吐槽。 主要描述内容包括以下六条,分上下篇,123上篇,456下篇(下篇:“咕咕咕”): 如何使用AD迅速开展能够应对本科毕设等级的PCB绘画工作(不涉及制板);如何利用Petalin

XILINX MPSOC通过VPSS实现输出缩放,像素格式转换

简介:赛灵思 mpsoc 7ev vpss输出缩放功能: 针对vdec 解码之后,不同分辨率的视频流,进行vpss缩放,然后过mixer统一成一种分辨率和像素格式输出显示。即:工程实现分辨率的上下变换和像素格式统一的功能。工程通过vpss之后,会统一成NV16 NV12 XV20 XV15中的一种像素格式,进行输出,也就是说不管vdec解码完成的流是什么格式 什么分辨率的流都可以通过

Xilinx UltraScale+ MPSOC(ZU9EG/ZU15EG)高性能 PCIe 数据预处理板

PCIE707 是一款基于 PCIE 总线架构的高性能数据预处理 FMC 载板,板卡具有 1 个 FMC+(HPC)接口,1 路 PCIe x4 主机接口、1 个 RJ45 千兆以太网口、2 个 QSFP+ 40G 光纤接口。板卡采用 Xilinx的高性能 UltraScale+ MPSOC 系列 FPGA 作为实时处理器,实现FMC 接口数据的采集、处理、以及设备间互联传输。PS 端外挂 1 组

赛灵思-Zynq UltraScale+ MPSoC学习笔记汇总

Zynq UltraScale+ MPSoC学习目录: 1、 赛灵思-Zynq UltraScale+ MPSoCs:产品简介 2、赛灵思-Zynq UltraScale+ MPSoC学习笔记:Petalinux 2021.2工具安装 3、赛灵思-Zynq UltraScale+ MPSoC学习笔记:Petalinux 的设计流程及定制Linux系统 4、Zynq UltraScale

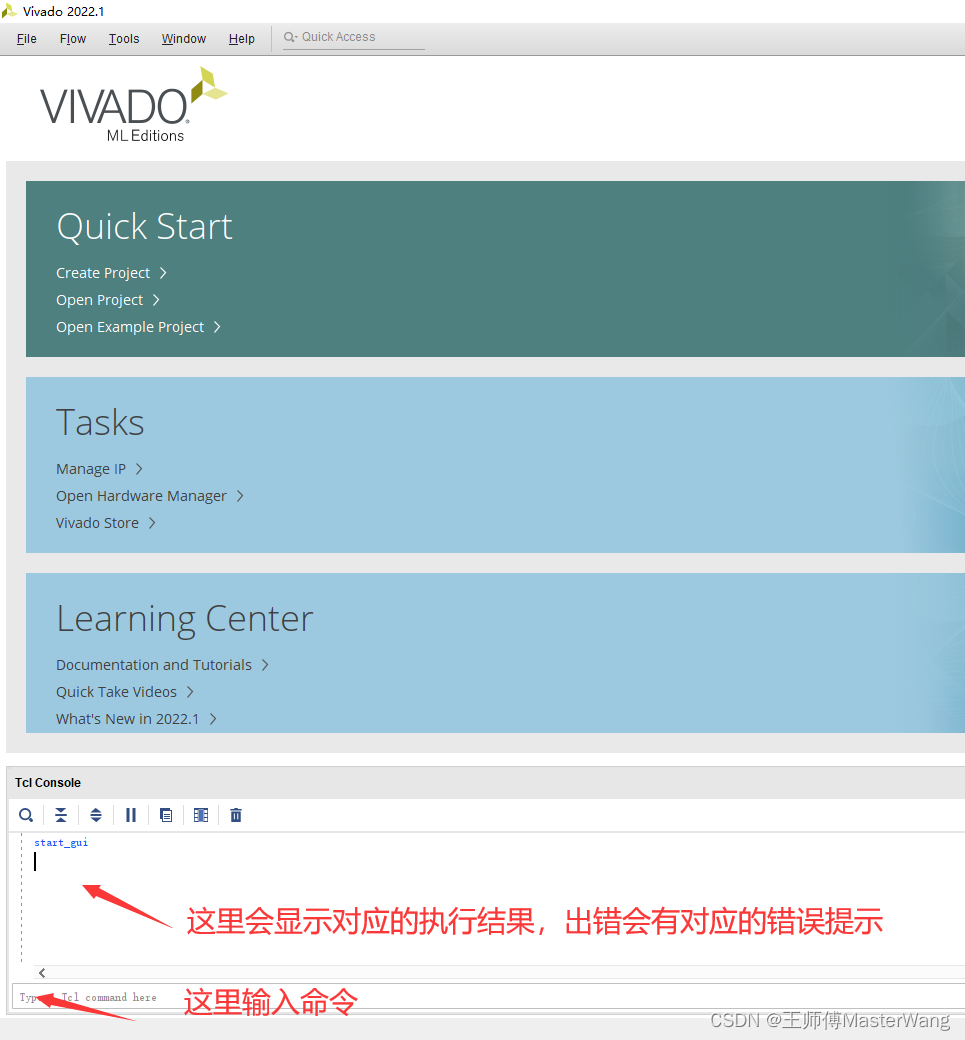

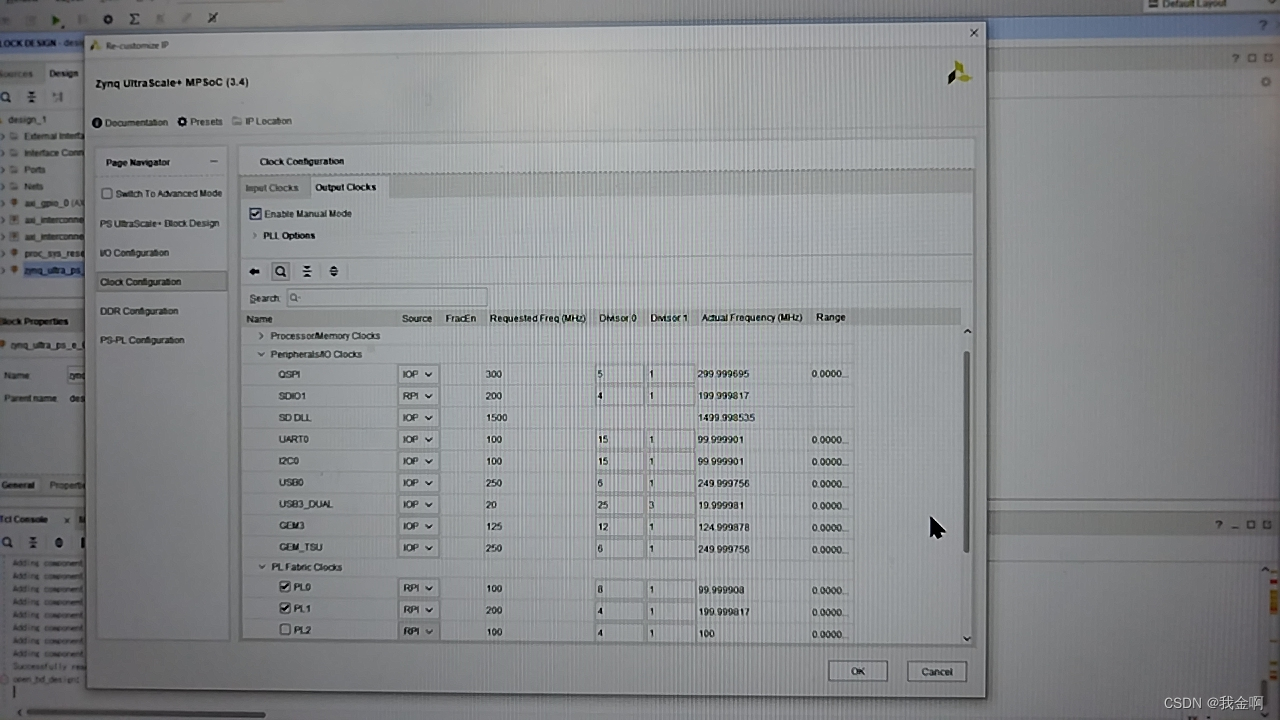

Zynq UltraScale+ MPSoC QSPI时钟修改

Xilinx社区提供方法 分频参数只支持如下几种(可参照Zynq UltraScale+ MPSoC芯片手册的寄存器说明) FPGA输出时钟在以下位置可见