modelsim专题

modelsim仿真流程

modelsim仿真流程 1、建立工程 project new "../prj" test.mpf 2、添加rtl文件 project addfile "../test.v" verilog 3、建立仿真库 vlib work 4、编译rtl到仿真库中 vlog -sv -sv09compat +define+T133 +incdir+"../rtl" test.v -wo

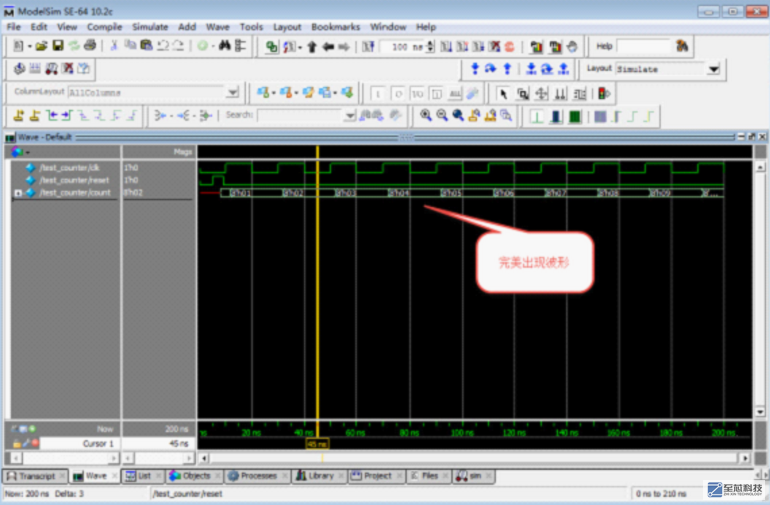

【乌拉喵.教程】编写TestBench,quartus与modelsim时序仿真

最近将多年来收集到的教学视频、国内外图书、源码等整理整合拿出来,涉及arm、Linux、python、信号完整性、FPGA、DSP、算法、stm32、单片机、制图、电子模块、kali、出版社图书等。资料目前约1.5TB+。详情请见: https://www.bilibili.com/read/cv20701606 昨天搜了一圈,也没整会这个仿真,今天在武梦梦的指导下修改了testbench,

关于在Quartus II和ModelSim中进行FPGA仿真报错的问题

今天晚上在用Quartus II设计好FPGA代码后,尝试在ModelSim中进行前仿真以验证设计功能的时候,总是报错。错误状态如下: Can’t launch the ModelSim-Altera software – the path to the location of the executables for the ModelSim-Altera software were not s

使用Modelsim独立仿真Altera及Xilinx IP核

使用Modelsim进行仿真非常方便,可以通过.do文件完成一些重复性的界面操作,但是使用Modelsim仿真IP核的时候经常会因为没有库文件的问题而纠结,网上不乏一些相关教程,但是在使用过程中总会遇到这样那样的问题,于是我痛定思痛,决定彻底解决这个问题,为了帮助大家解决相同的烦恼,决定写这篇文档,帮助大家避免走我曾走过的弯路,这也是我的第一篇教程,希望能帮到大家! 1 软件环境

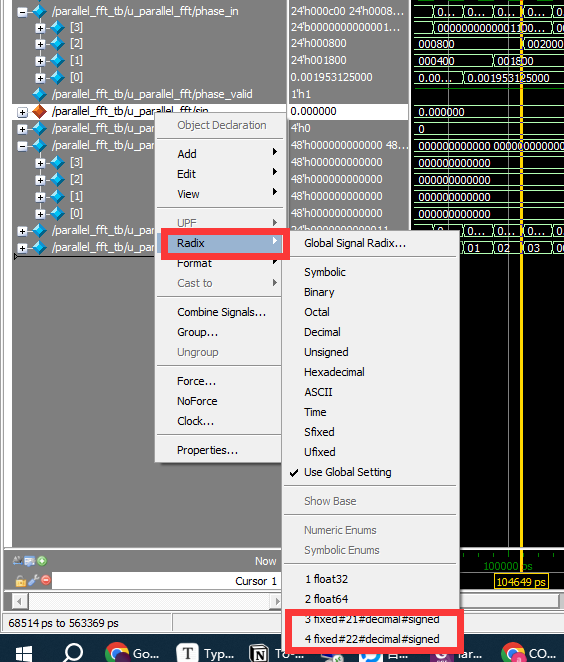

modelsim的使用技巧

因为一开始是写在个人博客上的,后续的更新在fpgaghost.com个人博客上,有需要请自行查看。 更舒服正确的查看波形 Zoom Full 展现所有波形,看到全局波形的动态 analog 可以查看信号的波形 如果波形覆盖到了别的地方,参考文章:Modelsim设置数据以模拟波形显示,只需要先选择合理的信号进制(radix),如下图选择浮点 修改进制为32为单精度浮点

modelsim仿真环境的搭建

相对gui图形界面的操作,脚本执行更方便。 注意: 如果有include语句。那么就增加+incdir+路径。如果想用电路视图。那么就加入参数:vsim -debugDB vlog -work work -vopt +incdir+D:/tools/perl/perl-study/verilog/embedded_risc/trunk/Verilog \D:/tools/perl/perl-

用ModelSim查看ChipScope所抓取的波形

在线查看ChipScope所抓取的信号比较方便,但有时在调试过后又想看之前的数据,那么这时我们就应该将其保存下来。 步骤1.选择ChipScope里的File-Export,输出Format选择VCD,Signals to Export 选择“Waveform Signals/Buses",a.vcd 步骤2.打开ModelSim,File-Change Directory,选择VCD文件所在

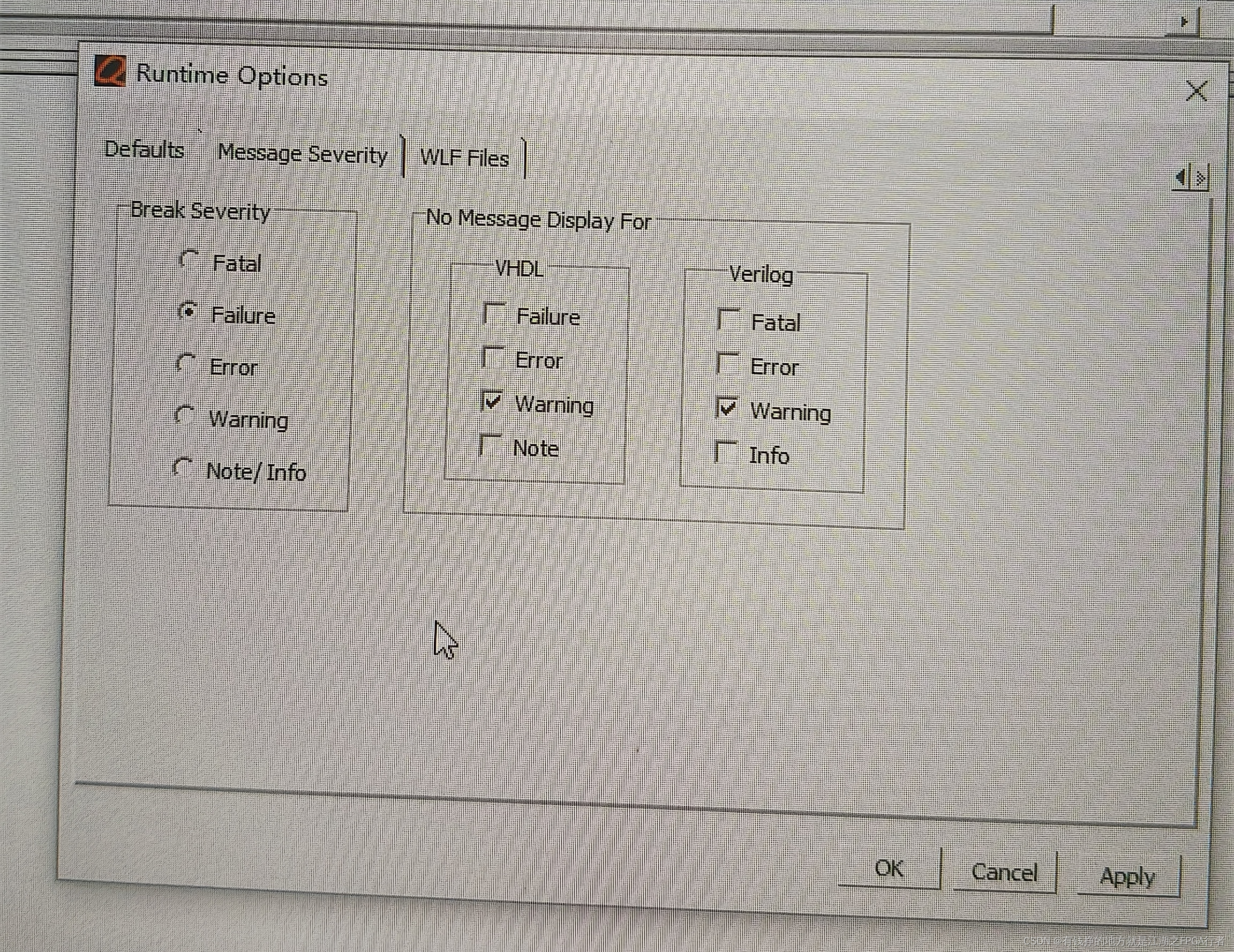

ModelSim - INTEL FPGA STARTER EDITION

ModelSim - INTEL FPGA STARTER EDITION 使用modelsim starter版本进行仿真,提示有错误信息,但无法定位,双击也不弹出错误提示:这时需要确定可能是lisence问题,代码超过了10000行,虽然本身设置并不大,但是加上altera的库之后就有可能出现这个问题。此时我尽量减少例化模块尝试,发现可以仿真成功。具体限制对比如下: https://ww

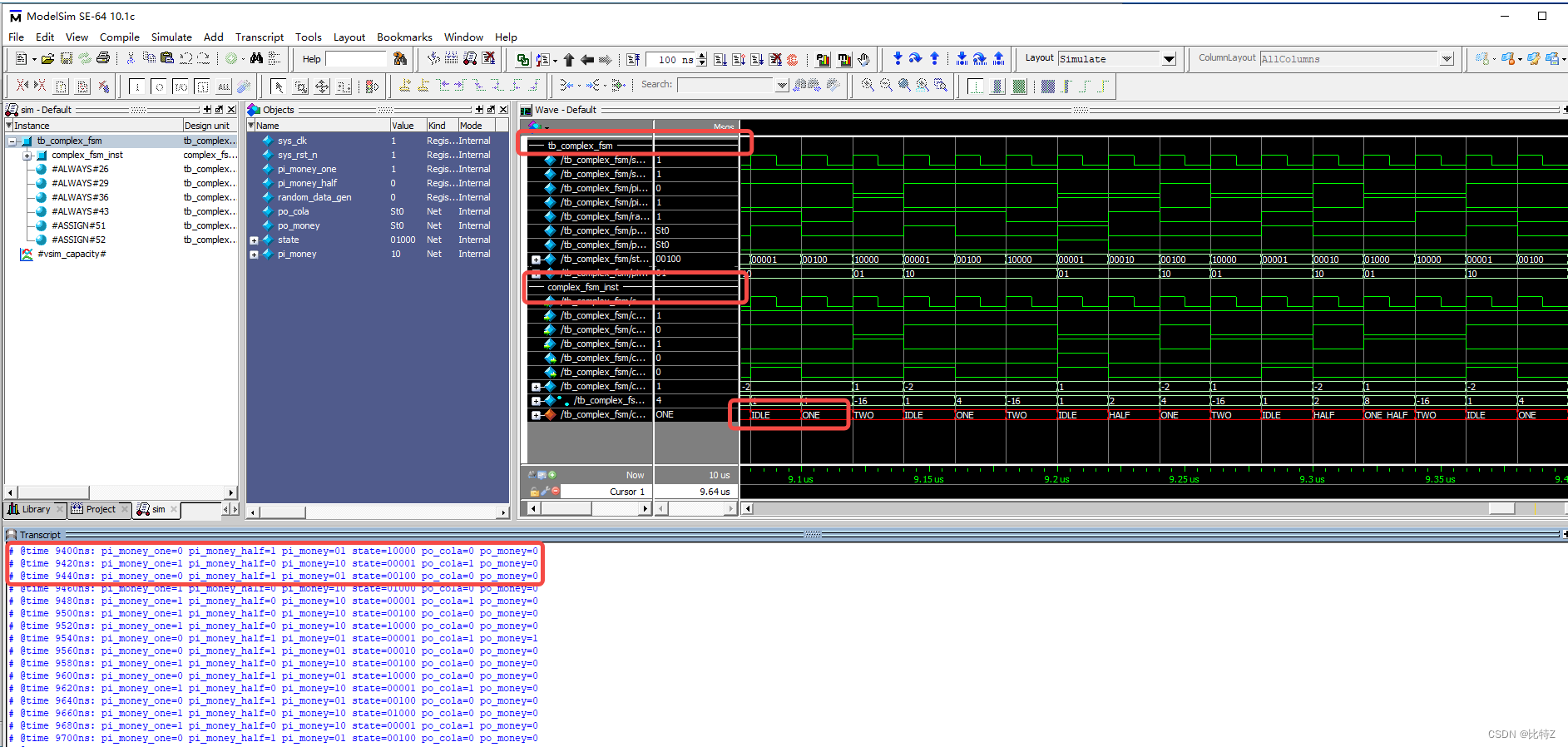

FPGA学习笔记(2)——Verilog语法及ModelSim使用

1.1 语法 1、赋值语句 = 和 <= = 为阻塞赋值,当该语句结束时,下一个语句才开始执行,串行执行 <= 为非阻塞幅值,该语句和整个语句块同时执行,并行执行 1.2 ModelSim使用 1、修改源文件路径:File -> Source Directory/Change Directory 2、查看窗口:View -> Transcript/Project/Library 3、新建

Modelsim与Verilog入门

0.什么是Modelsim? Modelsim是一个支持多语言的仿真环境,比如我知道的Verilog和VHDL语言都可以在里边使用,这俩都是硬件描述语言; 即就是个软件,你可以用Verilog语言来写代码,然后编译,仿真出波形..... 软件图标长这样: 1.什么专业学习它,以及它可以干什么? 我知道的:计算机科学与技术本科阶段是要学的,然后体系结构的硕士也可以学习,IC设计类专业那

Modelsim自动化仿真脚本(TCL)——简单实例

目录 1. Modelsim与TCL脚本的关系 2.实验文件 2.1设计文件 2.2仿真测试文件 2.3. 脚本文件 3. 实验步骤 3.1. 创建文件夹 3.2. 指定路径 3.3. 创建工程 3.4. 运行命令 3.4. 实验效果 1. Modelsim与TCL脚本的关系 TCL(Tool Command Language)是一种脚本编程语言,由

【Modelsim】保持波形格式重编译and波形的保存与查看

文章目录 保持原波形格式重编译波形的保持与查看保存波形打开工程查看波形 保持原波形格式重编译 Modelsim 仿真设置好波形格式后,若需要修改代码并保持原波形格式重新查看波形,只需将文件重新编译后仿真即可。 1.修改代码后Project页面的代码状态变成❓ 2.在Transcript页面点击右上角的Compile Out of Date图标(只编译❓的代码)、或点击Co

UVM系统验证基础知识0(modelsim搭建第一个UVM环境及源码下载 )

需求说明:UVM系统验证 内容 :IC设计验证 来自 :时间的诗 原文:http://www.ibowen.net/a/toutiao/252197.html 1 创建代码 在modelsim中建立UVM环境,使用的UVM是UVM1.1b。

从ISE 无法启动modelsim

在ISE14.7 中双击启动modelsim仿真后,出现如下报错: ERROR: Platform mismatch! ERROR: Error(s) encountered while extracting pre-compiled simulation library information. 原因 :当前工程是用32bit ISE14.7版本打开,而modelsim是6

基于脚本的modelsim自动化仿真笔记

一、基本介绍 这里介绍一下如何利用脚本调用modelsim进行自动化仿真,随笔前面先介绍一下前仿真,随笔结尾处介绍后仿真。前仿真的基本介绍如下所示,由于我的笔记是写在.do文件中,因此我这里也给代码的格式,如下所示: # #表示注释,modelsim不支持中文,因此可能不能识别注释#①退出当前仿真功能,退出当前的工程,跟在modelsim界面的命令行敲入命令的效果一样,之后就可以

FPGA ModelSim 仿真

FPGA ModelSim 仿真 1、编写文件编写工程文件编写测试文件 2、ModelSim 仿真仿真 1、编写文件 编写工程文件 选择FPGA 型号: 选择仿真工具,及语言: 新建文件: 编写文件并保存 编写测试文件 2、ModelSim 仿真 新建工程 设置工程路径: 添加文件和测试文件: 编译,如有错误可以进行修改,如图: 仿真 设置仿

ModelSim DE-64 10.6c的安装和vivado的联调--更新中

软件下载:Vivado:【1】Vivado 2018.3 配置ModelSim仿真_vivoda2018与modelsim-CSDN博客 软件安装:Modelsim 破解 注册 | 霹雳大乌龙的学习笔记 因为2018.3的vivado只能用ModelSim 10.6C

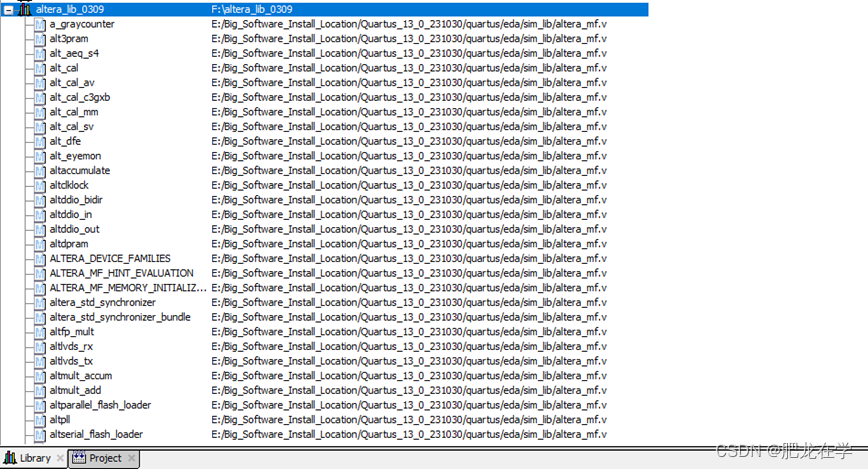

Modelsim 如何创建Altera库

以 (altera_mf)为例进行介绍 1、点击File,创建新的Libiary,弹出新建库的窗口,我们选择第三项“a new library and a logical mapping to it”。Library Name输入库名称,Library Physival Name输入库的地址,然后点击OK。 2、然后点击Project栏, 右键空白处,会弹出 3、点击Existing Fil

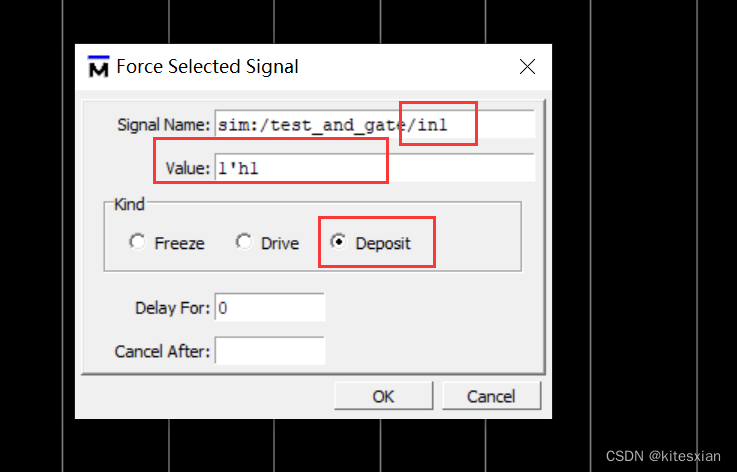

modelsim输入信号

modelsim输入信号 2012-06-02 22:18:09 分类: 嵌入式 一,DO文件的应用和工作方式 执行File/New/Souce/Do命令,进入Do文件编辑方式,在编辑窗口输入仿真批处理文件的代码,以.do为扩展名保存文件,调用方式:do filename parameters,完成对设计的仿真 用do文件进行仿真真得很方便,比写testbenc

modelsim独立仿真教程

一.GUI界面的仿真步骤 1.首先把你需要仿真的设计文本和仿真文本全部放在同一个文件夹下面,注意,文件夹路径不能包含中文。我的设计文件:counter.v`timescale 1ns / 1nsmodule counter (count, clk, reset);output [7:0] count;input clk, reset;reg [7:0] count;parameter t

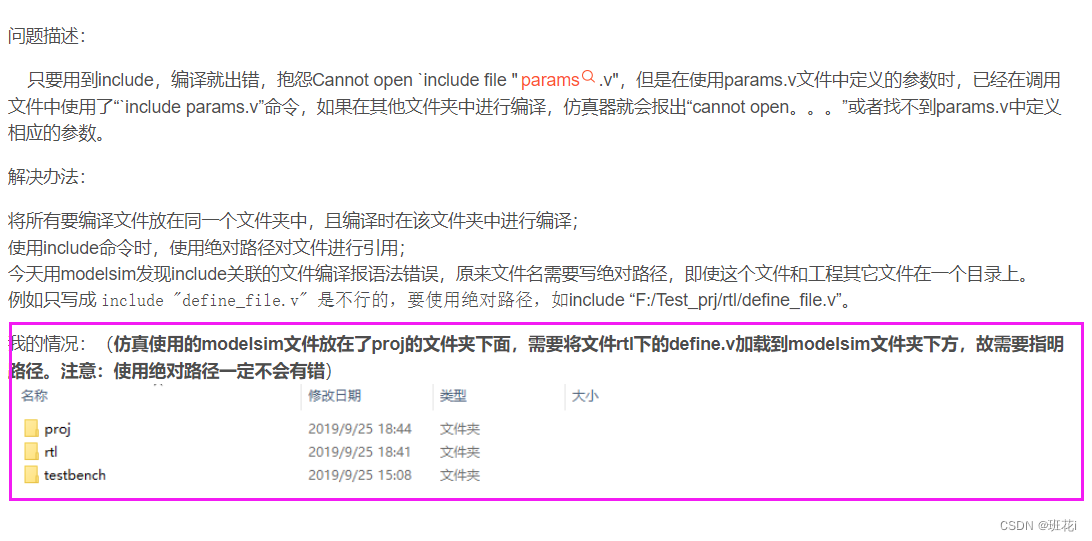

Modelsim报错:Cannot open `include file / (vlog-2163) Macro `INST_ADD_SUB is undefined.

目录 问题描述网上找到的原因:解决方案: 问题描述 我的verilog文件里包含了define,其中容易忘记加的 **`**符号我也加上了 报错为: Cannot open `include file “defines.v”. (vlog-2163) Macro `INST_ADDI is undefined. 网上找到的原因: **最先去检查define和引用相关

Modelsim 第一个仿真程序 四位加法器

4位全加器 //4位全加器module a4(sum,cout,a,b,cin);input [3:0] a,b;input cin;output cout;output [3:0] sum;assign {count,sum} = a+b+cin;endmodule 4位全加器的仿真程序 //4位全加器的仿真程序`timescale 1ns/1ns `include "M

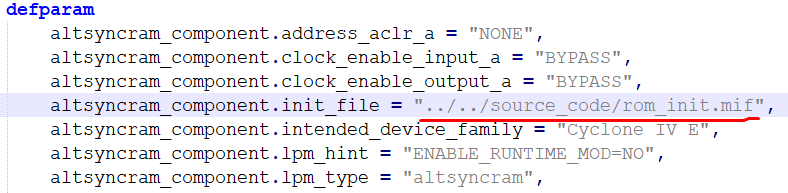

**modelsim仿真ROM IP核遇到无法读取mif文件的解决方法**

在用modelsim进行读取ROM内部数据仿真时遇到数据全为0,如图1,查看modelsim的提示说找不到mif文件,如图2。我的mif文件是放在source_code文件夹下的,参照网上说将mif文件放到modelsim根目录也无济于事,最后查看IP核产生的rom.v文件,把mif文件的路径位置进行更改,最后大功告成!其实就是相对路径的问题。 相对路径的补充:“./”表示当前目录,"

modelsim se使用.tcl脚本仿真rom读数据

最近安装了quartus19.2 pro版本,使用modelsim se进行单端rom仿真时读取的数据一直处于高阻态;怀疑是quartus版本导致,使用原先的quartus16.1 prime生成的单端rom仿真却正常。 (1)怀疑是19.2的仿真库没安装好 在19.2中使用Tools —> Lauch Simulation Library