本文主要是介绍modelsim se使用.tcl脚本仿真rom读数据,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

最近安装了quartus19.2 pro版本,使用modelsim se进行单端rom仿真时读取的数据一直处于高阻态;怀疑是quartus版本导致,使用原先的quartus16.1 prime生成的单端rom仿真却正常。

![]()

(1)怀疑是19.2的仿真库没安装好

在19.2中使用Tools —> Lauch Simulation Library Compiler,Tool name : 选中Modelsim;Executable location :选中modelsim.exe所在文件夹;选中芯片型号到Selected families;勾选Verilog和VHDL;Output directory新建非中文目录,用于生成对应的库文件。

库文件生成成功后,在modelsim的安装目录下的modelsim.ini中可以看到相关库文件的路径载入代码。

(2)怀疑是tcl脚本有问题

vlib work

vlog ../../pulser_init/sim/*.v

vlog ../../pulser_init/src/*.v

vlog ../../pulser_init/ip/mem_rom/*.v

vlog ./*.v

vsim -t ps -novopt +notimingchecks -L altera_mf_ver -L altera_mf\

work.pulser_init_tb

add wave -position insertpoint sim:/pulser_init_tb/pulser_init_inst/*

run -all

使用tcl脚本仿真时发现rom出来的数据还是高阻态,检查tcl脚本

首先检查19.2生成的rom ip核相关文件,用户程序例化的mem_rom模块中,例化了mem_rom_rom_1port_191_jm2g5pa模块,mem_rom_rom_1port_191_jm2g5pa模块中又例化了altera_syncram。那么上述tcl脚本vlog的.v文件是不完全的,添加两条

vlog E:/project/pulser_init/ip/mem_rom/sim/mem_rom.v

vlog E:/project/pulser_init/ip/mem_rom/rom_1port_191/sim/mem_rom_rom_1port_191_jm2g5pa.v

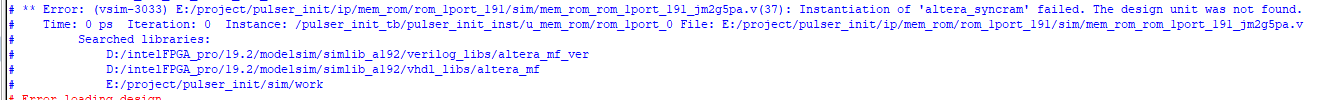

在modelsim中cd到sim文件夹(tcl脚本在sim文件夹中),do sim_pulser_init.tcl,报错

提示找不到 altera_syncram,查资料发现这个是库里面的原语,添加lpm_ver库

vsim -t ps -novopt +notimingchecks -L altera_mf_ver -L altera_mf -L lpm_ver\

work.pulser_init_tb

再do之后rom里面的数据可以正常读出

![]()

关于库文件和tcl脚本的相关文档后续再做记录

这篇关于modelsim se使用.tcl脚本仿真rom读数据的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!