mmu专题

ARM架构(五)——MMU①

1.MMU基础 1.1 为什么要用MMU,为什么要用虚拟地址? MMU的作用,主要是完成地址的翻译,即虚拟地址到物理地址的转换,无论是main-memory地址(DDR地址),还是IO地址(设备device地址),在开启了MMU的系统中,CPU发起的指令读取、数据读写都是虚拟地址,在ARM Core内部,会先经过MMU将该虚拟地址自动转换成物理地址,然后在将物理地址发送到AXI总线上,完成真正

ARM学习之协处理(disable cache,mmu)

ARM 微处理器可支持多达 16 个协处理器,用于各种协处理操作,在程序执行的过程中,每个协处理器只执行针对自身的协处理指令,忽略 ARM 处理器和其他协处理器的指令。ARM 的协处理器指令主要用于 ARM 处理器初始化 ARM 协处理器的数据处理操作,以及在ARM 处理器的寄存器和协处理器的寄存器之间传送数据,和在 ARM 协处理器的寄存器和存储器之间传送数据。 ARM 协处理器指令包括以下 5

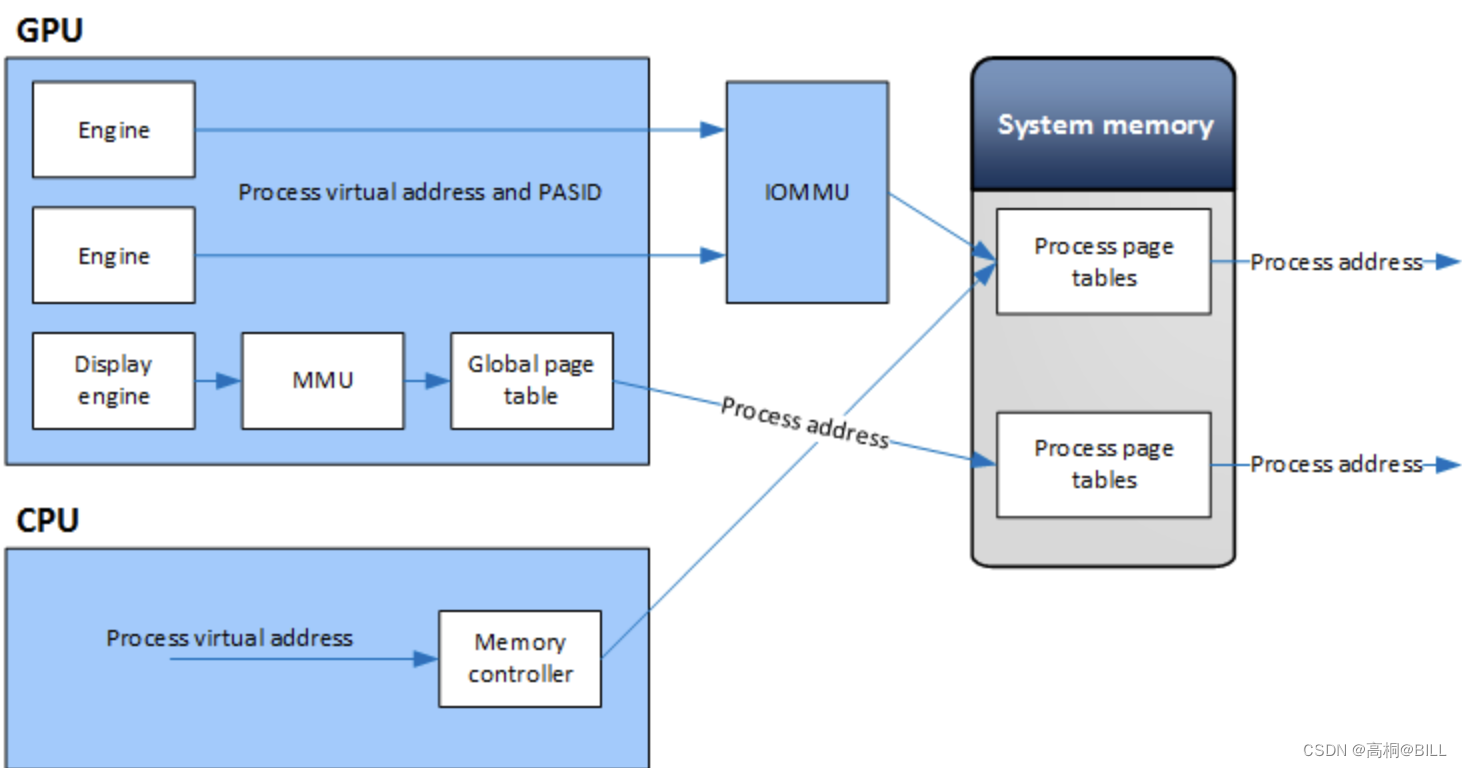

Linux内存从0到1学习笔记(8.15 MMU/IOMMU/SMMU概览)

一, 什么是MMU? MMU(Memory Management Unit 内存管理单元),即内存管理单元,是计算机硬件中的一个重要组件,主要负责处理中央处理器(CPU)的内存访问请求。 其工作原理如下: 当程序发出内存访问请求,包括读取或写入操作以及逻辑地址(虚拟地址)。然后,MMU根据页表等数据结构将逻辑地址转换为物理地址。接着,MMU将物理地址发送给内存控制器进行实际的内存读写操作

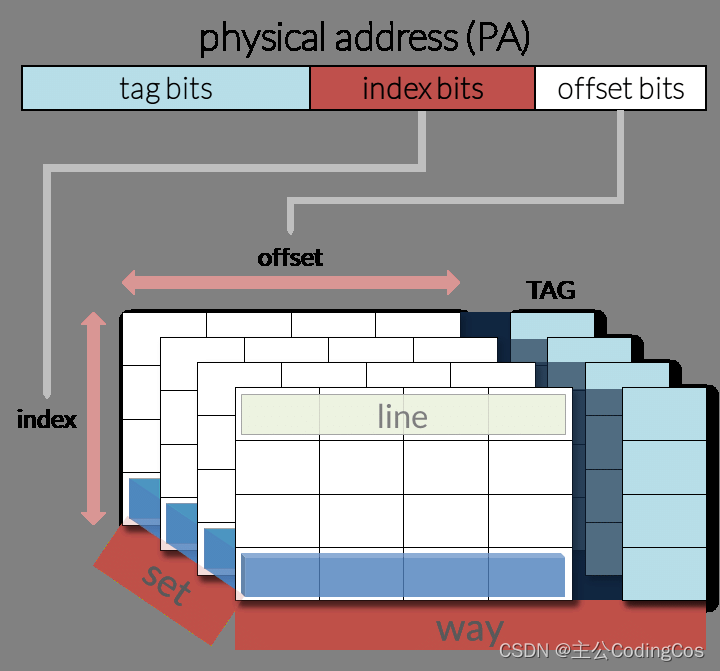

【ARM Cache 及 MMU 系列文章 6.4 -- ARMv8/v9 如何读取 Cache Tag 及分析其数据?】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 Cache Tag 数据读取测试代码 Cache Tag 数据读取 在处理器中,缓存是一种快速存储资源,用于减少访问主内存时的延迟。缓存通过存储主内存中经常访问的数据来实现这一点。为了有效地管理这些数据,缓存被组织成行(lines)或块(blocks),每个行或块包

【ARM Cache 及 MMU 系列文章 6.3 -- ARMv8/v9 Cache Tag数据读取及分析】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 Cache Tag 数据读取测试代码 Cache Tag 数据读取 在处理器中,缓存是一种快速存储资源,用于减少访问主内存时的延迟。缓存通过存储主内存中经常访问的数据来实现这一点。为了有效地管理这些数据,缓存被组织成行(lines)或块(blocks),每个行或块包

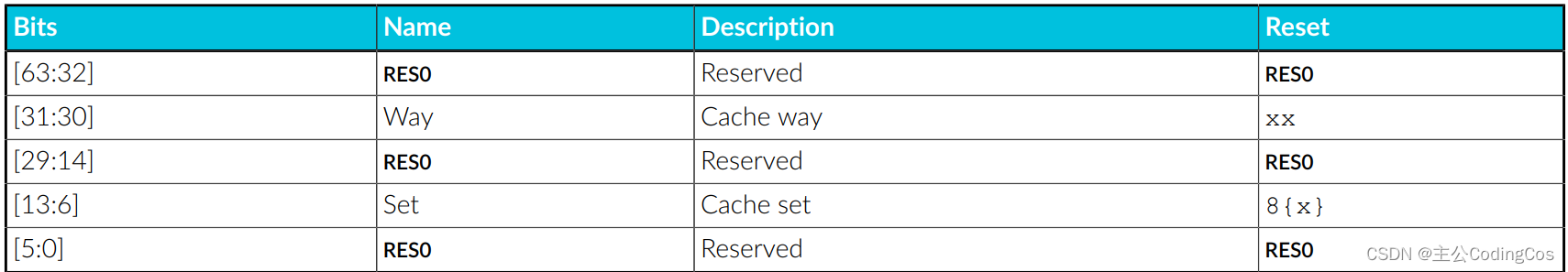

【ARM Cache 及 MMU 系列文章 6.2 -- ARMv8/v9 Cache 内部数据读取方法详细介绍】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 Direct access to internal memoryL1 cache encodingsL1 Cache Data 寄存器 Cache 数据读取代码实现 Direct access to internal memory 在ARMv8架构中,缓存(Cach

【ARM Cache 系列文章 7.2 – ARMv8/v9 MMU 页表配置详细介绍 03 】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 表描述符 Table descriptor52-bit OA 颗粒为4KB 和16KB52-bit OA 颗粒为64KB48-bit OA 颗粒为4KB 和16KB Stage 1 和 Stage 2 介绍第一阶段(Stage 1)转换的表描述符属性字段第二阶段(Stage 2)

【ARM Cache 及 MMU 系列文章 6.1 -- Cache maintenance 相关寄存器及指令详细介绍】

请阅读【ARM Cache 及 MMU/MPU 系列文章专栏导读】 及【嵌入式开发学习必备专栏】 文章目录 Cache Maintenance registers and instructionsDCZID_EL0DCZID_EL0寄存器字段解释 DCZ 使用场景Cache maintenance 范围选择 Cache maintenance 指令集 Cache Maint

[mmu/cache]-ARM cache的学习笔记-一篇就够了

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 应用场景——什么时候需要刷cache 1、在不同硬件之间共享数据时 场景:CPU往src地址处写入了一串数据,然后交给Crypto硬件进行加解密处理,加解密后的数据放在了dst地址处,然后cpu读取dst地址处的数据获取结果。 (1)、cpu在往内存(src地址)写数据时,cache中会缓存这些数

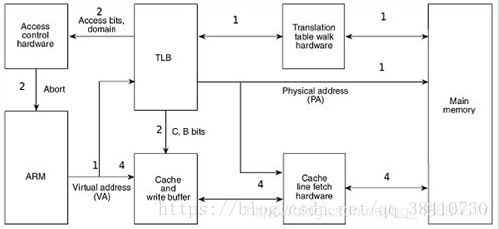

[mmu/cache]-ARM MMU的学习笔记-一篇就够了

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 ARMV8-aarch64的MMU 1、MMU概念介绍 MMU分为两个部分: TLB maintenance 和 address translation MMU的作用,主要是完成地址的翻译,无论是main-memory地址(DDR地址),还是IO地址(设备device地址),在开启了MMU的系统中,

思考:开启MMU瞬间可能出现的多种问题以及多种解决方案

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 (说明本文的介绍都是基于armv8-aarch64或armv9硬件架构) 在mmu未开启阶段,PC操作的都是物理地址执行程序,这样看起来一切正常,没啥问题。 例如: 取指(到物理地址0x4000处取指)、译码、执行 取指(物理地址0x4004处取指)、译码、执行 取指(物理地址0x4008处取指)、译

MMU关闭时Cache的缓存策略是怎样的

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 在学习MMU章节时,我们发现在页表的entry中,BIT[4:2]指向了MAIR寄存器,该寄存器描述了内存属性,其实就是cache的缓存策略属性(inner\outer\shareable\cacheable)。 也就是页表中的每一个entry都指向了一个这样的Attr。 那么我如果把MMU disable

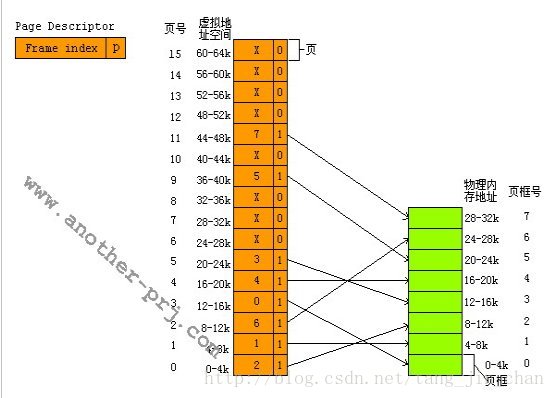

[架构之路-123]-《软考-系统架构设计师》-操作系统-2-操作系统原理 - 存储层次结构与存储管理(寄存器、Cache、MMU、内存、外存、页表)

目录 前言: 第11章 操作系统 第4节 存储管理:寄存器+cache+内存+外存 4.1计算机存储层次模型 4.1.1 层次模型的内容 4.1.2 通用的思想和思路 4.1.3 内存抽象 4.1.3 多核并行架构 4.2 位于CPU内部的寄存器 4.3 位于SOC芯片内部的Cache (纯硬件、解决速率不匹配问题) 4.3.1 概述 4.3.2 为什么需要cache 4

内核中与驱动相关的内存操作之一(MMU)

1.MMU的存在意义: MMU(Memory Manage Unit)的出现是为了解决以下这类问题的一种"硬件算法"或者说策略:16MB的程序运行于4MB内存空间的问题,实现内存的更高效地利用.类比于现实生活中的银行.银行无须要保障每时每刻都准备充足以备所有用户同时取钱--这种情况基本上不会发生.通过挖东墙补西墙,实现资金的更高效利用.从而达到一种"动态平衡",而使人表面上看到的是"静止

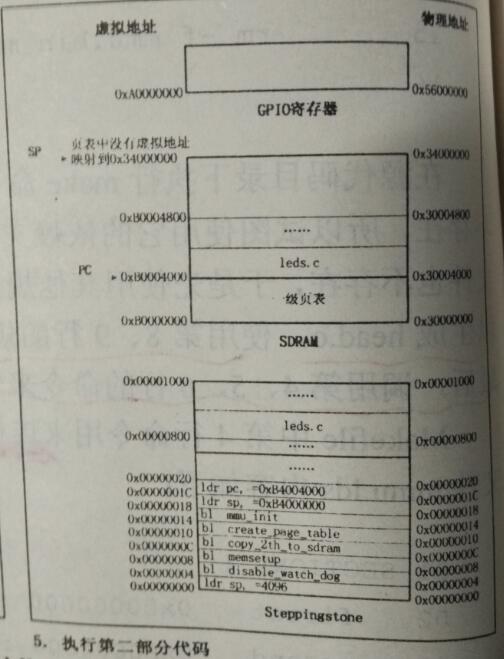

JZ2440 第7章 内存管理单元 MMU

本章目标: 了解虚拟地址和物理地址的关系; 掌握如何通过设置MMU来控制虚拟地址到物理地址的转化; 了解MMU的内存访问权限机制; 了解TLB、Cache、Write buffer的原理,使用时的注意事项; 通过实例深刻掌握上述要点; 7.1 内存管理单元MMU介绍 7.1.1 S3C2410/S3C2440 MMU特性 内存管理单元(Memory Managemen

【补充】 关于*(mmu_tlb_base + (virtuladdr 20))的理解

转载地址 http://blog.csdn.net/czg13548930186 对于MVA到PA转换过程,以及描述符所扮演的角色,请看下图: 来看代码: unsigned long virtuladdr, physicaladdr;unsigned long *mmu_tlb_base = (unsigned long *)0x30000000;//对应上图TTB

MMU工作原理以及S3C2440的MMU

zz : http://blog.csdn.net/xie376450483/article/details/5728772 MMU,全称Memory Manage Unit, 中文名——存储器管理单元。 许多年以前,当人们还在使用DOS或是更古老的操作系统的时候,计算机的内存还非常小,一般都是以K为单位进行计算,相应的,当时的程序规模也不大,所以 内存容量虽然小,但还是可以容纳当时的程序。

嵌入式100题(86):简述处理器在读内存的过程中,CPU核、cache、MMU如何协同工作?画出CPU核、cache、MMU、内存之间的关系示意图加以说明...

简述处理器在读内存的过程中,CPU核、cache、MMU如何协同工作?画出CPU核、cache、MMU、内存之间的关系示意图加以说明 现代操作系统普遍采用虚拟内存管理机制,这需要MMU(Memory Management Unit,内存管理单元)的支持。有些嵌入式处理器没有MMU,则不能运行依赖于虚拟内存管理的操作系统。 操作系统可以分成两类,用MMU的、不用MMU的。用MMU的是:Wi

arm-linux内核start_kernel之前启动分析(3)-开启MMU,走进新时代

最近在忙一款PPC处理器的芯片验证和内核移植工作,导致arm-linux启动分析最后一部一直没有写,今天将arm-linux start_kernel之前的最后一部分分析记录下。之前2篇文章链接如下: http://blog.csdn.net/skyflying2012/article/details/41344377 http://blog.csdn.net/skyflying2012/ar

嵌入式linux学习-ARM MMU工作原理分析

一 MMU的产生 许多年以前,当人们还在使用DOS或是更古老的操作系统的时候,计算机的内存还非常小,一般都是以K为单位进行计算,相应的,当时的程序规模也不大,所以内存容量虽然小,但还是可以容纳当时的程序。但随着图形界面的兴起还用用户需求的不断增大,应用程序的规模也随之膨胀起来,终于一个难题出现在程序员的面前,那就是应用程序太大以至于内存容纳不下该程序,通常解决的办法是把程序分割成许多称为覆盖块(

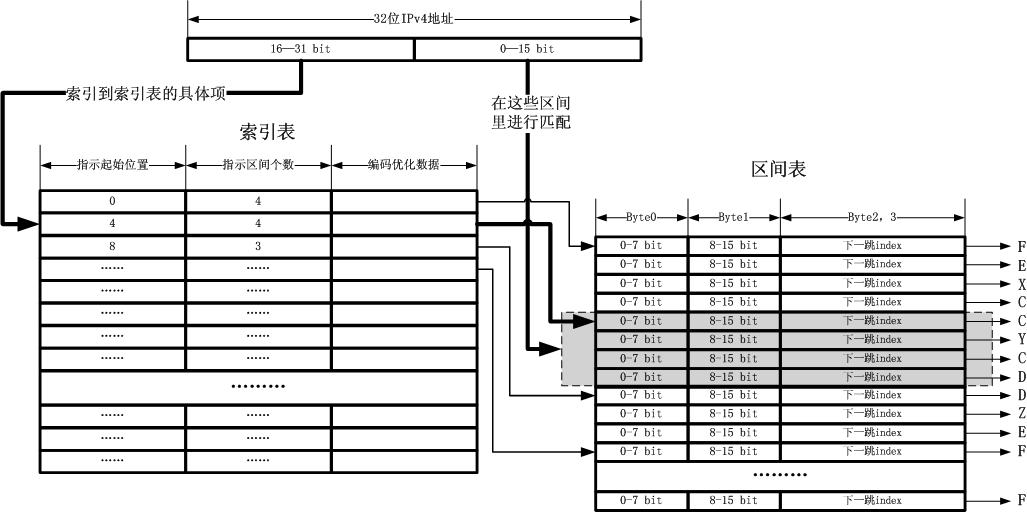

从模拟MMU设计一个路由表的失败到DxR的回归

在前几天写的一篇文字中,我描述了一次失败的经历,对于很在乎过程的我,描述下来就是成功。然而,我不得不回退到DxR,研究一下它的本质而不是其算法思 想。之所以失败,是因为我的逆反心理在作怪,我真的没有研究DxR的本质就开始动手,无疑于打一场毫无准备且对对手完全不了解的恶仗,如果不适可而止,其 结果必然和当初死磕Bloom一样悲惨! DxR的本质 DxR并没有发明什么新的算法,它之所以高效是因为它分

基于ARM板s3c2440---MMU和Cache

Cache—高速缓存存储器 高速缓冲存储器(Cache)其原始意义是指存取速度比一般随机存取记忆体(RAM)来得快的一种RAM,一般而言它不像系统主记忆体那样使用DRAM技术,而使用昂贵但较快速的SRAM技术,也有快取记忆体的名称。 高速缓冲存储器是存在于主存与CPU之间的一级存储器, 由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多, 接近于CPU的速度。在计算机存储系统的层次结

Armv8/Armv9 MMU学习的28问,你能回答上来几个

01、一个大系统中有多少个MMU ? 一般情况下:一个core里面有一个MMU,8个core就是8个MMU; 除了Arm core里有MMU之外,在SOC中,还会诸多个SMMU,具体看SOC的架构设计。 02、一个ARM Core中有多少个Translation regime? 在Armv8/Armv9架构中(不考虑CCA/RME安全扩展),至少有9类Translation regime,注

MMU如何通过虚拟地址找到物理地址-下

接着上文:MMU如何通过虚拟地址找到物理地址? 5,虚拟内存到物理内存的推导 本文只介绍最普遍的64位地址,四级页表,每个页表4k的这种情况。 linux内核将一个进程的内存映射表建立好之后,在该进程被调度运行的时候,会将PGD的物理地址放置到MMU的页表基地址寄存器中,在X86_64架构下,该寄存器为CR3,ARM64架构下,该寄存器为ttbr0_el1和ttbr

![[mmu/cache]-ARM cache的学习笔记-一篇就够了](https://img-blog.csdnimg.cn/img_convert/0ea6ba23c2af7a42131aa1ca0cd44de6.png)

![[mmu/cache]-ARM MMU的学习笔记-一篇就够了](https://img-blog.csdnimg.cn/img_convert/ec5086d339e91a2745d65088c6a21b32.png)

![[架构之路-123]-《软考-系统架构设计师》-操作系统-2-操作系统原理 - 存储层次结构与存储管理(寄存器、Cache、MMU、内存、外存、页表)](https://img-blog.csdnimg.cn/img_convert/a8e24d9bdaaa34796153ad055953d35e.png)