microblaze专题

Xilinx FPGA Microblaze AXI_IIC使用方法及心得

Xilinx FPGA Microblaze AXI_IIC使用方法及心得 前言 本着好好学习,认真负责的态度,我计划在空闲时间把自己用到的一些模块的使用方法与心得总结下与大家分享下,技术交流的同时共同进步,如有问题,欢迎批评指正! 本次先着重讲下AXI_IIC核的使用,后续还会包括以下模块 UART_AXI核使用及AXI总线详解QSPI_AXI核的使用AXI_DMA与AXI_FIFO使用,

MicroBlaze IP核中的外设接口和缓冲器接口介绍

MicroBlaze IP核是Xilinx公司提供的一个嵌入式软核处理器,广泛应用于FPGA设计中。在MicroBlaze IP核中,外设接口和缓冲器接口是处理器与外部设备和内存交互的关键部分。 1 外设接口 MicroBlaze处理器中的AXI4 内存映射外设接口AXI4是一种在Xilinx FPGA设计中常见的通信协议,用于在处理器和内存或其他外设之间传输数据。 指令外设接口(M_AXI_

MicroBlaze IP核的特性和暂停功能详述

MicroBlaze IP核的组织结构采用哈佛架构,为数据和指令访问提供了独立的总线接口单元。MicroBlaze支持的主要内存接口是本地存储器总线(Local Memory Bus, LMB)和AMBA AXI4接口(AXI4)和ACE接口(ACE)。 LMB提供对片上双端口块RAM的单周期访问。AXI4接口提供到片上和片外外围设备以及存储器的连接。ACE接口提供到存储器的高速缓存一致连接。

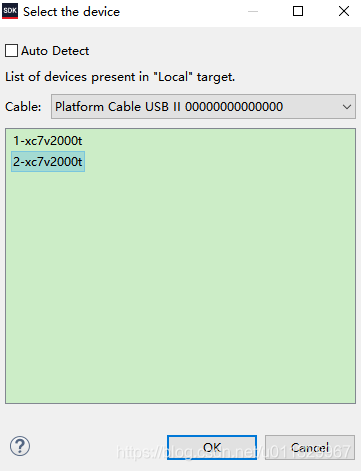

多个FPGA挂在同一个JTAG下去调试Microblaze时

当我们的系统存在多个FPGA挂在同一个JTAG下去调试Microblaze时,默认会出现: 此时需要先选定FPGA设备,才可以进行正常Debug操作:

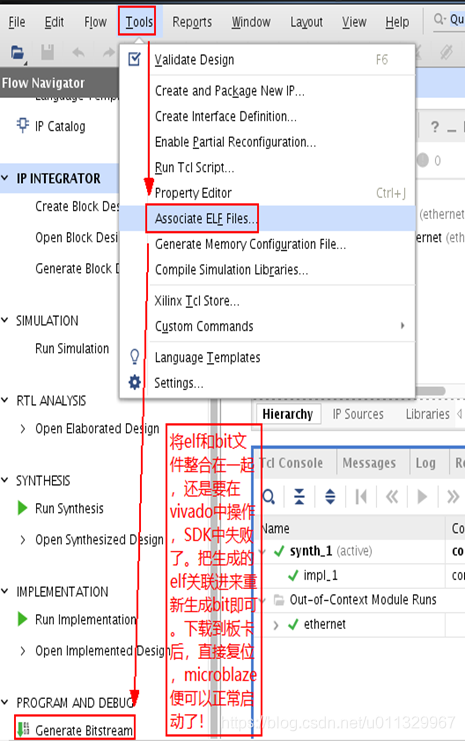

microblaze bit 和elf文件整合到一起

vivado一般使用microblaze时都需要先下载bit,再通过jtag挂入elf文件,程序才能跑起来;设计完成后我们需要把两个文件整合到一起,直接下载一个最终的bit即可,我们可以在vivado中添加elf,重新生成bit: 选择Tools->Associate ELF Files:(多个Microblaze可以对应添加多个elf文件) 然后点击Generate Bits

迁移基于MicroBlaze处理器的设计

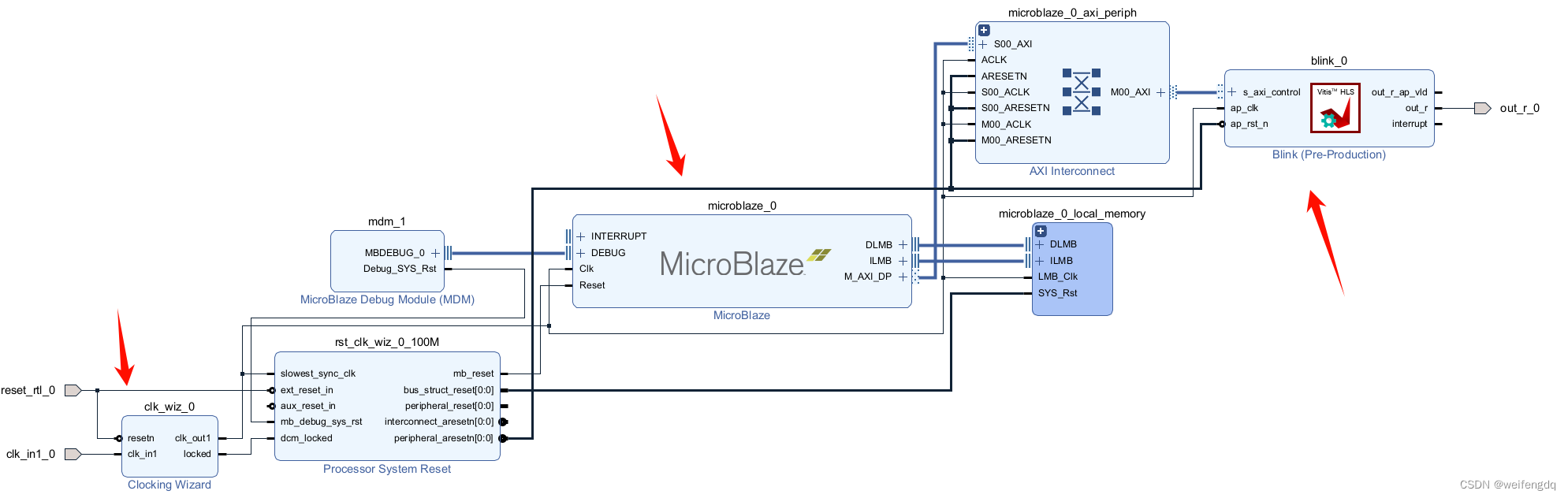

迁移基于MicroBlaze处理器的设计 生成系统基础设施(MicroBlaze、AXI_Interconnect, Clk_Wiz、Proc_Sys_Reset) 生成系统基础设施(MicroBlaze、AXI_Interconnect、Clk_Wiz和 Proc_Sys_Reset): 1.使用所需的板或可编程设备创建Vivado项目。 2.在“流导航器”中,单击“IP Integrator”

ZYNQ MicroBlaze AXI总线连接注意事项

目录 一、AMBA总线协议概述 1.ASB 2.AHB 3.APB 4.AXI (1)AXI4 (2)AXI4-Lite (3)AXI4-Stream 二、ZYNQ MicroBlaze连接AXI总线注意事项 三、解决方法 一、AMBA总线协议概述 AMBA是指先进的微控制器总线体系结构,主要由系统总线和外围总线两部分组成,它的演进如下: 根据 AMBA标准

Vivado Vitis 2023.2 环境配置 Git TCL工程管理 MicroBlaze和HLS点灯测试

文章目录 本篇概要Vivado Vitis 环境搭建Vivado 免费标准版 vs 企业版Vivado Windows 安装Vivado 安装更新 Vivado 工程操作GUI 创建工程打开已有工程从已有工程创建, 重命名工程GUI导出TCL, TCL复原工程TCL命令 Vivado 版本控制BlinkTcl脚本新建导出重建工程纯Verilog BlinkTcl脚本生成位流文件Tcl脚本编程

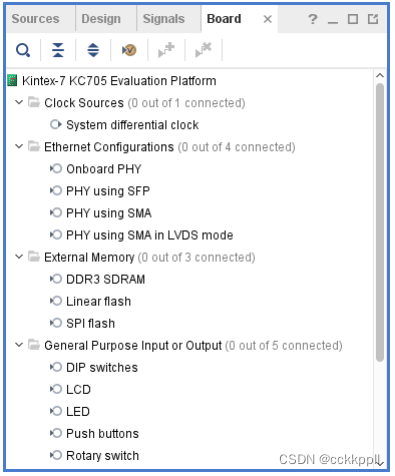

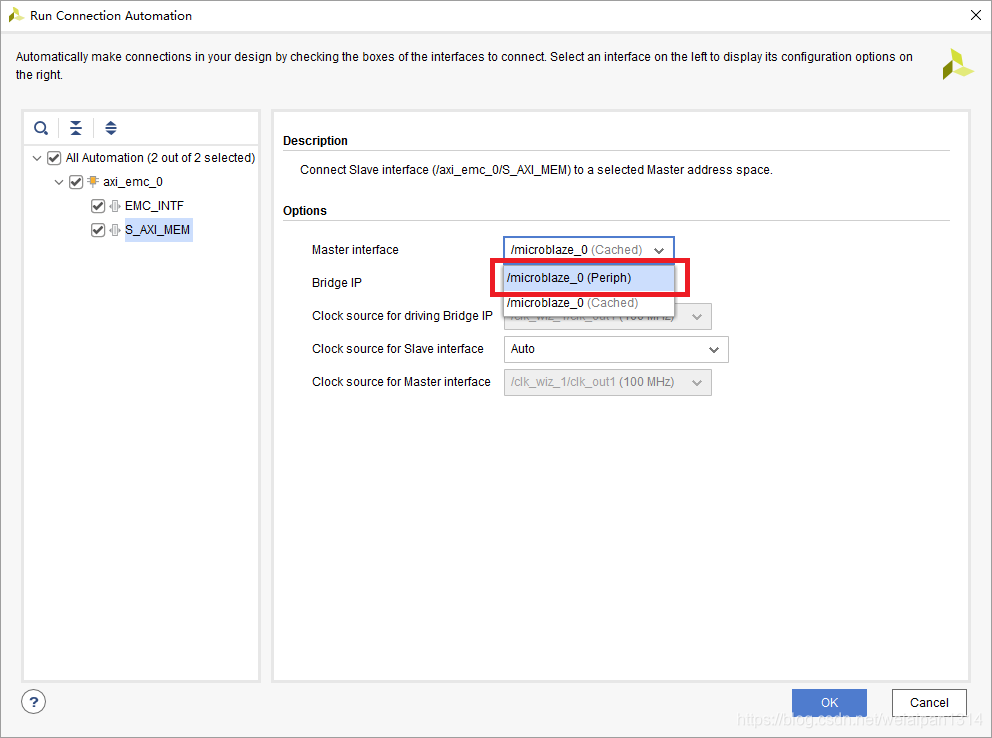

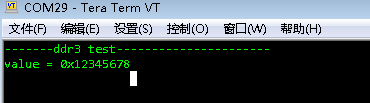

Virtex7 Microblaze下DDR3测试

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。 新建工程,FPGA选型为xc7v690tffg-1761。1. 创建Block Design,命名为Microblaze_DDR3。

MicroBlaze测试DDR3

我们在平常的调试过程中尤其在进行大批量数据处理时,经常需要缓存大量的数据,虽然较高级别的FPGA都用于大量的片内BlockRAM,但是在算法较为复杂时,BlockRAM依然显得捉襟见肘,外置的SDRAM容量大成本低,为FPGA扩容提供了良好的平台。Xilinx系列FPGA随软件拥有免费的SDRAM控制器,可以很方便的让用户对FPGA进行缓存扩容,而不用费神于如何控制SDRAM的读写时序和自刷新等繁

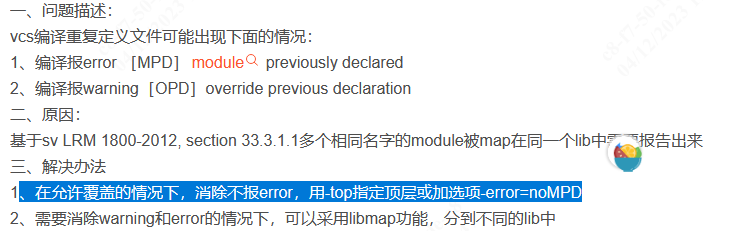

microblaze仿真

verdi+vcs (1) vlogan/vcs增加编译选项 -debug_access+all -kdb -lca (2) 在 simulation 选项中加入下面三个选项 -gui=verdi +UVM_VERDI_TRACE="UVM_AWARE+RAL+HIER+COMPWAVE" +UVM_TR_RECORD 这里 -gui=verdi是启动verdi 和vcs联合仿真。+

【【水 MicroBlaze 最后的介绍和使用】】

水 MicroBlaze 最后的介绍和使用 我对MicroBlaze 已经有了一个普遍的理解 了 现在我将看的两个 一个是 AXI4接口的 DDR读写实验 还有一个是 AXI DMA 环路实验 虽然是 水文 但是 也许能从中 得到一些收获 第一个是 AXI DDR 读写实验 Xilinx 从 Spartan-6 和 Virtex-6 系列开始使用 AXI 协议来连接 IP 核。在 7 系列器

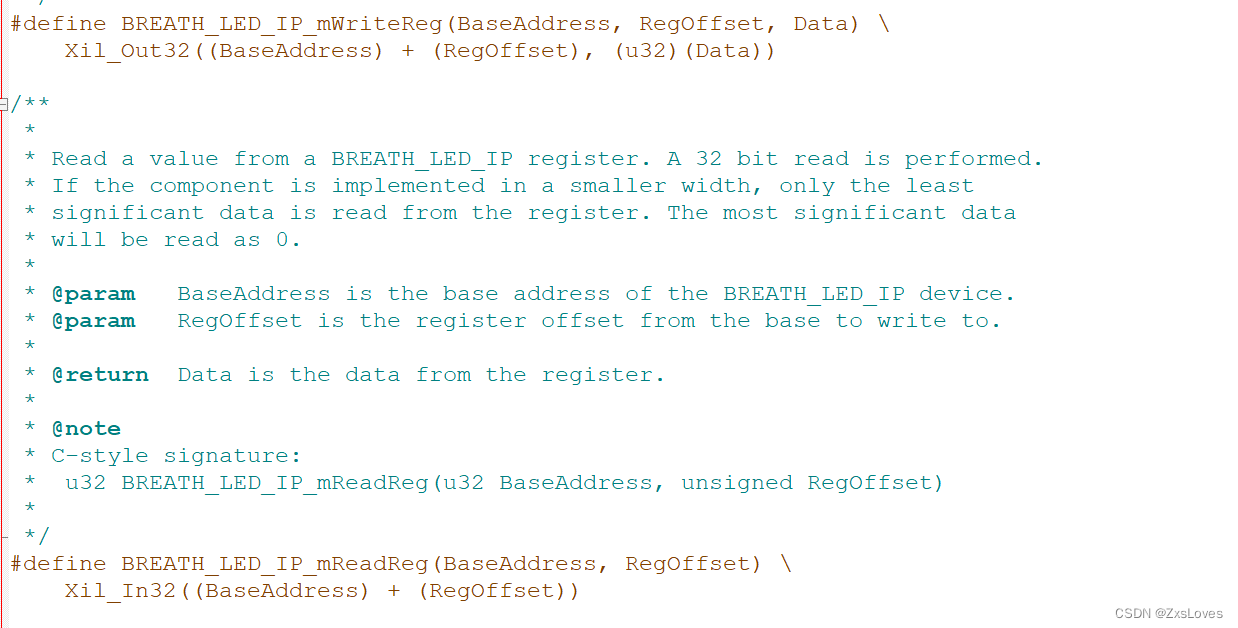

【【FPGA 之 MicroBlaze 自定义IP核 之 呼吸灯实验】】

FPGA 之 MicroBlaze 自定义IP核 之 呼吸灯实验 通过创建和封装 IP 向导的方式来自定义 IP 核,支持将当前工程、工程中的模块或者指定文件目录封装成 IP 核,当然也可以创建一个带有 AXI4 接口的 IP 核,用于 MicroBlaze 软核处理器和可编程逻辑的数据通信。本次实验选择常用的方式,即创建一个带有 AXI 接口的 IP 核,该 IP 核通过 AXI协议实现 Mi

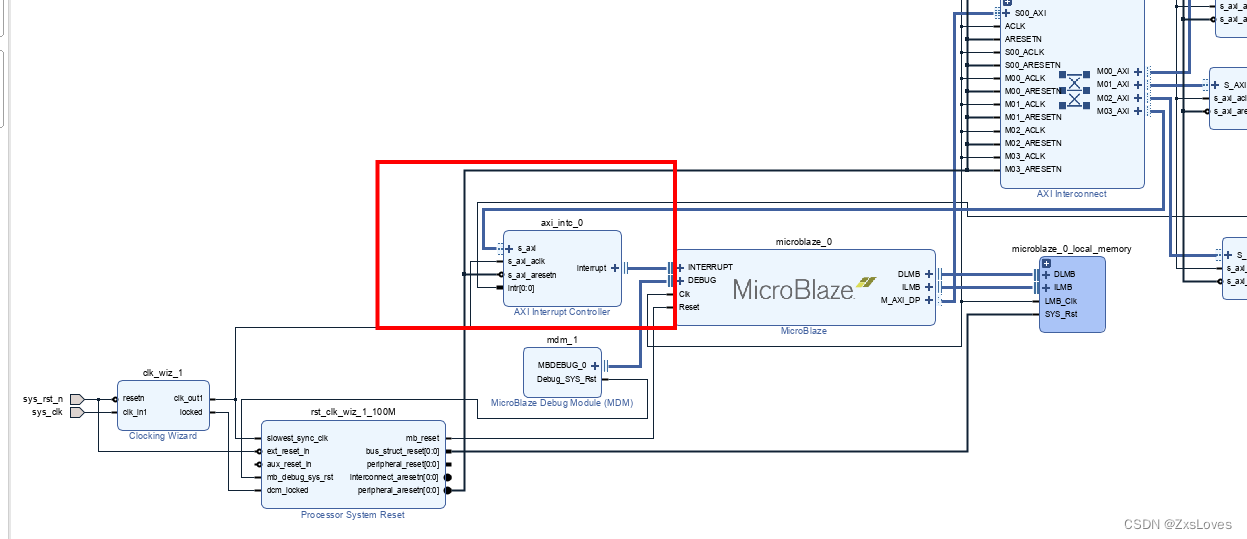

【【FPGA中断的介绍附上 上个MicroBlaze 代码的解析】】

FPGA中断的介绍附上 上个MicroBlaze 代码的解析 我们 先附带上上一节 Micro Blaze 的 blockdesign 结构 和 代码 本次实验参考自 正点原子达芬奇开发板 Micro Blaze 开发 我们 可以看出 我们圈画了一个中断控制器IP 还有一个是我们构建的软核 micro blaze 和挂载的BRAM 用来当作原本内核的 DDR 存储 我之前用的是 带硬核的

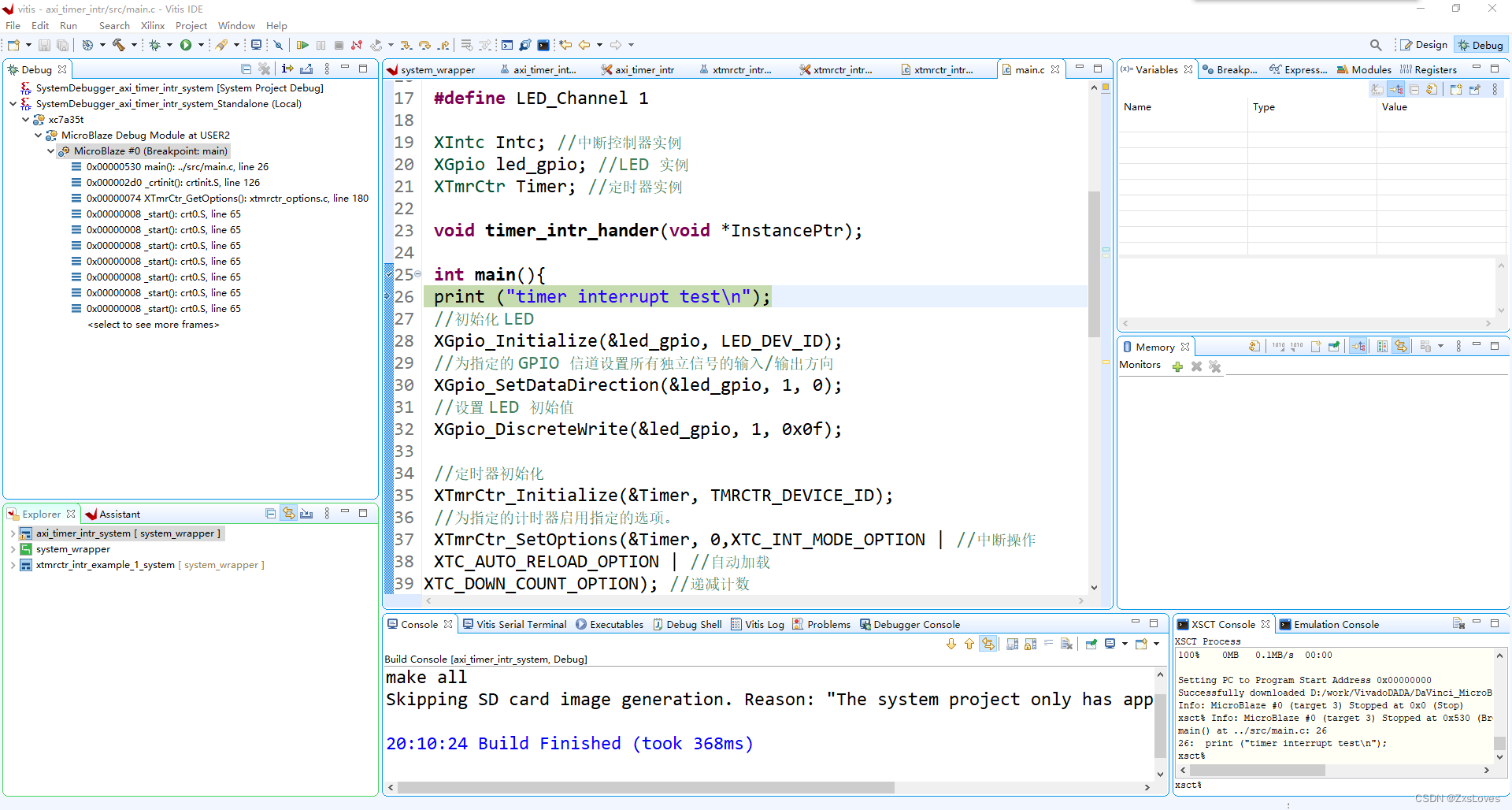

【【FPGA 之 MicroBlaze定时器中断实验】】

FPGA 之 MicroBlaze定时器中断实验 AXI Timer 具有 AXI 总线接口,能够产生不同时间周期和占空比的时钟、脉冲产生电路、产生与时间有关的中断和用于电机控制的脉宽调制信号。 AXI Timer IP 核提供了一个 AXI4 Lite 接口用于与处理器通信;它内部有两个可编程的定时器,具有中断、事件生成和事件捕获功能,用户可根据自身需求选择 8、16、32 位定时器的计数宽度

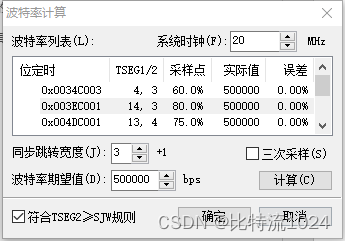

Xilinx microblaze axi can 使用说明

本次主要描述在SDK上如何配置波特率和采样率这两个关键的信息。 XILINX官方提供的驱动包括循环方式和中断方式。配置波特率和采样率主要依靠XCan_SetBaudRatePrescaler和XCan_SetBitTiming这两个函数。主要参数: #define TEST_BRPR_BAUD_PRESCALAR //分频系数 #define TEST_BTR_SYNCJUMP

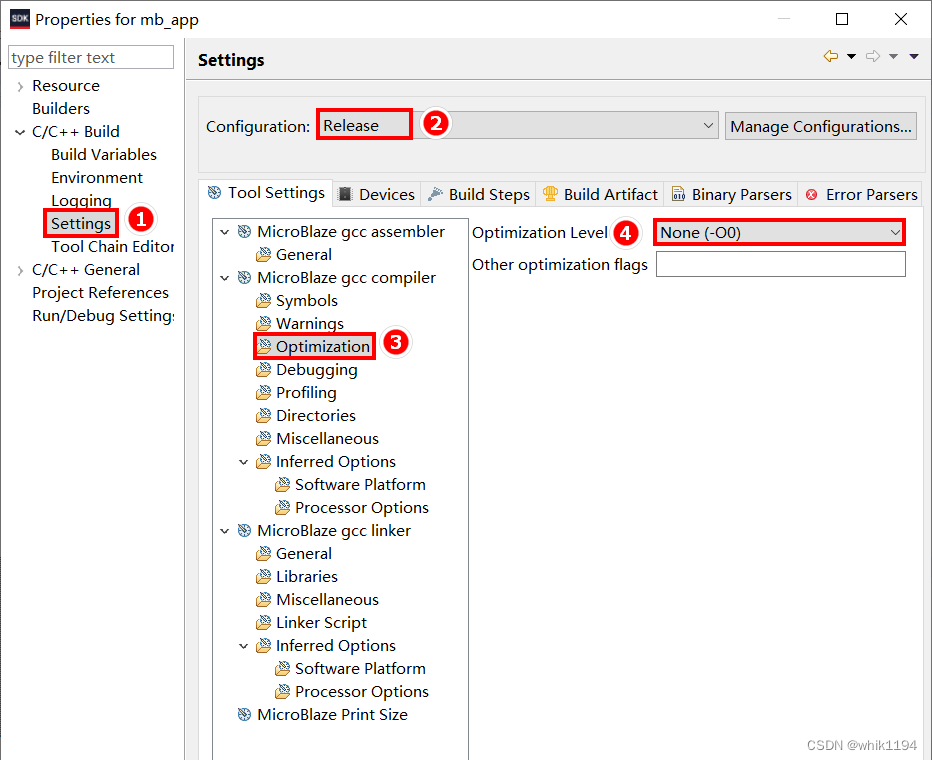

Xilinx MicroBlaze定时器中断无法返回主函数问题解决

最近在使用Xilinx 7系列FPGA XC7A100T时,运行MicroBlaze软核处理器,添加了AXI TIMER IP核,并使能定时器溢出中断,发现定时器触发中断后,无法返回主函数的问题,最后发现修改编译器优化等级就正常了。 FPGA型号是XC7A100T-FGG484,开发环境是Vivado 2018.3。 应用代码大致如下结构: uint32_t cnt_1ms = 0;int