本文主要是介绍Virtex7 Microblaze下DDR3测试,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

- 新建工程,FPGA选型为xc7v690tffg-1761。1. 创建Block Design,命名为Microblaze_DDR3。

- 在bd文件中加入Mircoblaze。

- 点击Run Block Automation

- 按照默认配置,确定即可。

- 出现下面的界面。

- 添加MIG的IP Core

- 开始配置DDR,选择Create Design.

- 这一步是选择Pin脚兼容的FPGA,我们不做选择,直接Next。

- 选择DDR3.

- ①选择DDR的工作频率,我们这里让DDR3的频率为1600MHz,所以时钟频率是800MHz;

②选择器件,根据实际情况来选择即可;

③数据位宽,也是根据板卡上的实际位宽进行选择;

④默认即可。

- 选择AXI总线的位宽,这里我们选择512.

- ①选择输入时钟频率,虽然DDR的工作时钟是800MHz(在第10步中选择),但我们可以输入一个低频时钟,然后MIG的IP Core中会倍频到所需频率。

②MIG的IP Core默认会输出一个200MHz的时钟,如果还需要其他的时钟输出,可以在这里选择。其他选择默认即可。

- ①选择输入时钟的方式,这里的输入时钟就是我们上一个页面中的设置的200MHz的输入时钟,如果选择差分或单端,则输入通过FPGA的管脚输入200MHz时钟到MIG的IP Core;如果选择No Buffer,则可以通过FPGA内部的MMCM输出一个200MHz时钟到MIG;这里我选择了No Buffer;

②选择参考时钟的方式,参考时钟频率固定是200MHz,如果选择如果选择差分或单端,则输入通过FPGA的管脚输入200MHz时钟到MIG的IP Core;如果选择No Buffer,则可以通过FPGA内部的MMCM输出一个200MHz时钟到MIG;如果在前一个页面中选择了输入时钟频率是200MHz,则这边会出现一个Use System Clock的选项,因为此时两个时钟频率是相同的嘛。这里我选择了Use System Clock;

③设置输入复位信号的极性,这个要特别注意,尽量选择高有效,因为无论我们选择高复位还是低复位,它的端口名都叫sys_rst,会让人直观就觉得是高复位。我第一次使用时,就没注意到这个选项,默认为低,但在MIG的端口上看到sys_rst这个名字我以为是高有效,结果DDR一直不通。

(备注:对于绝大多数的Xilinx的IP,如果是低有效的复位,端口名字中肯定是有N这个标志的)

- 这个页面不需要操作。

- 下面开始分配管脚,我比较习惯于选第二个,无论是第一次分配还是后面再重新分配。

- 在这一页,可以根据原理图一一分配管脚;如果有现成的xdc/ucf文件,可以直接通过Read XDC/UCF读入,然后再选择Validate验证管脚分配是否正确。

如果Validate成功,则会提示下面的界面。

- 如果在第13步中,选择了差分或单端输入,则这里会出现下面第一个图;如果选择了No buffer,则这里会出现第二个图。很容易理解,如果选择了通过外部管脚输入时钟,那这里就是让选择具体的管脚。并不是所有的MRCC或者SRCC管脚都可以选的,只能选择跟DDR管脚同一片区域的(比如DDR放在了Bank31 32 33,那么这里的时钟输入管脚就不能选择Bank15)。

如果不选择复位信号管脚,就可以通过FPGA内部逻辑来输入复位。

后面一路Next就完成了MIG IP Core的配置了。

- 在bd文件中,加入AXI Interconnect、UARTLite和Interrupt(如果不加中断模块,Microblaze的程序跑不起来),串口用来打印信息。然后再添加各输入输出端口,把内部的线连接起来,如下图所示。

但这个图里的线太多,看着不直观,我们把Microblaze模块、mdm_1、rst_clk_wiz和local_memory模块(上图中红框中的4个模块)放到一个子模块中,取名mb_min_sys,如下图。

-

创建顶层的top文件,并在top文件中例化bd文件。可以把init_calib_complete和mmcm_locked这两个信号抓出来,在下载程序后,这两个信号必须都是高,不然DDR就工作不正常,肯定是中间某个环节配置有问题。具体top.v文件内容见附录

-

将工程综合、实现、生成bit文件,并导出Hardware。

- 打开sdk,新建Application Project,并按下面的步骤依次操作。

再选择模板为HelloWorld,最后Finish。

- 修改helloworld.c,见附录,重新编译,如果提示overflowed则把lscript.ld文件中的size改大。

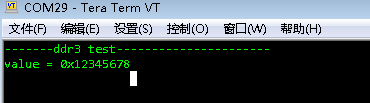

运行程序后,可以看到串口打印信息如下:

附录

// top.v

`timescale 1ns / 1psmodule top(input clk_n,input clk_p,input UART_rxd,output UART_txd,output [15:0]ddr3_addr,output [2:0]ddr3_ba,output ddr3_cas_n,output [0:0]ddr3_ck_n,output [0:0]ddr3_ck_p,output [0:0]ddr3_cke,output [0:0]ddr3_cs_n,output [7:0]ddr3_dm,inout [63:0]ddr3_dq,inout [7:0]ddr3_dqs_n,inout [7:0]ddr3_dqs_p,output [0:0]ddr3_odt,output ddr3_ras_n,output ddr3_reset_n,output ddr3_we_n);wire axi4_clk;wire axil_clk;reg axi4_rstn;wire axil_rstn;wire init_calib_complete;wire mmcm_locked;wire ddr_rst;always @ ( posedge axi4_clk )beginaxi4_rstn <= axil_rstn;end reg [8:0] cnt;always @ ( posedge axil_clk )beginif(~axil_rstn)cnt <= 'd0;else if(cnt=='d256)cnt <= cnt ;else cnt <= cnt + 1'b1;end assign ddr_rst = (cnt=='d256)?1'b0:1'b1;MicroBlaze_DDR3 MicroBlaze_DDR3_i(.UART_rxd (UART_rxd ),.UART_txd (UART_txd ),.axil_clk (axil_clk ),.axi4_clk (axi4_clk ),.axi4_rstn (axi4_rstn ),.clk_in_clk_n (clk_n ),.clk_in_clk_p (clk_p ),.ddr3_addr (ddr3_addr ),.ddr3_ba (ddr3_ba ),.ddr3_cas_n (ddr3_cas_n ),.ddr3_ck_n (ddr3_ck_n ),.ddr3_ck_p (ddr3_ck_p ),.ddr3_cke (ddr3_cke ),.ddr3_cs_n (ddr3_cs_n ),.ddr3_dm (ddr3_dm ),.ddr3_dq (ddr3_dq ),.ddr3_dqs_n (ddr3_dqs_n ),.ddr3_dqs_p (ddr3_dqs_p ),.ddr3_odt (ddr3_odt ),.ddr3_ras_n (ddr3_ras_n ),.ddr3_reset_n (ddr3_reset_n ),.ddr3_we_n (ddr3_we_n ),.ddr_rst (ddr_rst ),.init_calib_complete (init_calib_complete ),.mmcm_locked (mmcm_locked ),.reset (1'b0 ),.axil_rstn (axil_rstn ));

endmodule// helloworld.c

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"int main()

{init_platform();print("-------ddr3 test----------------------\n\r");unsigned int *DDR_MEM = (unsigned int*) XPAR_MIG_7SERIES_0_BASEADDR;// write data to ddr3*DDR_MEM = 0x12345678;// read backunsigned int value = *(unsigned int *) XPAR_MIG_7SERIES_0_BASEADDR;xil_printf("value = 0x%x\n", value);cleanup_platform();return 0;

}欢迎关注:

个人主页:http://www.technomania.cn

微信公众号:Quant_Times

Reading_Times

这篇关于Virtex7 Microblaze下DDR3测试的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!