jtag专题

isp jtag 串口 区别与原理

单片机编程器和开发板下载的区别 2009-11-10 08:35 woshijiqiren1 | 分类:嵌入式 | 浏览1501次 单片机编程器 和开发板 的下载功能有什么本质的区别吗 我现在的麻烦事sste516rd芯片不能仿真,据说是内部程序掉了,我用开发板下载仿真程序就去,显示找不到芯片,查了一下说是要用编程器少些才行,请教给为了,刚学单片机,见笑了,希望答案全面点,会有加分

查了查jtag和串口的区别

能用串口下载程序的单片机,其内部一般都有boot程序的支持,boot程序将要下载的数据通过串口接收到单片机之后调用boot中的flash编程程序,写到内部的flash中,也有用串口调试的,就看单片机的boot程序做的咋样了,O(∩_∩)O哈哈~,jtag是一种标准的调试扫面接口,完全硬件实现,需要单片机内部有jtag的硬件调试单元和外面的仿真器进行通信,既能调试又能下载,单片机功能较简单,所以低端

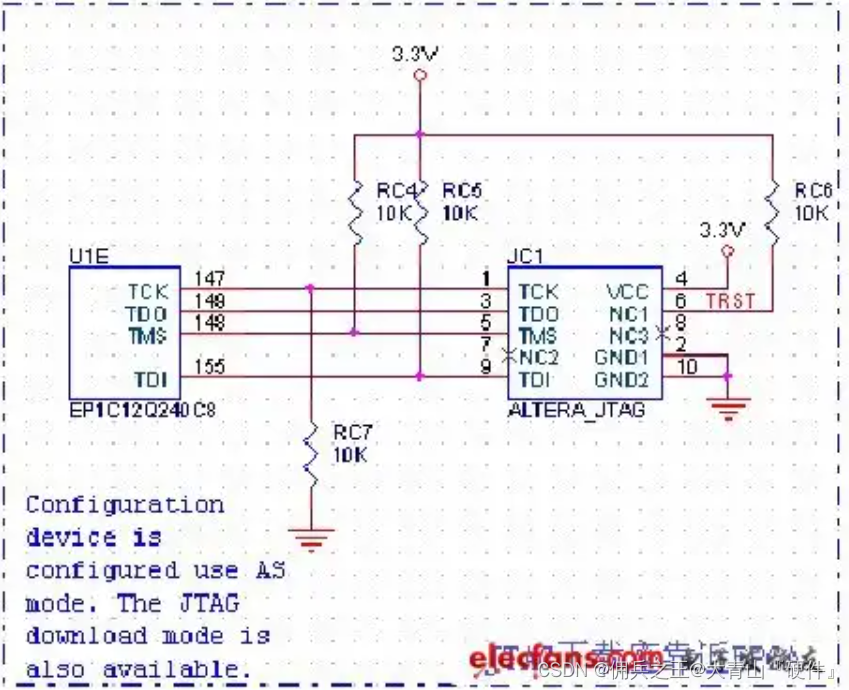

Altera的JTAG电路下载模块为何上下拉电阻,不可不知的秘密

一、FPGA背景信息 当前的FPGA市场上有国际和国产两大体系,国际排名,一直很稳定,国际上前三名Xilinx、Altera、Lattice,国内FPG厂商也在填补空白,低端、中低端市场上发力,替代潮流已在兴起,目前国内前五,分别是京威齐力、安路科技、广州高云、复旦微电子、西安智多晶,国货当自强,真的很厉害。 FPGA随着人工智能、大数据、云计算、数据中心而越发收到重视,对于我们硬件工程师来说

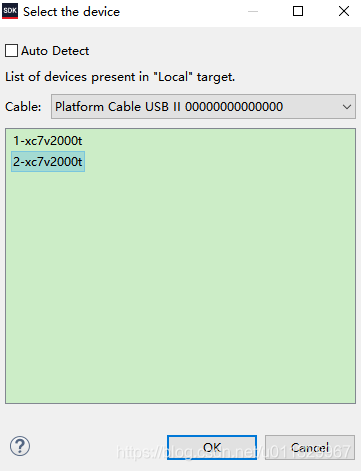

多个FPGA挂在同一个JTAG下去调试Microblaze时

当我们的系统存在多个FPGA挂在同一个JTAG下去调试Microblaze时,默认会出现: 此时需要先选定FPGA设备,才可以进行正常Debug操作:

jtag 与 swd 的异同

JTAGSWD提出组织JTAGARM功能调试/边界扫描调试引脚数量8至20个2个适用场合ARM的cortex-a/FPGA/DSPARM所有的soc/AP

jtag 调试中 提供给用户的命令接口

jlink 提供了 cmdopenocd 提供了 telnet , telnet 提供了 cmdgdb 提供了 cmd 1.jlink 的cmd 参考手册 https://wiki.segger.com/J-Link_Commander具体还是要看 UM08001.pdf , 即 J-Link-J-Trace-User-Guide实例 可参考 https://blog.csdn.net

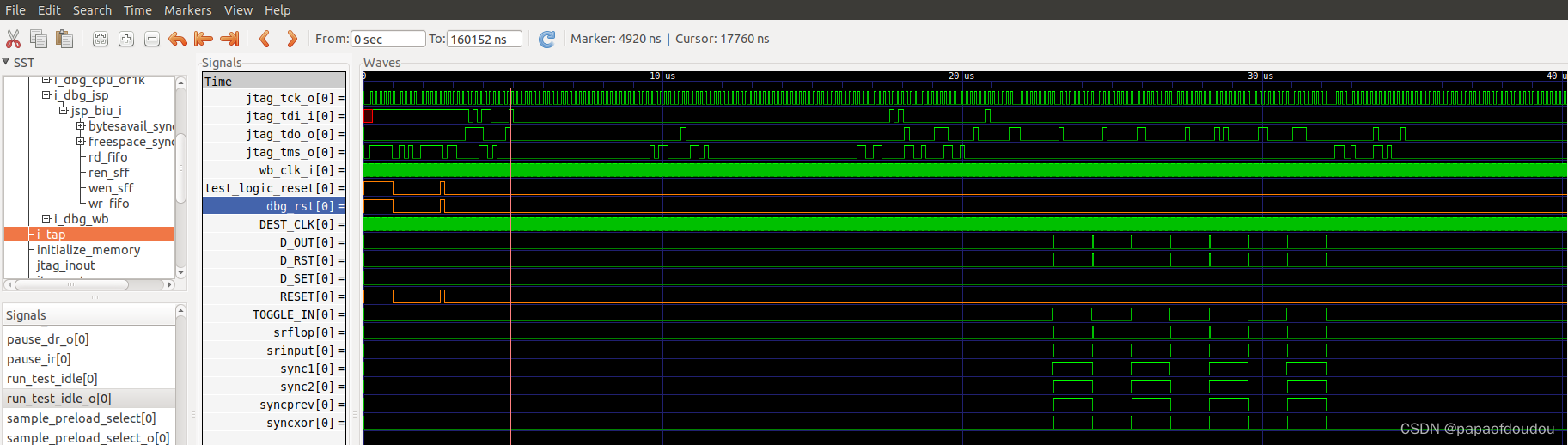

openocd riscv 对应的jtag动作解析

openocd 服务器开启时1.探测存在的核心2.halt住核心3.读misa4.resume核心5.循环查询dmstatus traget remote时1.halt住核心2.读了X0-X31和PC2.读各种CSR寄存器(TODO) disconnect 时1. resume request openocd 服务器 被ctrl-c 结束时1. resume req

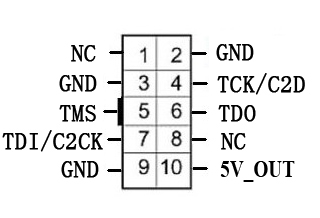

JTAG/C2 接口定义

JTAG/C2 接口定义 C8051F的JTAG接口是如何定义的? JTAG接口如下:(适用型号C8051F00x C8051F01x C8051F02x C8051F04x C8051F06x C8051F12x C8051F2Xx) 端口号JTAG接口备注1- 2GND 3GND 4TCK 5TMS 6TDO 7TDI 8- 9GND 10PWR_OUT_5V本公司仿真器对外电5V/50

【INTEL(ALTERA)】采用 JTAG 频率为 24MHz 或 16Mhz 的非流水线Nios® V/m 处理器,niosv-download 失败

说明 在英特尔® Quartus® Prime Pro Edition 软件 23.3 版及更高版本中将 Nios® V 处理器软件下载到非流水线Nios® V/m 处理器时,可能会出现此问题。 这是由于处理器限制,仅影响非流水线Nios® V/m 处理器。 以下其他处理器不受此限制的影响: 管道式 Nios® V/m 处理器Nios® V/g 处理器 解决方法 要变通解决此问题,

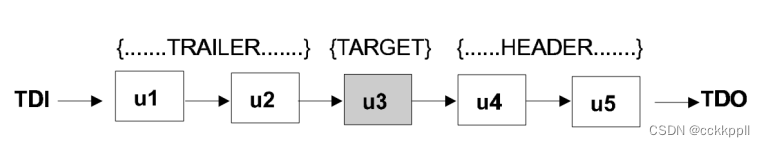

vivado 低级别 SVF JTAG 命令

低级别 SVF JTAG 命令 注释 : 在 Versal ™ 器件上不支持 SVF 。 低级别 JTAG 命令允许您扫描多个 FPGA JTAG 链。针对链操作所生成的 SVF 命令使用这些低级别命令来访问链中的 FPGA 。 报头数据寄存器 (HDR) 和报头指令寄存器 (HIR) 语法 HDR length

STM32 JTAG与ISP区别

JTAG是Joint Test Action Group(联合测试行动小组)的缩写,是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。JTAG用来对芯片进行测试的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对内部节点进行测试。标准的JTAG接口是4线:TMS、 TCK、TDI、TDO,分别为模式选择、时钟、数

调试系统及ARM CPU挂死和总线挂死的DS-5(JTAG)调试方法

DFT和JTAG的关系 DFT(Design for Testability)和JTAG(Joint Test Action Group)是与电子设计和测试领域相关的两个重要概念,它们之间有一定的关联。 DFT(Design for Testability): DFT是一种设计方法,旨在使电子芯片或电路板更容易进行测试和诊断。DFT的目标是在设计阶段考虑测试需求,以提高产品的可测试性、可维护

创龙TI TMS320C6748定点/浮点DSP C674x开发板硬件电源接口和拔码开关、JTAG仿真器接口

TL138/1808/6748-EVM是广州创龙基于SOM-TL138/1808/6748核心板开发的一款开发板。由于SOM-TL138/1808/6748核心板管脚兼容,所以此三个核心板共用同一个底板。开发板采用核心板+底板的设计方式,尺寸为18cm*13cm,它主要帮助开发者快速评估核心板的性能。 核心板采用高密度6层板沉金无铅设计工艺,尺寸为55mm*33mm,板载3路转换率很高的DC-D

TI KeyStone C66x开发板千兆以太网口、JTAG接口

TL6678F-EasyEVM是广州创龙基于SOM-TL6678F核心板而研发的一款多核高性能DSP+FPGA开发板。开发板采用核心板+底板方式,底板采用沉金无铅工艺的8层板设计,尺寸为247.33mm*139.8mm,它为用户提供了SOM-TL6678F核心板的测试平台。为了方便用户开发和参考使用,上面引出了各种常见的接口,可以帮助用户快速评估SOM-TL6678F核心板的整体性能。 广州创龙

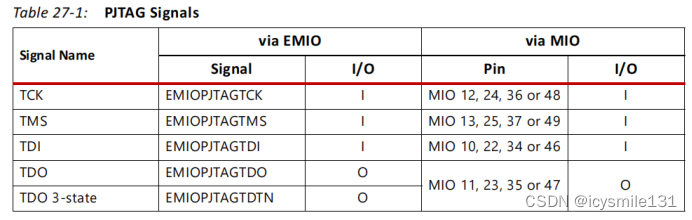

Zynq 7000 系列中的JTAG和DAP子系统

Zynq 7000系列SoC器件通过标准JTAG调试接口提供调试访问。在内部,SoC设备器件在处理系统(PS)内部实现了一个Arm调试访问端口(DAP),同时在可编程逻辑(PL)内部实现了一个标准的JTAG测试访问端口(TAP)控制器。作为Arm CoreSight调试架构的一部分,Arm DAP允许用户利用行业标准的第三方调试工具。 除了标准JTAG功能外,AMD TAP控制器还支持一系列PL功

ESP32S3在wsl环境的JTAG、openocd仿真调试

文章目录 一、准备工作二、添加 ESP-IDF 环境变量三、添加 udev 规则文件四、vscode 配置 一、准备工作 安装配置好 WSL、ubuntu, 参考连接: WSL2安装Ubuntu迁移到其他盘或者其他电脑_wsl ubuntu迁移-CSDN博客 WSL2 设置桥接模式_wsl2 桥接-CSDN博客 下载好 WSL-USB 参考连接 WSL2 Ubuntu装ESP

31---JTAG电路设计

视频链接 JTAG电路设计(JLINK&XILINX&ALTERA)_哔哩哔哩_bilibili JTAG电路设计 1、JTAG简介 JTAG(Joint Test Action Group):联合测试工作组,是在名为标准测试访问端口和边界扫描结构的IEEE的标准1149.1的常用名称。 JTAG是一种国际标准测试协议,主要用于芯片内部测试;验证设计与测试生产出的印刷电路板。 现在多数

单片机烧录方式,JTAG,ISP,SWD,

常见的词汇 参考 ISP:In System Programing,在系统编程 IAP:In Application Programing,在应用编程 ICP:In Circuit Programing,在电路编程 ICSP全称是In Circuit Serial Programming JTAG(Joint Test Action Group)编程:通过JTAG协议进行编程 SWD(Seria

单片机SWJ 调试端口(SW-DP和JTAG)、SWD下载电路

单片机下载接口是指用于将编写好的程序代码下载到单片机芯片中的接口。常见的单片机下载接口包括以下几种: 1. **串口下载接口**:通过串口(如UART或RS-232接口)与计算机或下载器相连,将程序代码通过串口传输到单片机内存中。串口下载接口简单易用,适合于一些简单的单片机应用。 2. **USB下载接口**:通过USB接口与计算机相连,利用USB通信协议进行数据传输,将程序代码下载到单片

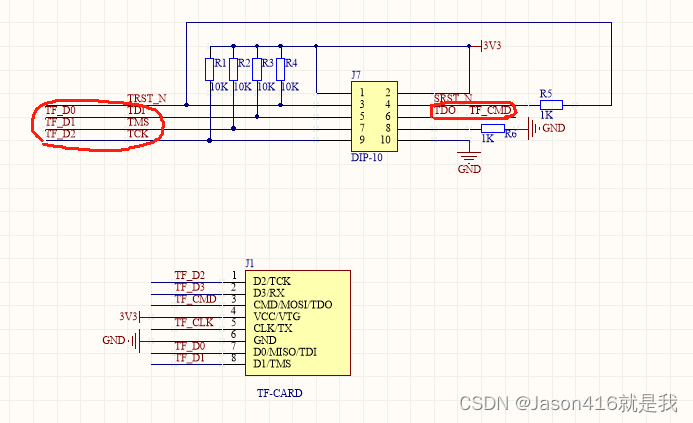

平头哥IP核C906的JTAG调试器DIY教程(一)

背景 最近买了一块基于平头哥C906核,SOC为全志的D1s,的核心板,手工焊接在白嫖的底板上(此处感谢百问网老师的友情支持,手动狗头)。在焊接完成后,进行点亮跑程序的时候,发现没有优雅的调试方法,只能用串口调试的方法,无法追踪程序在核心上的运行流程。 因此基于上面的问题,咨询了一下,老师转发了SD转JTAG的PCB文件,打开后发现上面有WHYCAN.COM的链接,百度搜索相关关键字,便查找到了

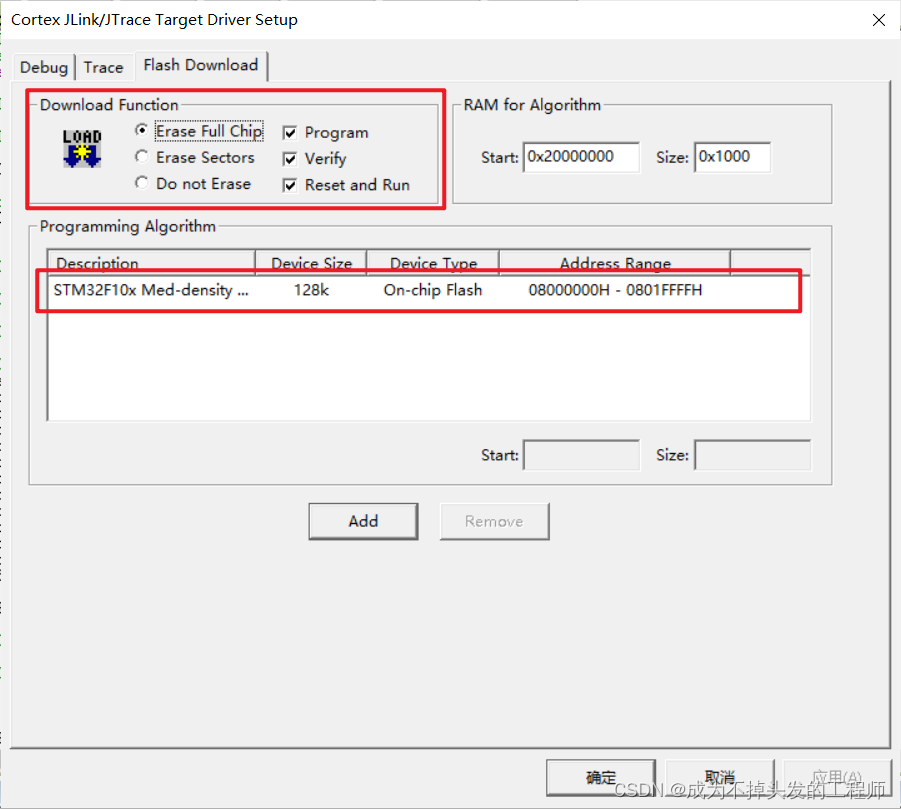

烧录错误***JLink Error: Debugger tries to select target interface JTAG.

一、错误描述: ERROR: Debugger tries to select target interface JTAG.This interface is not supported by the connected emulator. Selection will be ignored by the DLL. Unknown Error. Error:Target DLL has

基于JTAG对ESP32-C3的调试及下载

前言 继上一章节《基于VSCODE的ESP32C3开发环境的搭建》之后,小编相信大部分读者借助红旭的肩膀,应该可以轻松地搞定ESP32-C3的开发环境搭建,并完成一些基础的开发;接下来,让我们继续趁热打铁,讲讲如何利用ESP32-C3的JTAG接口,对ESP32-C3进行下载或者调试仿真。 JTAG接口 为了更好地阐述并实现对ESP32-C3进行下载或者调试仿真,这里小编以HX-DK-商为蓝

STM32F103C8T6在aduino IDE编程使用 jtag模式 下载

1、准备好相关硬件 2、arduino环境搭建参考前文https://blog.csdn.net/qq_38288618/article/details/90553252 3、接线参考看前文https://blog.csdn.net/qq_38288618/article/details/98640223 4、arduino ide相关设置,如图 5、找个示例编译成功,下载出

Quartus FPGA JTAG配置芯片固化(Cyclone IV)

Cyclone IV配置芯片固化 FPGA有三种配置下载方式:主动配置方式(AS),被动配置方式(PS)和最常用的基于JTAG的配置方式。AS和PS模式主要是将比特流下载到配置芯片中(即一次烧录后,断电后代码不会消失),而JTAG模式既能将代码下载到FPGA中直接在线运行(速度快,调试时优选),也能通过FPGA将比特流下载到配置芯片中。 这里介绍在Quartus中如何使用JTAG固化配置芯片。

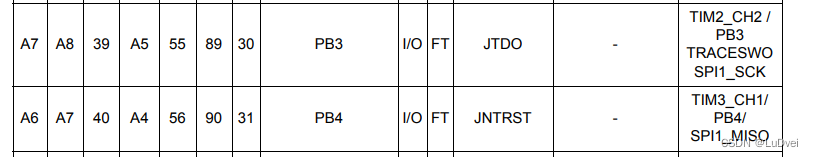

STM32_JTAG引脚及复用代码

目录 1.JTAG引脚1.1 说明(可以不看)1.2 引脚 2.复用代码3. 手册介绍(可以不看) 总是忘记有些引脚是JTAG复用的,导致偶尔浪费一些时间,记录一下。 1.JTAG引脚 1.1 说明(可以不看) STM32的JTAG引脚通常包括TCK、TDI、TDO、TMS以及可选的TRST。 JTAG(Joint Test Action Group)是一种国际标准的调试接

关于JTAG引脚设置为普通IO口

转自https://blog.csdn.net/wang370064915/article/details/8176363 简介 STM32单片机中的JTDO与JNTRST是JTAG引脚复用,一般最好不用JTAG-DP调试端口,而是用SW-DP,只需要JTMS/SWDIO与JTCK/SWCLK。这样可以省下有限的IO资源。 但是stm32复位后,JTAG与SW默认同时开启的,即所有的JTAG