ddr5专题

海力士A-DIE颗粒内存条震撼发布:毁灭者星际战舰DDR5内存条登场

**海力士A-DIE颗粒内存条震撼发布:毁灭者星际战舰内存条登场** 近日,海力士正式发布了全新一代A-DIE颗粒内存条——毁灭者星际战舰DDR5 7200RGB电竞内存条。这款内存条凭借其卓越的性能和先进的技术,成为数码爱好者关注的焦点。 导语: 海力士在内存领域一直保持着领先地位,此次发布的毁灭者星际战舰内存条,更是其技术创新的结晶。该产品采用了最新的A-DIE颗粒技术,旨在

SK Hynix明年将开发基于96/128 GB DDR5的CXL 2.0内存解决方案

SK Hynix 正致力于为人工智能领域开发基于 DDR5 的 CXL 2.0 内存解决方案,尤其是针对"内存饥渴型"LLM。CXL 指的是 Compute Express Link,这是一种互联技术,可以在 CPU 和 GPU 之间实现更快的数据传输,但在人工智能领域,它实际上是 CPU 和加速器之间的数据传输。 与传统的 PCIe 接口相比,CXL 的优势在于它能让 GPU 直接访问系统内

[DDR5 Jedec] 读操作 Read Command 精讲

依公知及经验整理,原创保护,禁止转载。 专栏 《深入理解DDR》 Read 读取命令也可以视为列读取命令。当与正确的bank地址和列地址结合使用时,通过激活命令(行访问)移动到检测放大器中的数据, 现在被推送到数据总线上。 DRAM 通常包括一个“读取和自动预充电”命令,该命令执行列读取,然后关闭/预充电行。这样,就不需要发出单独的预充电命令。如果需要访问同一行,但需要访问不同的列,则根

Linux环境下测试服务器的DDR5内存性能

要在Linux环境下测试服务器的DDR5内存性能,可以采用以下几种方法和工具: ### 测试原理 内存性能测试主要关注以下几个关键指标: - **带宽**:内存每秒能传输的数据量。 - **延迟**:内存访问请求从发出到完成所需的时间。 - **稳定性**:内存能否在高压条件下无错误地工作。 ### 工具推荐 #### 1. MemTest86+ MemTest86+ 是一个知名的内存测试

Stream与MLC测试CPU内存DDR5的原理与方法详解

在高性能计算和服务器领域,内存性能是决定整体系统性能的关键因素之一,特别是随着DDR5内存的普及,其更高的带宽和更低的延迟特性使得内存性能测试变得更加重要。本文将详细介绍使用Stream和MLC两种工具对CPU内存DDR5进行性能测试的原理和实施方法。 #### Stream测试原理与方式 **原理:** Stream是由John D. McCalpin博士开发的一款开源内存带宽测试程序,它通

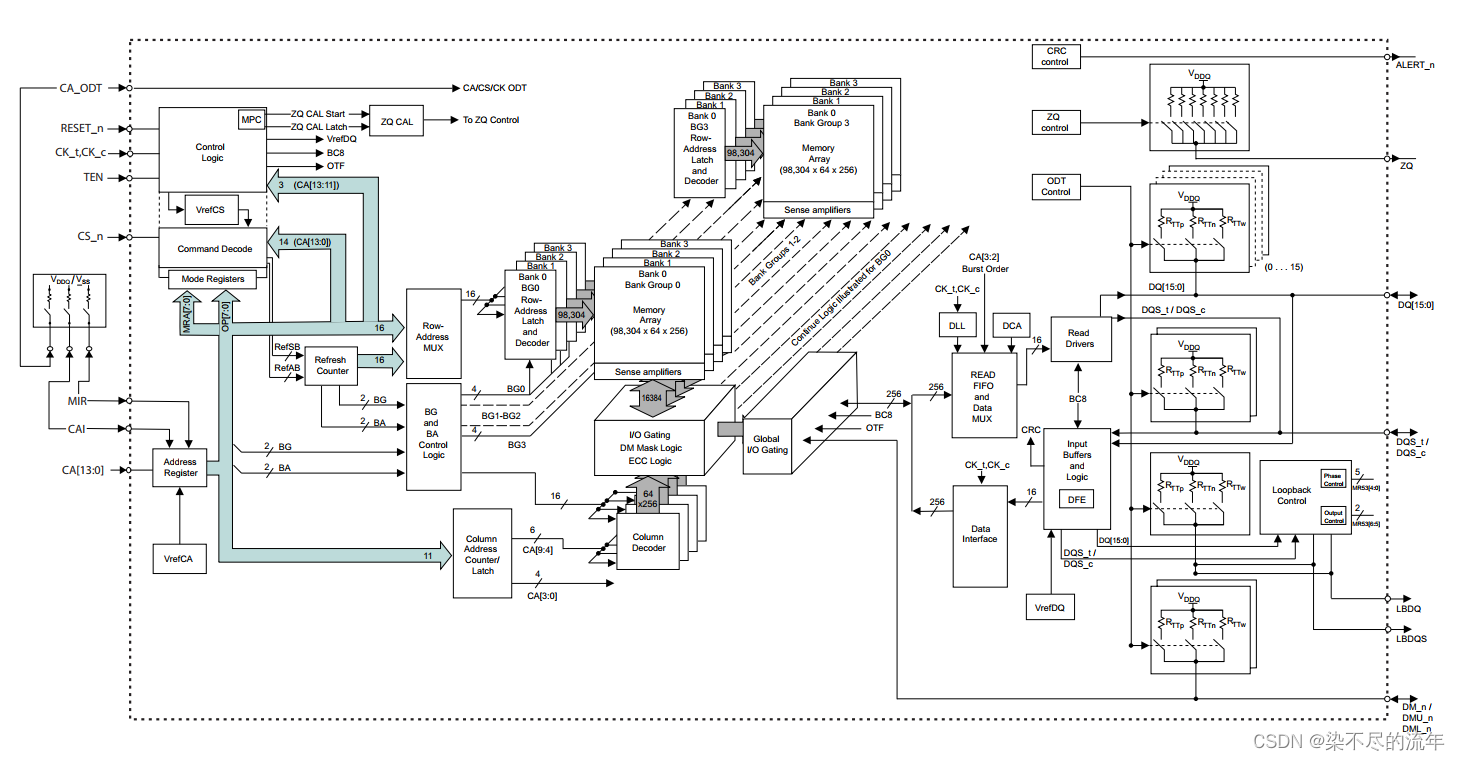

DDR5芯片系统框图详解

DDR5 SDRAM(双倍数据率五代同步动态随机存取存储器)的功能框图详细展现了其内部结构和各个关键模块,这些模块协同工作以实现高速数据传输和存储管理。以下是主要组成部分的详细介绍: Controller Logic (控制器逻辑) 这是DDR5内存系统的大脑,负责接收来自CPU或SoC的指令,解码这些指令,并生成适当的控制信号以执行读写操作、初始化、刷新等任务。控制器逻辑还负责管理与内

[DDR5 Jedec 3]DDR5 SDRAM 状态图 和 基本功能

3000字, 依公知及经验整理,原创保护,禁止转载。 专栏 《深入理解DDR》 3.1 简化状态图 来源: Jedec Proposed DDR5 Full spec 缩写功能ACT激活PRE预充电PRE_A全部预充电MRS寄存器集模式REF刷新TEN边界扫描模式ReadRD, RDS4, RDS8Read ARDA, RDS4A, RDS8AwriteWR, WRS4, WRS8

【专篇】DDR5 SDRAM-01总体介绍

概念 DDR5 SDRAM(第五代双倍数据率同步动态随机存取存储器)是一种正在开发的高带宽电脑存储器规格,属于SDRAM家族的存储器产品。DDR5重点提升了DRAM存储的密度和速率,支持单颗64Gbit的DRAM存储芯片,是DDR4最大允许容量(16Gbit)的四倍。DDR5相比DDR4具有更高的数据传输率(速度)、更多的带宽、更低的工作电压和更好的效率。 DDR5支持每列8Gb到64Gb的内

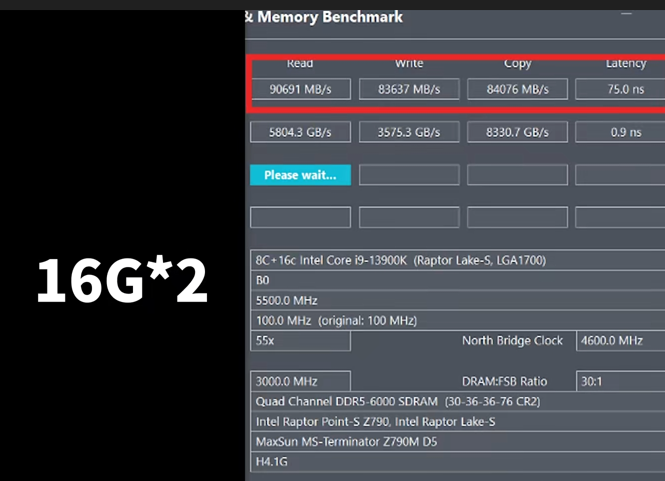

双通道内存@DDR5多通道内存

文章目录 多通道内存DDR4及以前的内存的双通道DDR5往后的双通道和多通道半位宽4通道组合 其他组合测试 DDR5介绍概览重要Features特点 总结 多通道内存 DDR4及以前的内存的双通道 双通道内存是一种内存架构设计,通过在主板上配置两个或多个独立且同时工作的内存控制器通道来实现更高的内存带宽。在双通道模式下,处理器可以同时与两个独立的内存通道进行通信,从而在理论

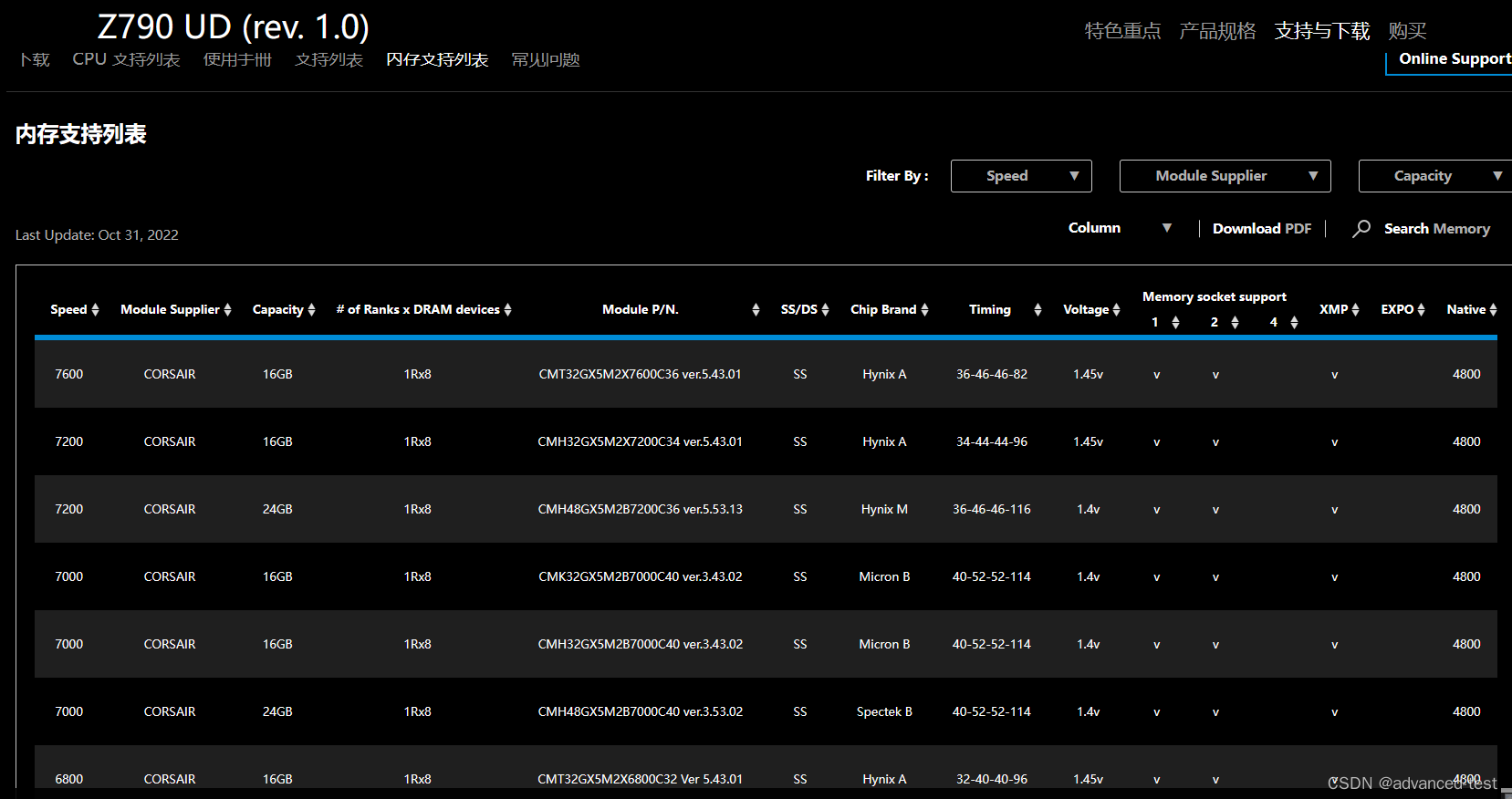

海盗船DDR5版本号VER命名规则

从华硕、技嘉、微星的内存QVL中可总结出如下规律 海盗船DDR5版本号命名规则 第一位数字 颗粒厂商 第二位数字 对应产品类型 第三位数字 DIE数 3 美光 01 A 4 三星 43 传统内存 02 B 5 海力士 53 非传统内存 03 C 04 D 05 E 8 南亚 13

美光证实:DDR5 内存供应不足与 PMIC 和 VRM 短缺有关,2022 年改善的可能性很小

目录 美光证实,由于 PMIC 和 VRM 短缺,DDR5 内存可用性受到阻碍 最近证实,较差的DDR5内存可用性与 PMIC 和 VRM 组件短缺有关

游戏、设计选什么内存条?光威龙武系列DDR5量大管饱

如果你是一位PC玩家或者创作者,日常工作娱乐中,确实少不了大容量高频内存的支持,这样可以获得更高的工作效率,光威龙武系列DDR5内存条无疑是理想之选。它可以为计算机提供强劲的性能表现和稳定的运行体验,让我们畅玩游戏、高效工作,尽情享受数字世界的精彩。 这款内存有着多种版本可以选择,比如6400MHZ 24GB×2版本就很有性价比,时序低至CL32,另外还有6800MHZ 16GB×2,默认时

入手DDR5内存最佳时机到了,价格大跳水香过DDR4

当时 DDR5 内存刚出来那会儿大家怎么说的来着,售价离谱,提升微弱,鬼都不买… 不过嘛,随着 13 代酷睿以及锐龙 7000 系 CPU 上市,DDR5 彻底真香起来了。 先不说花重金升级 13 代酷睿平台,还用 DDR4 会不会有一种逼格差一截儿的感觉; 光锐龙 7000 平台直接不支持 DDR4,来了波强推 DDR5。 最重要的是,经过市场 DDR5 内存需求提升,对

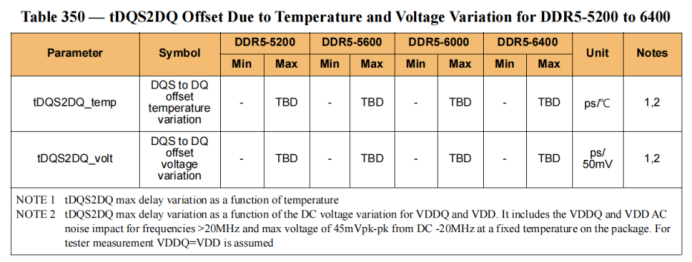

【JESD79-5之】4 DDR5 SDRAM命令描述和操作-32(tDQS2DQ offset due to temperature and voltage variation)

4 DDR5 SDRAM命令描述和操作-32 4.32 因温度和电压变化导致的tDQS2DQ偏移 4.32 因温度和电压变化导致的tDQS2DQ偏移 随着SDRAM芯片上温度和电压的变化,DQS时钟树将会发生偏移,可能需要重新训练。振荡器通常用于测量在给定时间间隔内的延迟量(由控制器确定),使得控制器可以将训练的延迟值与稍后时间的延迟值进行比较。由于温度和电压变化,tDQS2

至强新一代服务器芯片,英特尔新一代服务器处理器真容曝光,支持DDR5内存和PCIe 5.0...

英特尔新一代服务器处理器真容曝光,支持DDR5内存和PCIe 5.0 2020-12-11 14:53:52 2点赞 6收藏 11评论 今年8月时,英特尔在架构日活动上确认,会在明年发布10nm工艺的Sapphire Rapids处理器,全新架构,全新工艺,还支持DD5内存以及PCIe 5.0,是最近近年来变化最大的一代,这也意味着明年英特尔开始大更新,先从服务器平台开始。 今天,业内曝光了首

![[DDR5 Jedec] 读操作 Read Command 精讲](https://img-blog.csdnimg.cn/direct/8d31fad7a28745eb81e253606f226423.png#pic_center)

![[DDR5 Jedec 3]DDR5 SDRAM 状态图 和 基本功能](https://img-blog.csdnimg.cn/direct/1539e07b5b744855a7397a81e7b8ae6f.png)