本文主要是介绍[DDR5 Jedec] 读操作 Read Command 精讲,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

依公知及经验整理,原创保护,禁止转载。

专栏 《深入理解DDR》

Read

读取命令也可以视为列读取命令。当与正确的bank地址和列地址结合使用时,通过激活命令(行访问)移动到检测放大器中的数据, 现在被推送到数据总线上。 DRAM 通常包括一个“读取和自动预充电”命令,该命令执行列读取,然后关闭/预充电行。这样,就不需要发出单独的预充电命令。如果需要访问同一行,但需要访问不同的列,则根本不会发出预充电,并且该行将保持打开状态。要使用 read 命令,CS 和 CAS 被拉低,而 RAS 和 WE 被拉高。

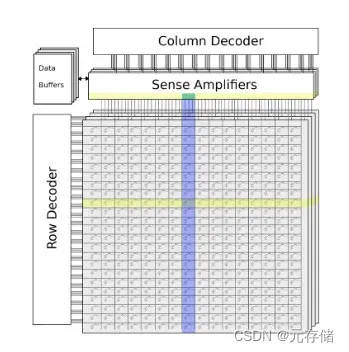

图. 高亮显示Active 和 读操作

图中黄色高亮的行, 是 Active 操作对象。紫色高亮的列, 是读操作的对象。

1.1 Read 过程

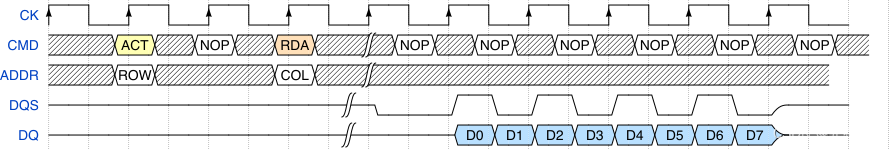

图. 读操作

上图是 BL 为 8 的一组 Read 操作。分为两步骤

- Act 命令线激活 bank 某一行

- 第二步是 RDA(Read 自动预充电读取), 当连续读长度达到 BL(8)后, 读完成, 并自动预充电。

地址位寄存器以及“读取”或“写入”命令用于选择用于突发操作的列。此步骤是 CAS 或列地址选通。由于每个组只有一个感应放大器,因此在移动到第二个行之前必须停用第一个行。这是使用 PRECHARGE 命令完成的。还有其他方便的命令替代品,如 RDA(使用自动预充电读取)和 WRA(使用自动预充电写入)命令,它们会自动处理激活和停用。

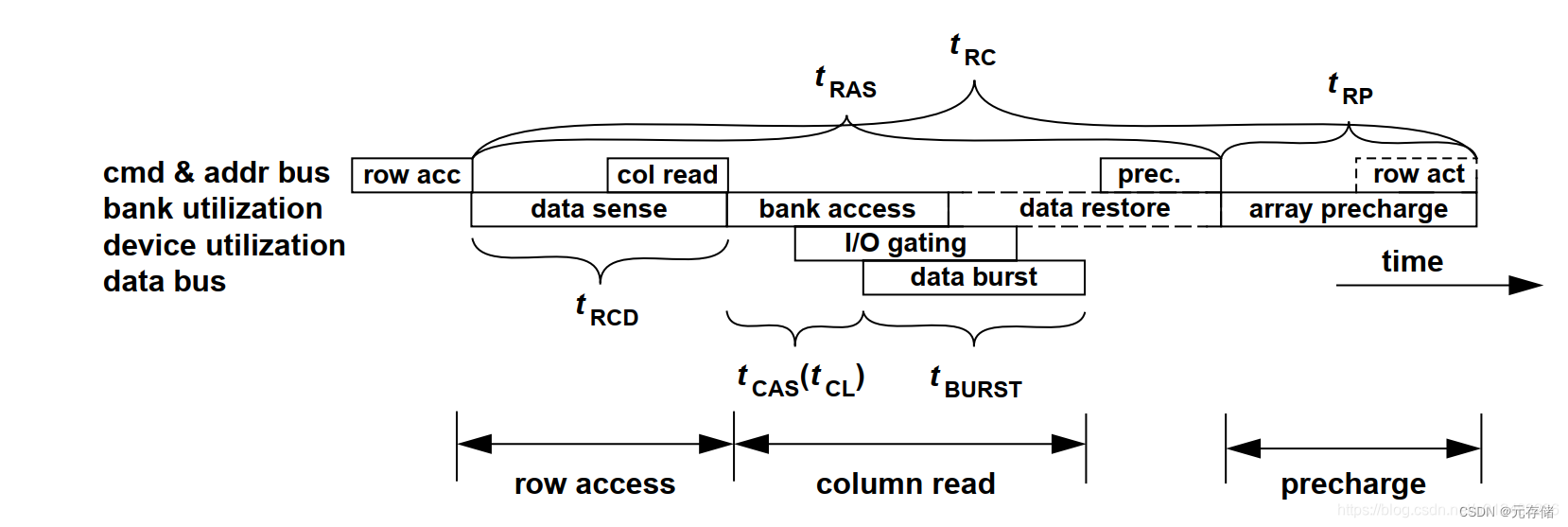

图 完整的 Burst Length 的 Read Cycle

1.2 Read 时序

Read 时序分三类参数, 分别是 读取时序,时钟到DS (data strobe) 关系,DS 到 Data 的关系

读取时序

| 参数 | 功能 |

|---|---|

| CL (CAS Latency) | CAS 是 Column-Address-Strobe,即当列地址出现在行上时。CL 是内部 READ 命令与输出数据第一位之间的延迟(以时钟周期为单位)。 |

| AL (Additive Latency) | 使用 AL,设备允许在 ACTIVATE 命令之后立即发出 READ 命令 |

| RL (Read Latency) | 总体读取延迟 |

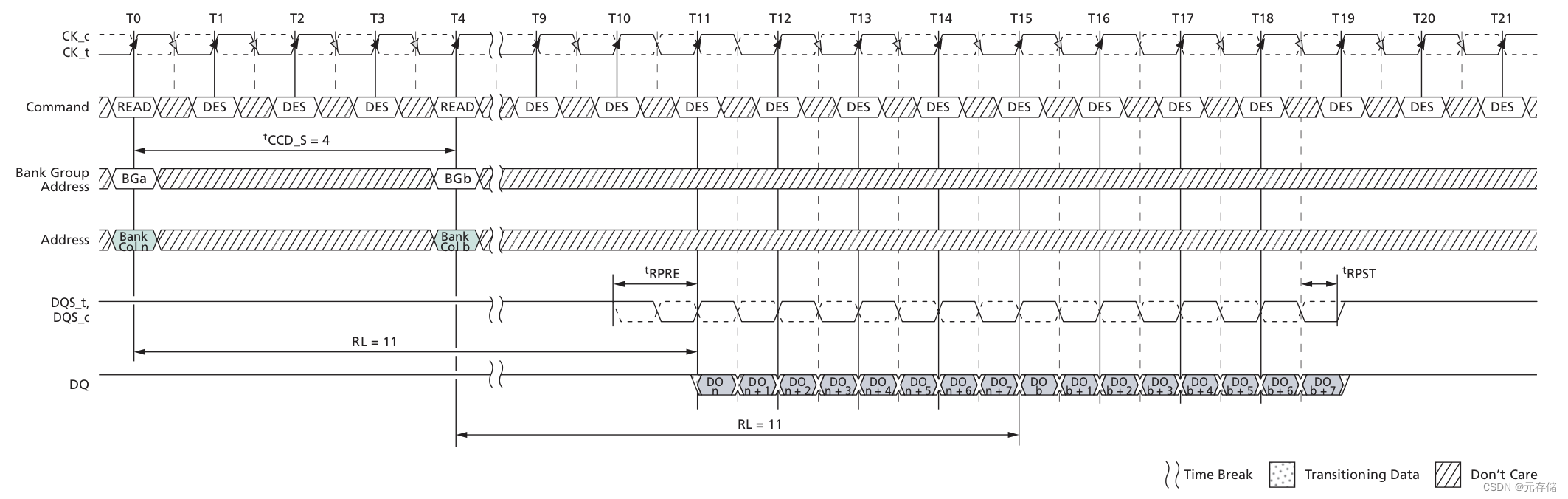

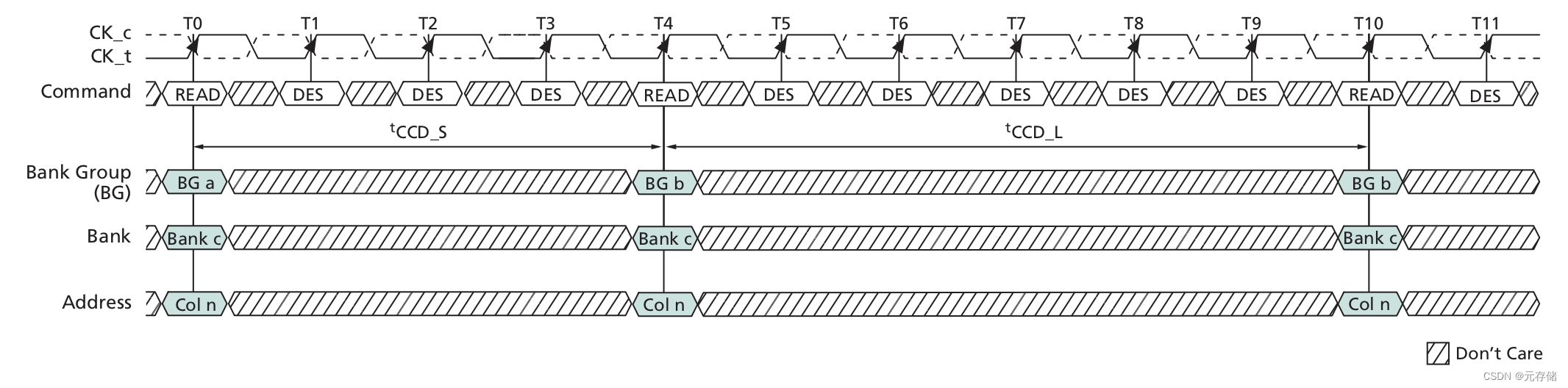

| tCCD_S & tCCD_L | 与Bank访问同一Bank组内的银行相比,访问不同bank group 之间的时间延迟更少。对不同bank group 的访问命令需要间隔的tCCD_S(短时间)延迟,而同一bank group 内的访问命令要间隔tCCD_L(长时间)延迟。 |

图:对不同Bank Group的连续读取。(来源:美光数据表)

图:tCCD_S 和 tCCD_L 的图示(来源:美光数据表)

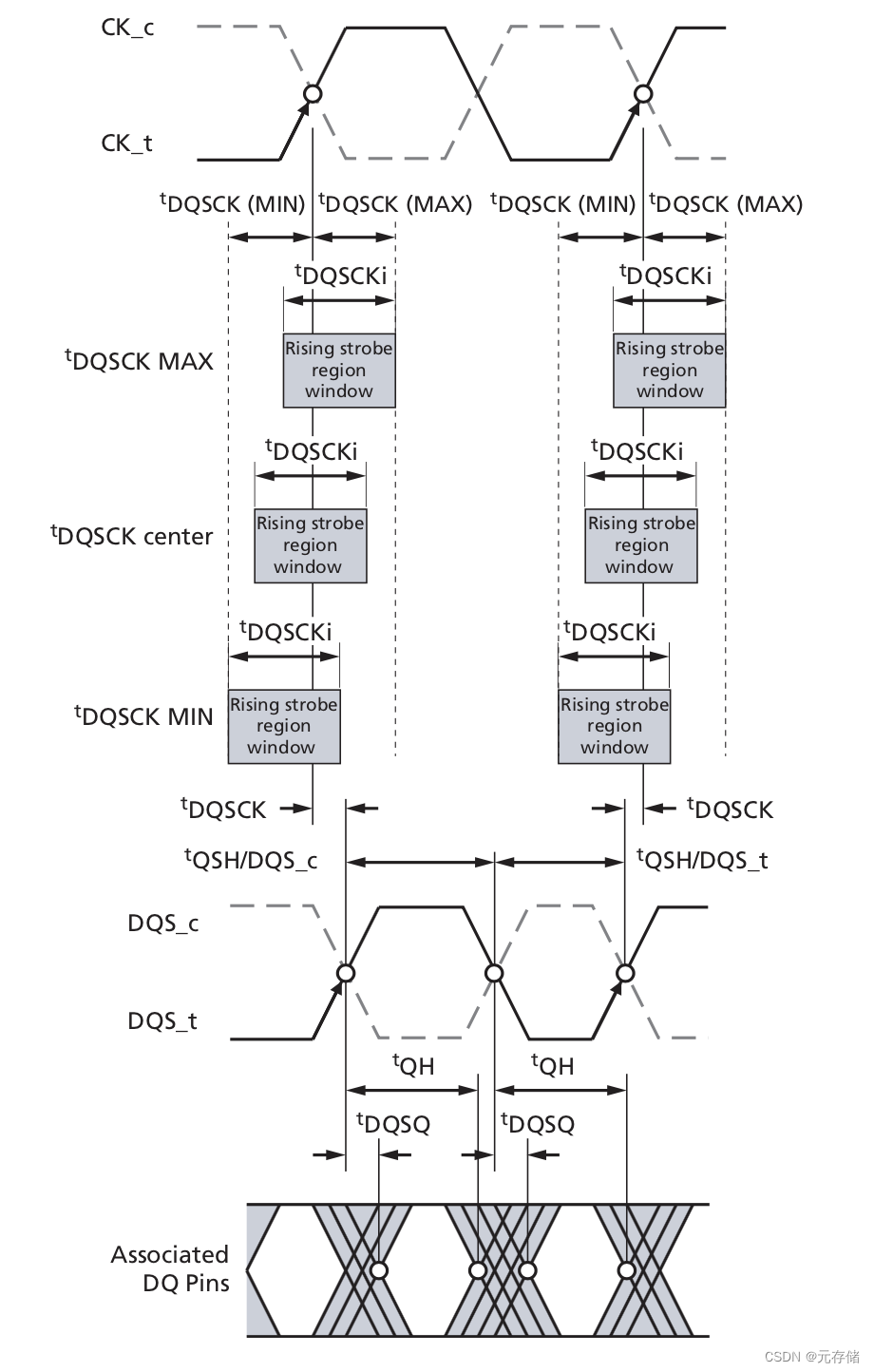

| tDQSCK (MIN/MAX) | 描述数据选通边沿相对于时钟CK_t的允许范围 |

| tDQSCK | 是上升频闪边沿相对于CK_t的实际位置 |

| tQSH | 描述数据选通高脉冲宽度 |

| tQSL | 数据选通低脉冲宽度。 |

图:CK-DQS 和 DQS-DQ 关系图示(来源:美光数据表)

参考

| 1 | https://www.systemverilog.io/design/ddr4-basics/#read |

免责声明:

一. 本博客及动态出现的信息,均仅供参考。本人将尽力以求所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性。本人对有关资料所引致的错误、不确或遗漏,概不负任何法律责任(包括侵权责任、合同责任和其它责任)。

二. 任何透过本博客及动态的网页或链接及得到的资讯、产品及服务,本人概不负责,亦不负任何法律责任。

三. 本博客及动态使用的信息,网页或链接(图片)可能由于本人疏忽未标明作者和出处,如有侵权,请立即与本人取得联系。

四. 本博客及动态支持保护知识产权,任何单位或个人认为本博客及动态中的网页或链接内容可能涉嫌侵犯其知识产权,应该及时向本人提出,并提供侵权情况证明。本人会依法尽快删除相关内容或断开相关链接。

五. 本博客内容仅供学习交流,禁止商用。

六. 阅读并使用本博客及动态包括其提供的网页链接及资源时,即代表您已阅读并同意本免责声明的全部内容。如有异议,请立刻关闭本网页并屏蔽本人动态并停止使用。

这篇关于[DDR5 Jedec] 读操作 Read Command 精讲的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!