clocking专题

【FPGA】clocking wizard配置(PLL/MMC内核配置)

明天准备更vivado的iserdes内核,ISE可能不怎么更了,由于毕设要开始搞了,准备直接转vivado,其实都差不多。今天先把ISE的始终管理内核说一下吧。 第一页,clocking features选项框中的 1.Frequency synthesis选项是允许输出与输入时钟不同频率的时钟。 2.Spread Spectrum选项是提供调制时钟输出,用来降低电子设备产生

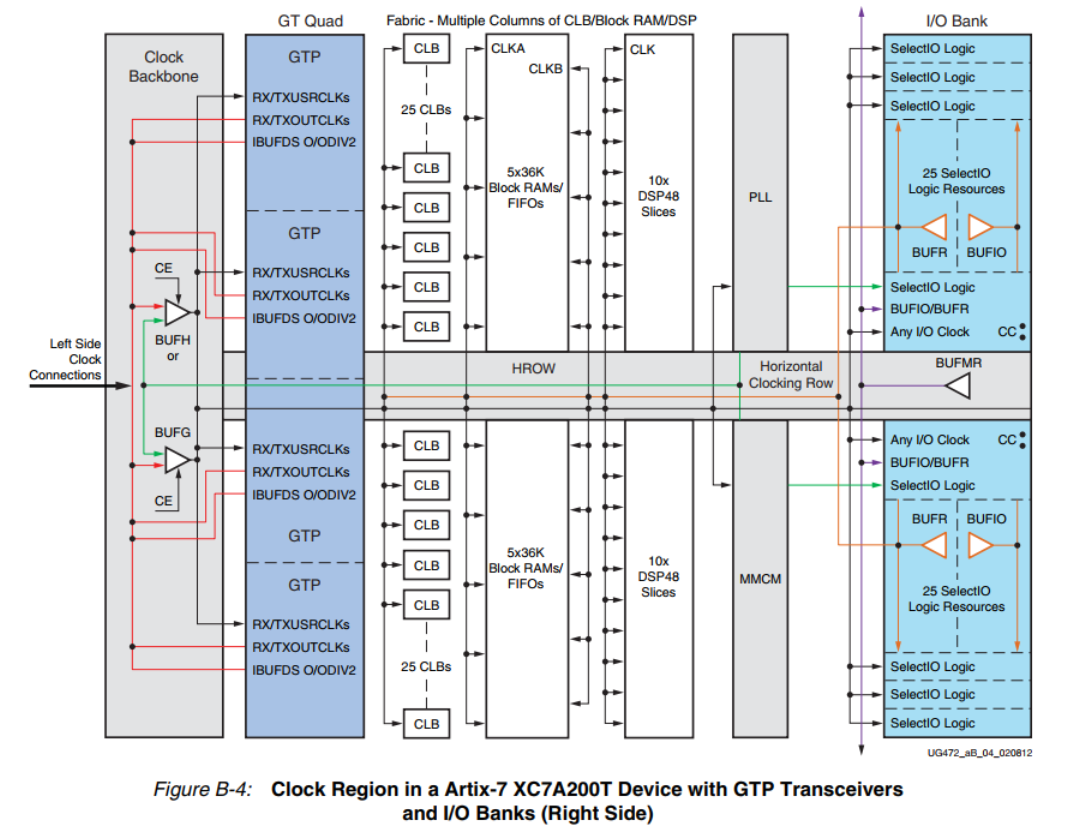

FPGA - 7系列 FPGA内部结构之Clocking -04- 多区域时钟

前言 本文节选UG472进行整理翻译,用于介绍时钟资源的跨多个时钟区域的时域说明和注意要点。 文章目录 前言简介跨多个区域的时钟BUFMR 原语 使用示例跨时钟区域的时钟对齐每个时钟区域的单个缓冲器驱动多个BUFIO驱动多个 BUFR 每个时钟区域的多个缓冲器驱动多个 BUFR(带分频)和 BUFIO驱动多个 BUFR(有和没有分频) BUFR 对齐 每个时钟区域的时钟资源和连接变化re

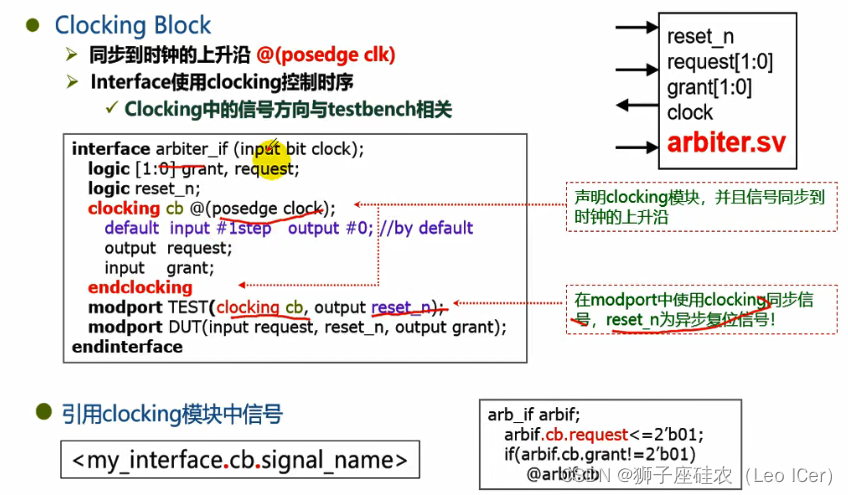

验证systemVerilog中激励的时序(clocking)

1 背景介绍 1.1 保留足够的setup time 下图中在10ns时,没有建立(setup)时间,很容引起不确定情况发生,因此需要将write信号前移,留出足够长的setup time。 1.2 保留足够的hold time 下图中,正确情况: TB产生req信号,req信号拉高,DUT的grant信号拉高;当grant信号经过一个周期后,grant信号会被拉低,然后req信号也会