本文主要是介绍验证systemVerilog中激励的时序(clocking),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1 背景介绍

1.1 保留足够的setup time

下图中在10ns时,没有建立(setup)时间,很容引起不确定情况发生,因此需要将write信号前移,留出足够长的setup time。

1.2 保留足够的hold time

下图中,正确情况:

- TB产生req信号,req信号拉高,DUT的grant信号拉高;

- 当grant信号经过一个周期后,grant信号会被拉低,然后req信号也会拉低;

- 若是hold time时间不够,req采到的grant为高电平(错误),那么req信号也无法拉低,出现错误。

1.3 总结

驱动过晚或采样过早,都会引起竞争现象。在建立之前,稳定的驱动信号,可以避免竞争现象。

2 clocking 模块控制同步信号

clocking模块控制同步信号,要点:

- clocking是关键字

- systemVerilog中使用clocking模块控制同步信号

- 在interface中定义clocking模块,将信号同步到某一个特定的时钟

- clocking模块中所有信号都是同步驱动或采样,可以确保验证平台可以在正确的时间跟设计进行交互

- clocking 模块主要使用在验证平台中,不能用作RTL设计

- 一个interface中可以包含多个clocking模块

2.1 用interface和clocking进行仿真

- 从DUV的输出到testbench的输入有1个延迟

- 需要在testbench的输入端加一个“虚拟的同步器”

- 从testbench的输出到DUV的输入没有延迟

default input #1 step output #0;(默认值,不写的话就是这个值,放置在clocking block)

2.2 定义input 和output skew,控制时序

- input skew表示在时钟有效边沿采样信号的扭斜单位时间 output skew表示

- 在时钟有效边沿驱动信号的扭斜单位时间

clocking dram @(clk)input #1ps address;input #5output #6 data;

endclocking

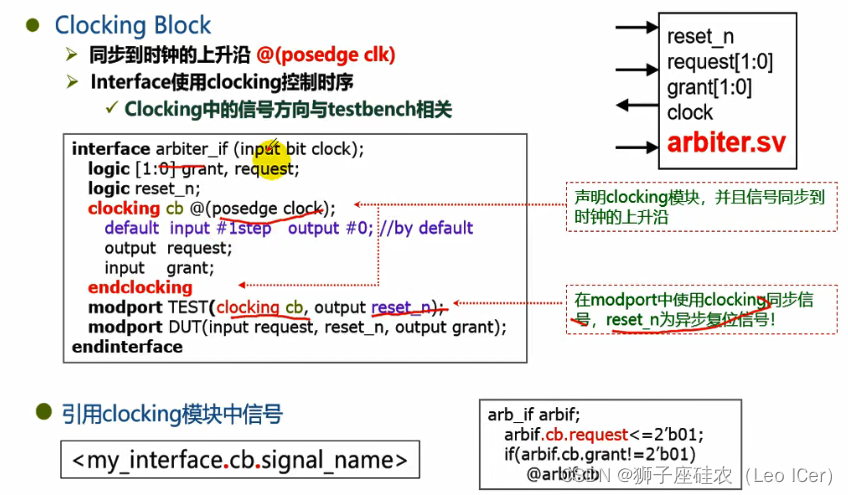

2.3 clocking block举例和引用clocking模块中信号

自动将arbif.cb.request信号同步到clock上面。

自动将arbif.cb.request信号同步到clock上面。

2.4 将信号同步到时钟有效边沿

@arbif.cb; //等待接口arbif的时钟边沿

repeat (3) @arbif.cb; //经过3个arbif接口的时钟上升沿

2.5 同步到信号的任何一个边沿

@arbif.grant; //等待接口grant信号的任意一个边沿

@(posedge arbif.cb.grant); //等待grant信号的上升沿

@(negedge arbif.cb.grant); //等待grant信号的下降沿

wait (arbif.cb.grant==1) //等待grant信号为高电平,如果已经为高电平则没有延迟

2.5 等待n个时钟周期 ##n 阻塞语句

##2 arbif.cb.requeset <= 0;//经过2个时钟周期后赋值

等效:repeat(2) @arbif.cb;

2.6 引用clocking内的信号

驱动信号必须用非阻塞赋值,采样信号用阻塞赋值

arbif.cb.request <=1; //驱动输出信号

value = arbif.cb.grant; //采样出入信号

2.7 在下一个有效时钟边沿赋值

如果不使用时间的推进语句如#1或者##1,仿真时间不会更新,会导致仿真悬挂

forever beginif(request ==1)grant <= 1;end

上面将会是死循环,直至内存写满,应该改成如下代码解决问题

forever begin

#1 psif(request ==1)grant <= 1;end

这篇关于验证systemVerilog中激励的时序(clocking)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!