本文主要是介绍DE2-115串口通信,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

- 一、 内容概要

- 二、 Hello Nios-II

- 2.1 Nios-II编程

- 2.1.1 硬件

- Ⅰ 搭建环境

- Ⅱ 编写代码

- 2.1.2 软件

- 2.1.3 烧录

- Ⅰ硬件

- Ⅱ 软件

- 2.2 verilog编程

- 三、 心得体会

一、 内容概要

- 分别用Verilog和Nios软件编程, 实现DE2-115开发板串口输出“Hello Nios-II”字符到笔记本电脑串口助手。

二、 Hello Nios-II

2.1 Nios-II编程

2.1.1 硬件

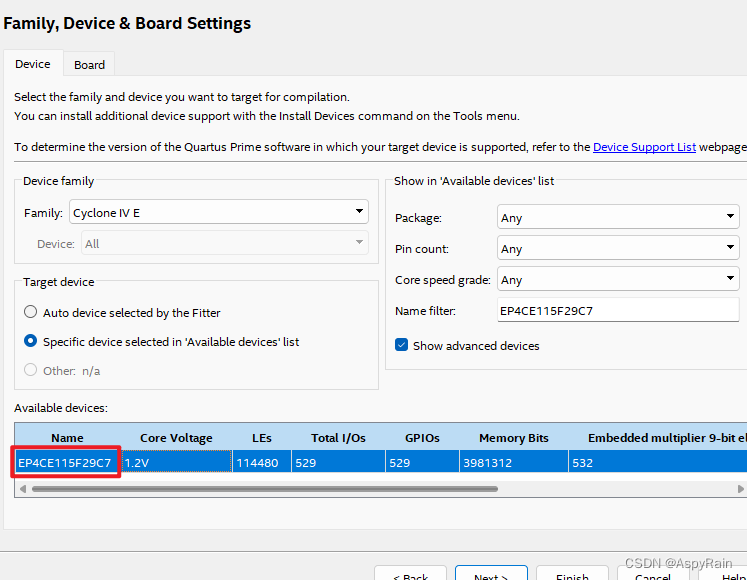

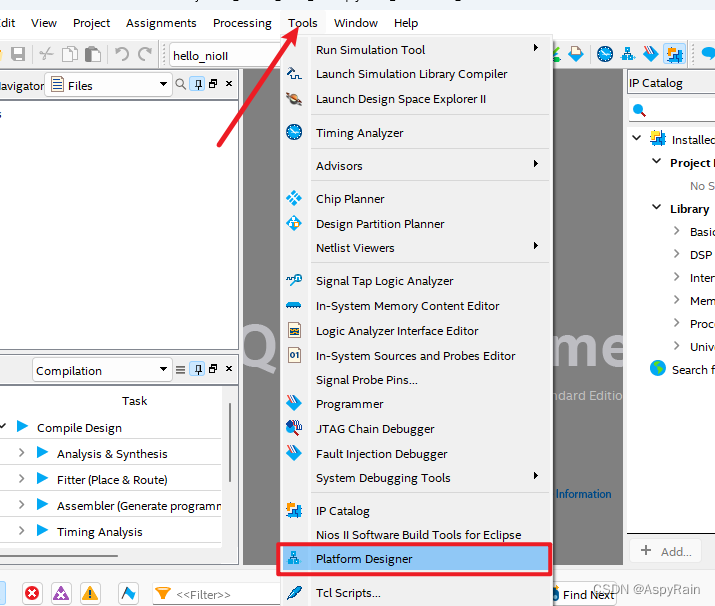

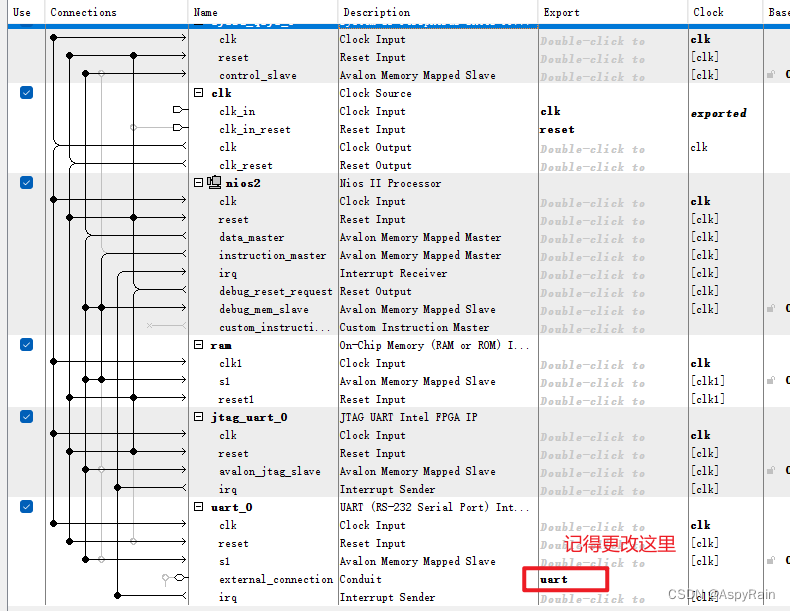

Ⅰ 搭建环境

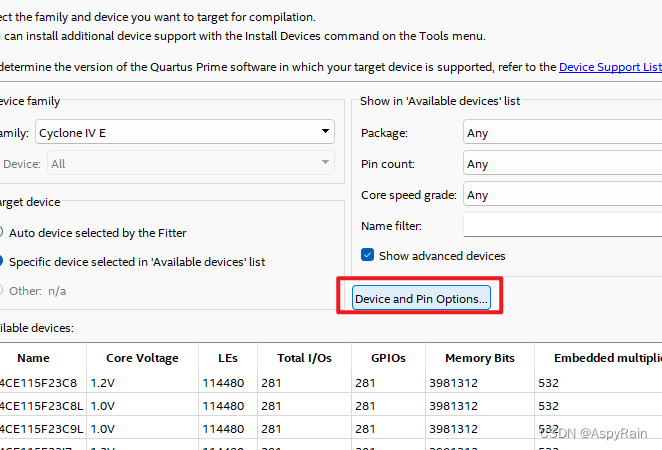

新建工程,选择开发板

进行模块添加和连接

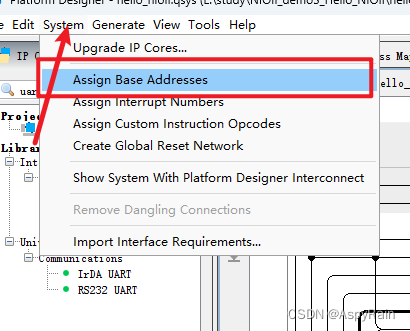

分配地址

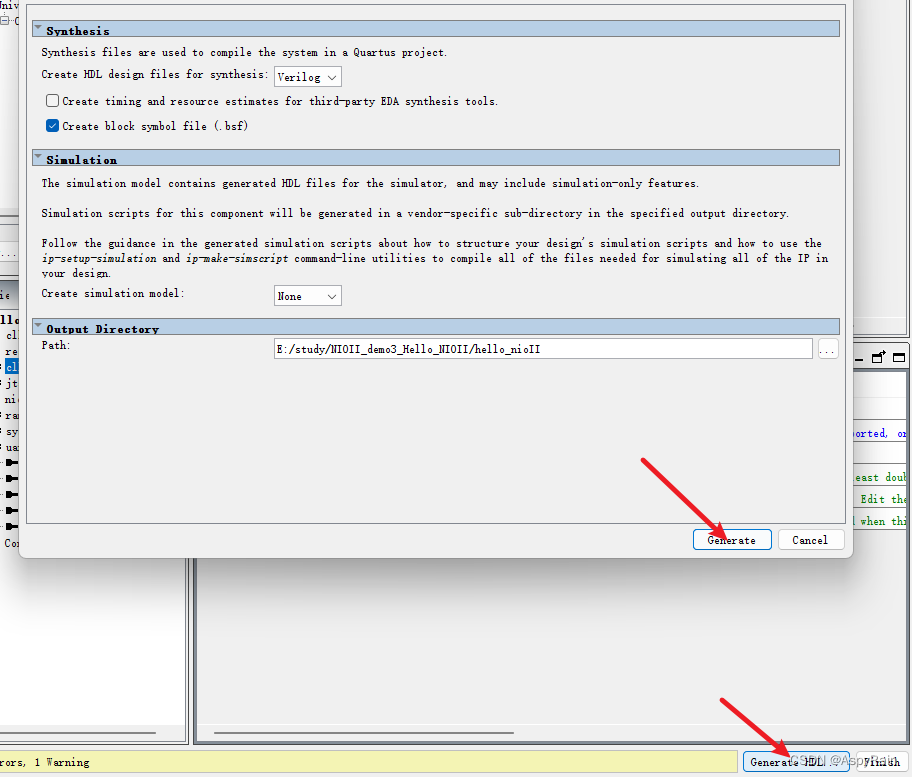

Generate

Ⅱ 编写代码

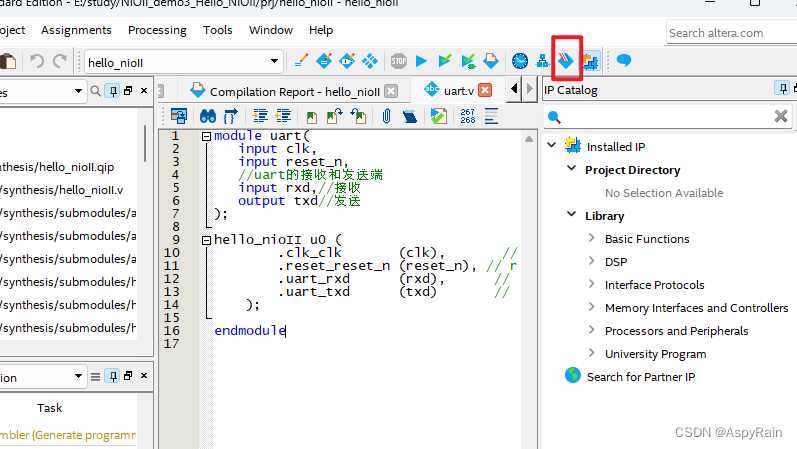

新建Verilog文件

module uart(input clk,input reset_n,//uart的接收和发送端input rxd,//接收output txd//发送

);

endmodule

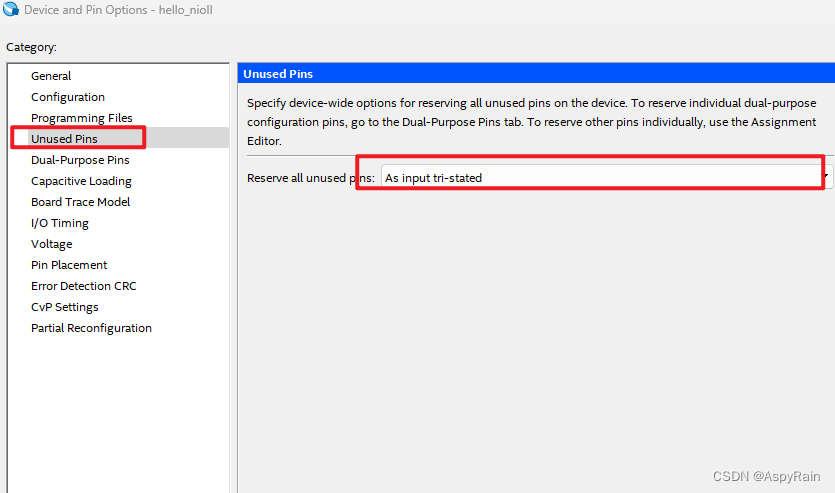

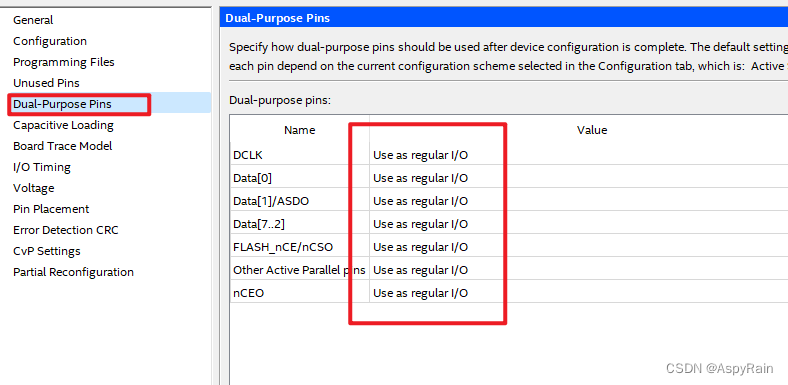

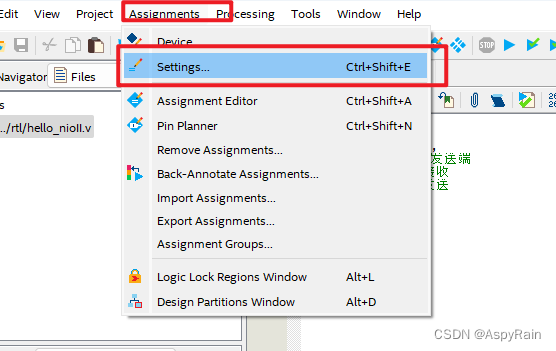

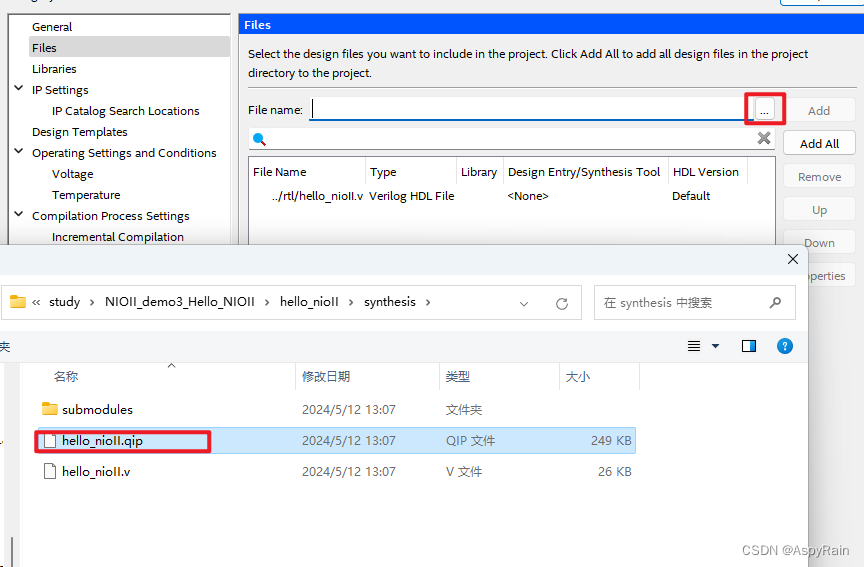

配置

进入qip文件的第一个verilog文件

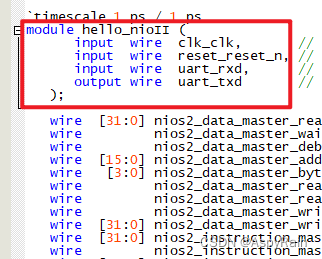

根据模块信息,在顶层文件里增加:

hello_nioII u0 (.clk_clk (clk), // clk.clk.reset_reset_n (reset_n), // reset.reset_n.uart_rxd (rxd), // uart.rxd.uart_txd (txd) // .txd);

完整代码为:

module uart(input clk,input reset_n,//uart的接收和发送端input rxd,//接收output txd//发送

);hello_nioII u0 (.clk_clk (clk), // clk.clk.reset_reset_n (reset_n), // reset.reset_n.uart_rxd (rxd), // uart.rxd.uart_txd (txd) // .txd);endmodule编译

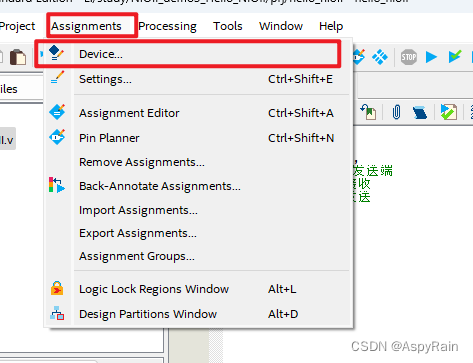

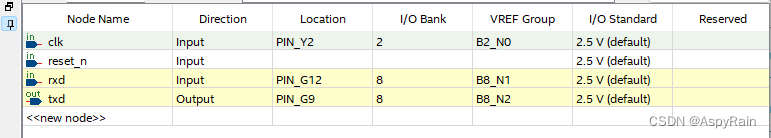

配置管脚

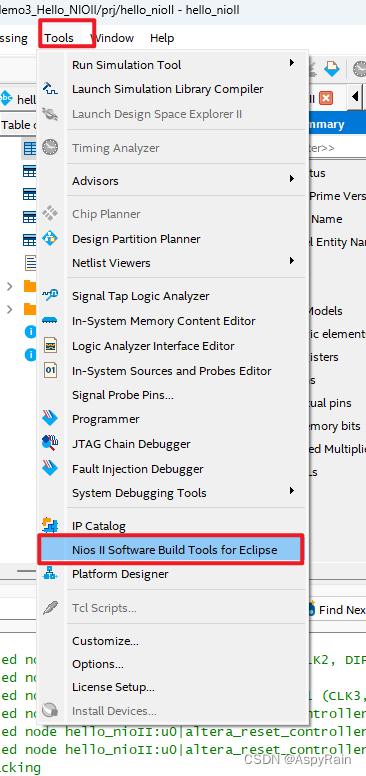

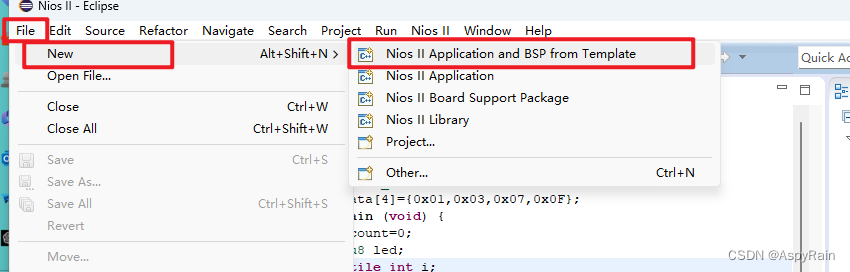

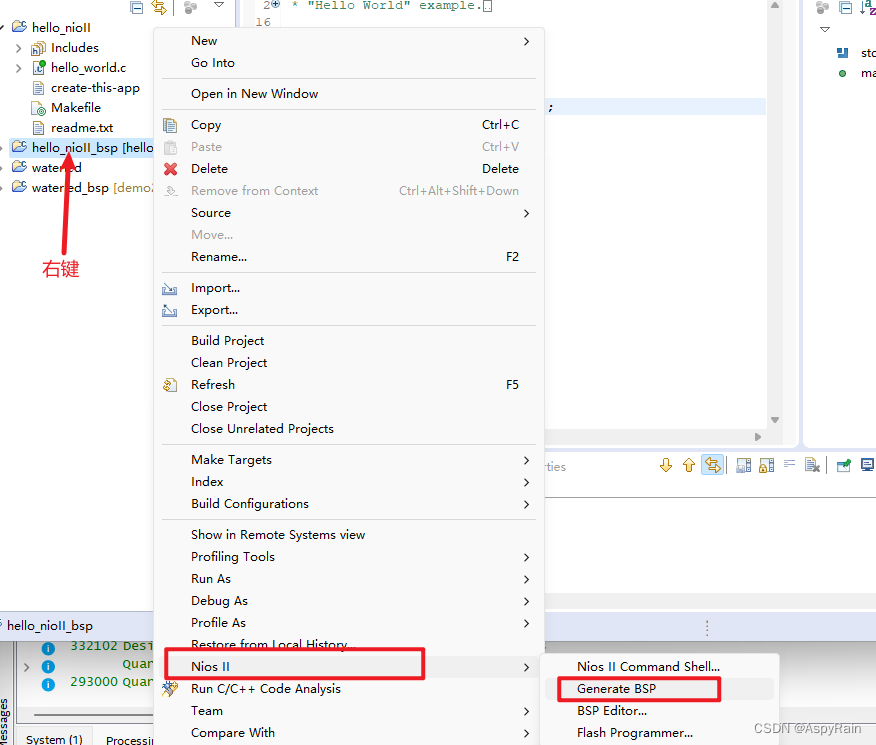

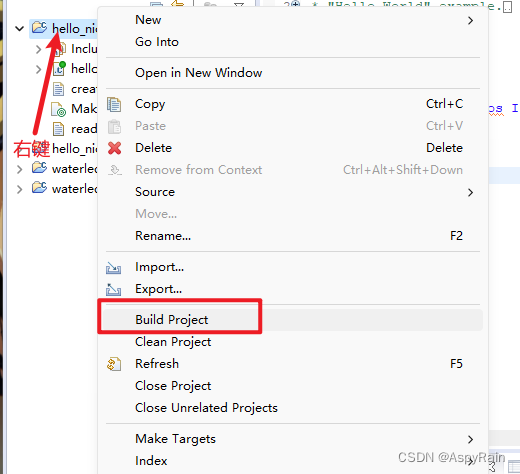

2.1.2 软件

修改hello_world.c

#include <stdio.h>

#include "unistd.h"

#include "system.h"

#include "alt_types.h"

#include "altera_avalon_uart_regs.h"

#include "sys\alt_irq.h"alt_u8 txdata=0;

alt_u8 rxdata=0;//UART中断服务函数

void IRQ_UART_Interrupts(){rxdata = IORD_ALTERA_AVALON_UART_RXDATA(UART_BASE);//将rxdata寄存器中存储的值读入变量rxdata中txdata = rxdata;//串口自收发,将变量rxdata的值赋给txdatawhile(!(IORD_ALTERA_AVALON_UART_STATUS(UART_BASE)& ALTERA_AVALON_UART_STATUS_TRDY_MSK));//查询发送准备接收信号,如果没有准备好,则等待IOWR_ALTERA_AVALON_UART_TXDATA(UART_BASE,txdata);//发送准备好,发送txdata

}//中断初始化函数

void IRQ_init()

{//清除状态寄存器IOWR_ALTERA_AVALON_UART_STATUS(UART_BASE, 0);//使能接收准备中断,给控制寄存器相应位写1IORD_ALTERA_AVALON_UART_CONTROL(UART_BASE);alt_ic_isr_register(UART_IRQ_INTERRUPT_CONTROLLER_ID,//注册ISRUART_IRQ,//中断控制器标号,从system.h复制IRQ_UART_Interrupts,//UART中断服务函数0x0,//指向与设备驱动实例相关的数据结构体0x0);//flags,保留未用

}int main()

{/*while(1){IOWR_ALTERA_AVALON_UART_TXDATA(UART_BASE, "hello world!\n");int i=0;while(i<5000){i++;}}*/IRQ_init();while(1);return 0;

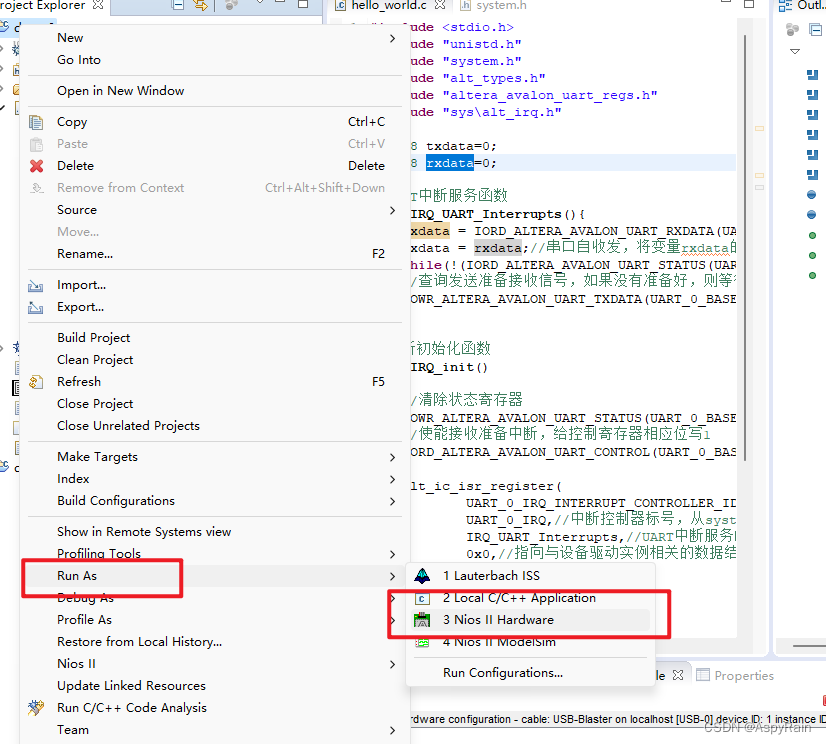

}配置

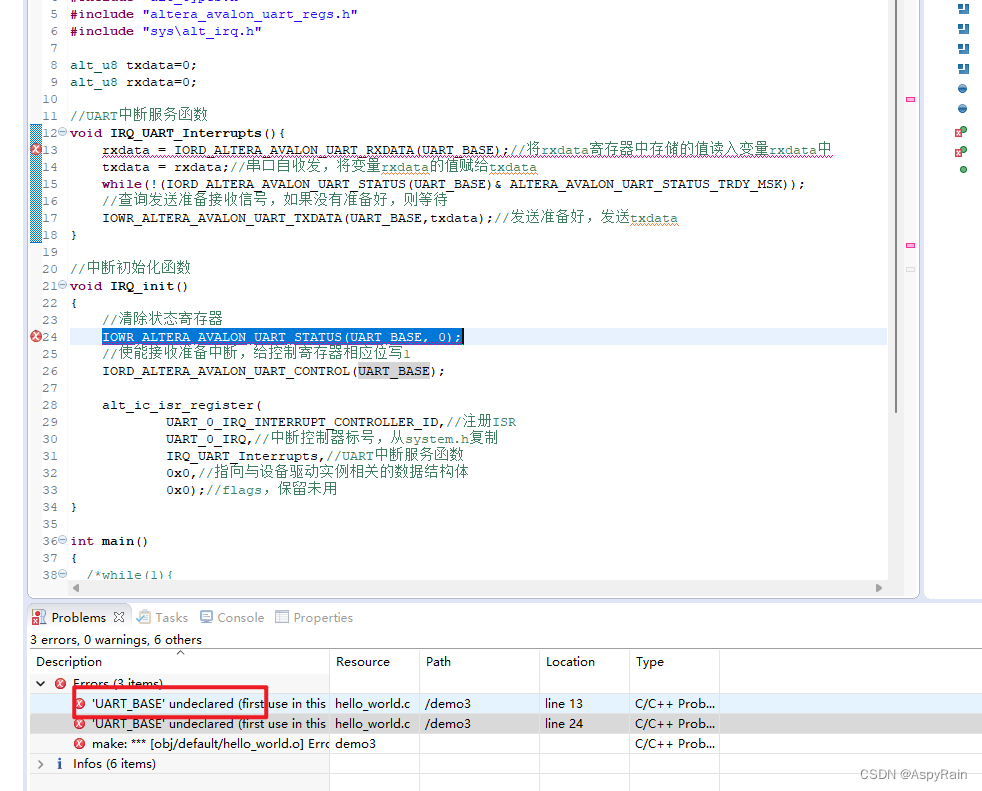

报错:

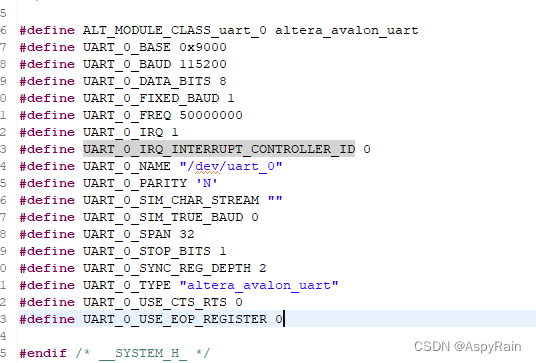

若遇到类似情况,请按住ctrl然后左键单击#include 里面的system.h,找到UART部分

发现是URAT_0_BASE,把helloworld.c里面的UART_BASE修改为URAT_0_BASE就行

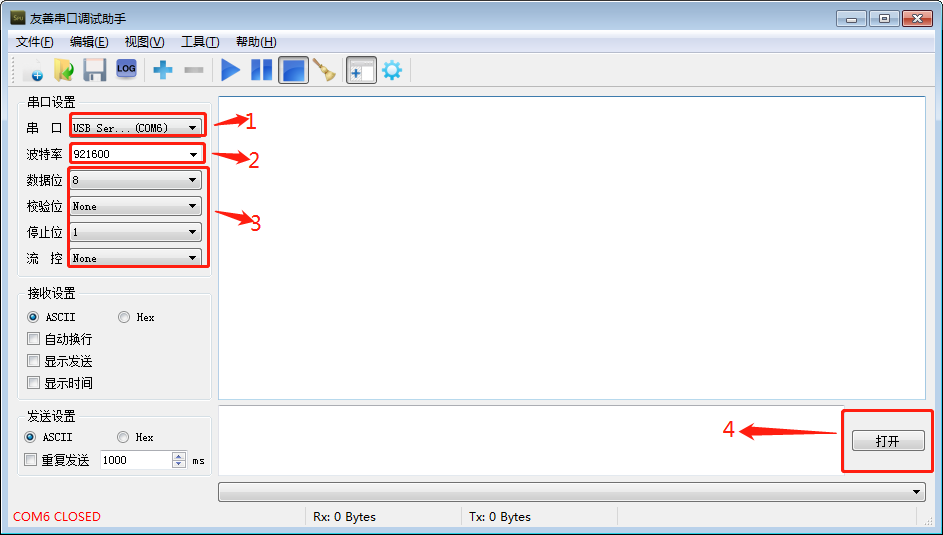

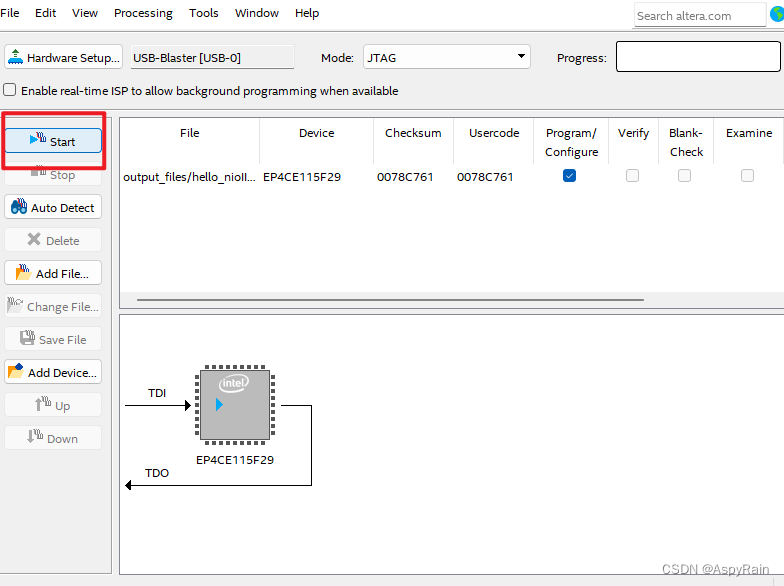

2.1.3 烧录

Ⅰ硬件

Ⅱ 软件

2.2 verilog编程

编译烧录以下代码就行

`timescale 1ns/1nsmodule rs232

(input wire sys_clk , //系统时钟50MHzinput wire sys_rst_n , //全局复位input wire rx , //串口接收数据output wire tx //串口发送数据

);//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//parameter define

parameter UART_BPS = 20'd9600 , //比特率CLK_FREQ = 26'd50_000_000 ; //时钟频率localparam BAUD_CNT_MAX = CLK_FREQ/UART_BPS ;

//wire define

wire en_h_flag;

wire [7:0] po_data; //接收的数据

wire po_flag; //接收完1字节数据标志位,高电平有效

wire flag; //识别到接收数据与密码对应标志位

wire tx_flag; //发送完1字节数据标志位,高电平有效

reg [39:0] datain_reg; //存储接收的数据,5字节

reg [47:0] dataout_reg;//存储的要发送的数据,6字节

reg [1:0] state; //状态位

reg [7:0] data_tx; //发送的1字节数据

reg en_tx; //发送允许标志位

reg [2:0] tx_cnt; //发送字节计数器,发送6个后置0

reg en; //发送控制开关

reg [12:0] baud_cnt; //收到发送成功的tx_flag后延迟1个波特

reg bit_flag; //计满1baud有效

reg work; //波特计数器baud_cnt有效

//********************************************************************//

//*************************** Instantiation **************************//

//********************************************************************//

//------------------------ uart_rx_inst ------------------------

uart_rx

#(.UART_BPS (UART_BPS ), //串口波特率.CLK_FREQ (CLK_FREQ ) //时钟频率

)

uart_rx_inst

(.sys_clk (sys_clk ), //input sys_clk.sys_rst_n (sys_rst_n ), //input sys_rst_n.rx (rx ), //input rx.po_data (po_data ), //output [7:0] po_data.po_flag (po_flag ) //output po_flag

);

always@(posedge sys_clk or negedge sys_rst_n)if(!sys_rst_n)en <= 1'b1;else if(en_h_flag)en <= 1'b1;else if(tx_cnt>=3'd5)en <= 1'b0;

//接收数据寄存

always@(posedge sys_clk or negedge sys_rst_n)if(!sys_rst_n)datain_reg <= 40'd0;else if(po_flag)datain_reg <= {datain_reg[31:0],po_data[7:0]};//接收到tx_flag后,延迟一个baud时间再发送下一个

always@(posedge sys_clk or negedge sys_rst_n)if(!sys_rst_n)work <= 1'b0;else if(tx_flag)work <= 1'b1;else if(state != 2'd2)work <= 1'b0;always@(posedge sys_clk or negedge sys_rst_n)if(!sys_rst_n)baud_cnt <= 13'd0;else if((baud_cnt == BAUD_CNT_MAX - 1) || en_tx)baud_cnt <= 13'b0;else if(work)baud_cnt <= baud_cnt + 1'd1;always@(posedge sys_clk or negedge sys_rst_n)if(!sys_rst_n)bit_flag <= 1'b0;else if(baud_cnt == BAUD_CNT_MAX - 1)bit_flag <= 1'b1;else if(state != 2'd2) bit_flag <= 1'b0;//hello的ASCII码

assign flag = (datain_reg == 40'h68656c6c6f)? 1'b1:1'b0;always@(posedge sys_clk or negedge sys_rst_n)if(!sys_rst_n)beginstate <= 2'd0;dataout_reg <= 48'h6e692c68616f;//ni,hao的ASCII码data_tx <= 8'd0;en_tx <= 1'b0;tx_cnt <= 3'd0;endelsecase(state)2'd0:beginif(flag && en)state <= 2'd1;elsestate <= 2'd0;end2'd1://发送数据beginstate <= 2'd2;data_tx <= dataout_reg[47:40];en_tx <= 1'b1;dataout_reg <= dataout_reg << 8;end 2'd2://等待数据发送完成,并计数+1beginif(bit_flag)beginif(tx_cnt>=3'd5)beginstate <= 2'd0;tx_cnt <= 3'd0; endelse beginstate <= 2'd1;tx_cnt <= tx_cnt + 1'd1; end endelsebeginen_tx <= 1'b0;state <= 2'd2;endend default : state <= 2'd0;endcase

//------------------------ uart_tx_inst ------------------------

uart_tx

#(.UART_BPS (UART_BPS ), //串口波特率.CLK_FREQ (CLK_FREQ ) //时钟频率

)

uart_tx_inst

(.sys_clk (sys_clk ), .sys_rst_n (sys_rst_n ), .pi_data (data_tx ), .pi_flag (en_tx ), .tx (tx ), .tx_flag (tx_flag )

);endmodule三、 心得体会

通过本次实验,我更深刻地理解了Nios II软件编程和Verilog硬件编程在FPGA设计中的应用和区别。Nios II软核提供了一个通用的处理器环境,可以使用高级语言如C/C++进行编程,易于理解且开发效率较高。而Verilog则是一种硬件描述语言,它允许我直接控制硬件行为,更适合于对性能要求较高的应用。

硬件环境的搭建与配置

在Nios II编程部分,我学会了如何使用Quartus软件和Platform Designer(或Qsys)来搭建硬件环境,包括选择适当的开发板、添加必要的硬件模块(如Nios II处理器、存储器、UART等),并进行模块间的连接和参数配置。这个过程对理解整个系统的硬件架构非常有帮助。

软件编程与硬件的交互

在软件编程部分,我学习了如何在Nios II软核上编写C语言程序,并通过HAL库函数来控制硬件设备,如UART进行串口通信。同时,我也意识到了软件编程中对硬件地址和中断控制器标识符的正确引用的重要性。

遇到的问题及解决

在实验过程中,我遇到了几个问题,包括硬件地址未定义、中断控制器标识符未声明等。通过查阅文档、检查硬件设置和代码,我学会了如何定位并解决这些问题。这些经验对于我未来解决类似的问题非常宝贵。

Verilog编程实践

在Verilog编程部分,我编写了一个简单的UART收发模块,并实现了基本的串口通信功能。这个过程加深了我对UART工作原理和Verilog语言的理解。

总体来说,这次实验不仅增强了我的动手实践能力,也加深了我对FPGA设计、Nios II软核开发以及跨平台串口通信等知识的理解。通过解决实际遇到的问题,我获得了宝贵的学习和成长经验。未来,我希望能将这些知识和技能应用到更复杂的项目中,以进一步提升我的专业技能。

这篇关于DE2-115串口通信的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!