本文主要是介绍【verilog-语法】编译命令( compiler directives ),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、前言

编译器指令的范围是从它的出现的点延伸到处理的所有文件,直到另一个编译器指令取代它或处理结束。编所有的编译命令都有重音符 " ` "引出。在IEEE std1364-2005中共介绍了19条编译命令,这19条命令又可分为12组命令进行独立或组合使用。本文将对这些编译命令进行介绍。

二、编译命令

2.1 `resetall

使用格式:`resetall

当编译过程中遇到`resetall编译器指令时,所有编译器指令都会设置为默认值。 `resetall指令对于确保只有编译特定源文件所需的指令处于活动状态非常有用。

建议的用法是将 `resetall 放在每个源文本文件的开头,紧接着是源文件中所需的编译指令。

在模块或 UDP 声明中指定 `resetall 指令是非法的。

2.2 `default_nettype

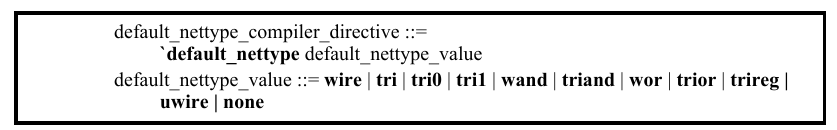

指令`default_nettype控制为隐式网络声明创建的网络类型。 它只能在模块定义之外使用。 允许使用多个`default_nettype指令,代码中按照最新的`default_nettype指令执行。 当不存在`default_nettype指令或者有指定`esetall指令时,隐式网络的类型为“wire”。 当`default_nettype设置为“none”时,所有网络都应显式声明。 如果未显式声明网络,则会生成错误。`default_nettype的语法如下:

2.3 `unconnected_drive , `nounconnected_drive

使用格式:

`unconnected_drive pull1/pull0......

`nounconnected_drive 出现在指令`unconnected_drive和`unconnected_drive之间的模块的所有未连接输入端口

被上拉或下拉,而不是正常的默认值。 当指定pull1时,所有未连接的输入端口会上拉到1。 当指定pull0时,未连接的输入端口被下拉为0。

使用要点:

- 建议将每个`unconnected_drive与`nounconnected_drive配对,但这不是必需的。

- 最新出现的该指令指令控制未连接端口发生的情况。

- 这些指令应在模块声明之外成对指定。

- `resetall 指令包括 `nounconnected_drive 指令的效果。

2.4 `include

使用格式:`include "filename"

文件包含(`include)编译器指令用于在编译期间将源文件的全部内容插入到另一个文件中。

`include 编译器相关要点:

- 编译器指令 `include 可以在 Verilog HDL 描述中的任何位置指定。

- 文件名是要包含在源文件中的文件的名称; 文件名可以是完整路径名或相对路径名。

- 使用`include 编译器指令包含在源代码中的文件可以包含其他`include 编译器指令, 包含文件的嵌套层数应是有限的,最少可以嵌套15层。

- 只有空格或注释可以出现在与 `include 编译器指令相同的行上,不能出现其他内容。

- 可用于包含全局或常用的定义和任务,而无需将重复代码封装在模块边界内。

2.5 `define ,`undef

使用格式:`define 标识符(宏名) 字符串(宏内容)

作用很简单,就是为了在编译预处理时,把程序中在该命令之后的所有宏名替换成宏内容。可以通过这种方式将一个很长的字符串用很短的宏名替代,或者用有意义的宏名去代替一个没有意义的数字或符号。通过修改宏定义中的宏内容可以实现大规模修改,更加简洁。

`define相关要点:

- `define可以写在模块外和模块内,有效范围为定义之后到原文件结束。通常将其定义在module外, 作为程序的一部分,在此程序内都有效。

- 在引用已定义的宏名时,必须在宏名的前面加上符号`,表示该名字是一个经过宏定义的名字。

- 宏定义是用宏名代替字符串,也就是做简单的置换,不做语法检查。只有在编译已经被宏展开后的源程序时才报错。

- 宏定义不是verilog HDL语句,不必在行末加分号,加分号则分号也被当成宏内容字符串进行替换。

- 宏定义可以嵌套,定义一个新的宏定义时可以引用之前定义过的宏定义进行嵌套。

- 宏名和宏内容必须在同一行进行声明,宏内容中如果有注释行,注释行不会被替换。

- 所有编译器指令均被视为预定义的宏名称; 将编译器指令重新定义为宏名称是非法的。

`undef:用于取消之前声明过的宏定义。

宏定义功能不受编译器指令`resetall的影响。

2.6 `ifdef,`else, `elsif, `endif, `ifndef

使用格式:

(`define FLAG1/2/3)

`ifdef/`ifndef FLAG1// Statements

`elsif FLAG2// Statements

`elsif FLAG3// Statements

`else// Statements

`endif与`define进行联用,按逻辑编译对应条件内的内容。

条件编译语句相关要点:

- 可以出现在源文件中的任意地方。

- 条件编译语句的条件中必须为`define定义的标识符。

2.7 `timescale

使用格式:`timescale 时间单位/时间精度

该指令指定了跟随其后的模块的时间单位和时间精度,有效值和单位为1,10,100以及s,ms,us,ns,ps,fs 。

`timescale相关要点:

- `timescale 编译器指令指定时间和延迟值的测量单位以及遵循该指令的所有模块中延迟的准确度,直到另一个 `timescale 编译器指令被读取。

- 如果没有指定“时间刻度”或者已通过“resetall”指令重置,则时间单位和精度是由模拟器决定。

- 如果某些模块指定了“时间刻度”而其他模块则没有,则将出现错误。

2.8 `celldefine 与 `endcelldefine

指令 `celldefine 和 `endcelldefine 标记模块为单元模块。 某些 PLI 例程将单元用于应用程序,例如延迟计算。 建议将每个`celldefine 与一个`endcelldefine 配对,但这不是必需的。 源代码中最新出现的任一指令控制模块是否被标记为单元模块。 这些对中的多个可能出现在单个源描述中。这些指令可能出现在源描述中的任何位置,但建议在模块定义之外指定这些指令。 `resetall 指令包括 `endcelldefine 指令的效果。

2.9 `line

待学习。

2.10 `pragma

带学习。

2.11 `begin_keywords, `end_keywords

待学习。

三、参考资料

IEEE std1364-2005.

这篇关于【verilog-语法】编译命令( compiler directives )的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!