本文主要是介绍vivado Aurora 8B/10B IP核(9)- CRC、 Aurora 8B/10B内核的时钟接口端口,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

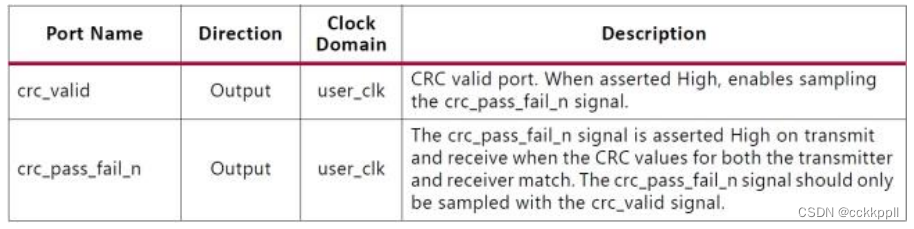

CRC 模块提供 16 位或 32 位 CRC,用于用户数据。

Aurora 8B/10B 内核的时钟接口端口

从相邻收发器四边形的时钟Xilinx 实现工具可以根据需要对南北路由和引脚交换到收发器时钟输入进行必要的调整,以将时钟从一个四线到另一个。

重要信息:共享参考时钟时必须遵守以下规则,以确保满足高速设计的抖动余量:

•7 系列 FPGA 中由外部时钟引脚对(mgtrefclkn / mgtrefclkp)采集的 GTP 或 GTH 收发器四分之一 的总数不能超过三个四分之一(一个四分之一和一个四分之一)或 12 个 GTPE2_CHANNEL /

GTHE2_CHANNEL 收发器。7 系列 FPGA 中超过 12 个收发器或超过 3 个四极的设计应使用多个外部时钟引脚。

•UltraScale 架构 FPGA 中由外部时钟引脚对(mgtrefclkn / mgtrefclkp)采集的收发器四分之一的

总数不得超过五个四分位数(下面两个四分之一和两个四分之一)或 20 个 GTHE3_CHANNEL 收发器。

这篇关于vivado Aurora 8B/10B IP核(9)- CRC、 Aurora 8B/10B内核的时钟接口端口的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!