本文主要是介绍时序分析之setup/hold时钟path requirement解疑,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

一、前言

二、时钟边沿选取

2.1 setup和hold

2.2 path requirement

2.3 同频率同相位

2.4 同频率不同相

2.5 倍频或分频关系

2.5 异步时钟

2.6 无公共周期

一、前言

在时序报告中,任选一条时序分析结果查看路径详细延时,会看到在source path delay和destination path delay中,最前面的一段延时都是时钟边沿的延时,有时该值和时钟周期相同,有时不一样,该值是如何选取的呢?

同时,在summary中也可以看到Requirement,改值有时如何计算的呢,下面将针对这些就行解释

二、时钟边沿选取

2.1 setup和hold

先来看看setup,在用户手册906中,setup是对两个时钟延时关系进行最悲观的边沿检查,对时钟的边沿检查默认是发起时钟和捕获时钟边沿间的最小的正delta。

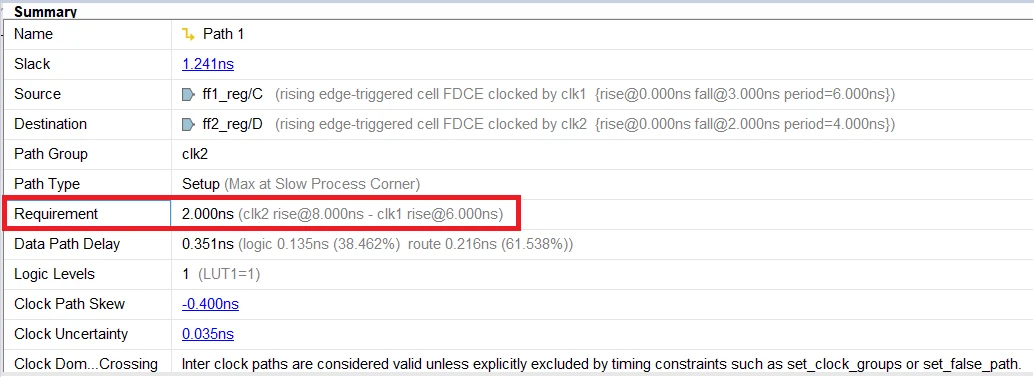

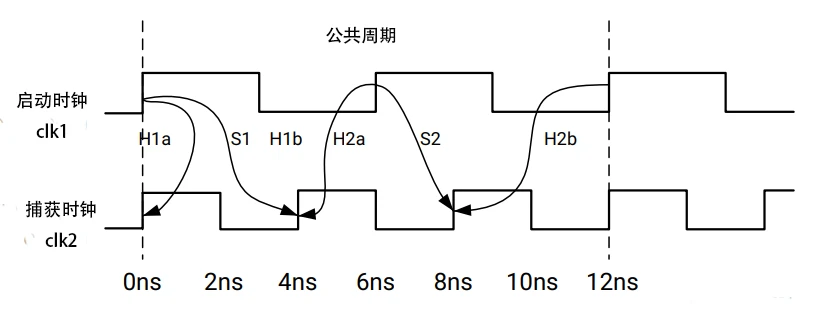

在下面的内容开始前,先解释一个概念公共周期common period,假设时钟clk1周期为T1,时钟clk2周期为T2,则满足下列关系的最小正整数m,n,m*T1=n*T2,m*T1或n*T2的值即为公共周期

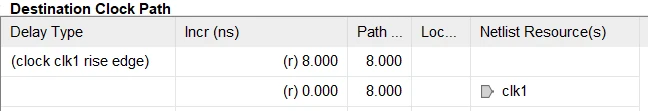

以时钟上升沿触发为例,启动时钟clk0的周期为6ns,第一个上升沿在0ns,下降沿在3ns,捕获时钟周期为4ns,第一个上升沿在0ns,下降沿在2ns。

在一个公共周期12ns内,存在两个setup检查,第一个setup(1)的delta值为4ns,第二个setup(2)的delta值为2ns,根据前面的定义选择最小的delta值,即2ns。因此时序分析时,启动时钟的边沿延时为6ns,捕获时钟为8ns

再看hold的定义,hold检查是确保启动边沿发送数据后,不能够被前一个setup捕获沿捕获,因此要比前一个捕获沿迟到,也即下图hold检查为H1a,H2a。

另一种情况是在setup启动沿的数据无法被捕获沿捕获后,数据能被下一个有效启动时钟沿发送,也即下图hold检查中的H2a,H2b。

同样的,hold分析也只分析最悲观的hold检查,根据上面的两种情况,可知最悲观的hold检查并不和最悲观的setup检查一一对应。时序分析工具会遍历公共周期内所有最悲观的setup检查对应的hold检查,选取最悲观的作为hold分析值,还是以setup分析的clk1和clk2为例,最大的hold要求时间为0ns,

hold计算

数据要求时间(hold)=捕获沿时间+目标时钟路径时延+时钟不确定度+hold值

数据到达时间(hold)=启动沿时间+源时钟路径时延+数据路径时延

slack(hold)=数据到达时间(hold)-数据要求时间(hold),因此,只由数据到达时间时延大于数据要求时间,slace值才为正值

2.2 path requirement

在前言中也提到path requirement,path requirement中的即为公共周期内捕获时钟的有效沿时间减去启动时钟的有效沿,setup分析取最小值,hold分析取最大值。

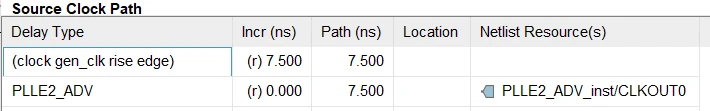

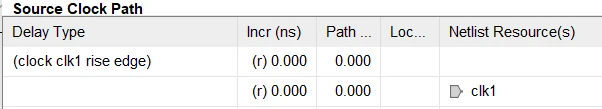

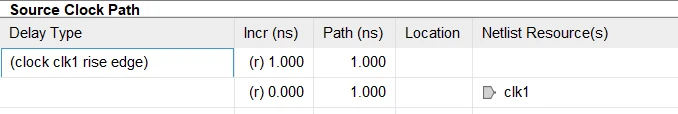

源时钟clk1的rise延时

目的时钟clk2的rise延时

2.3 同频率同相位

假设启动时钟和捕获时钟是同一个时钟clk,周期为6ns,上升沿0ns,下降沿3ns,

则根据前面的分析可知道

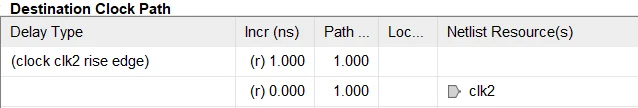

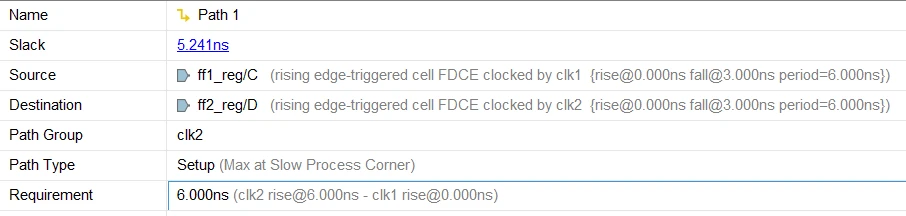

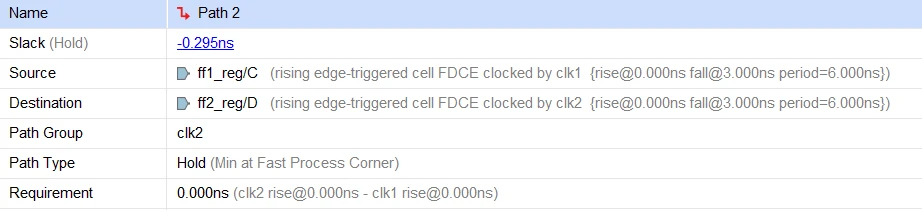

Source和Destination中显示了clk1和clk2的波形信息,setup中Requirement为6ns,即启动沿边沿时延为0ns,捕获沿延时为6ns

hold分析中,因clk1和clk2的边沿是对齐的,故requirement为0

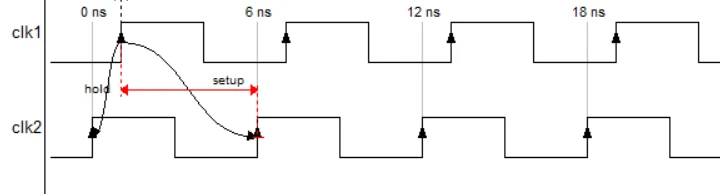

2.4 同频率不同相

场景1

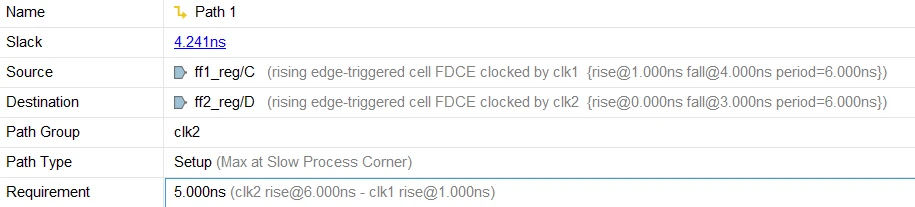

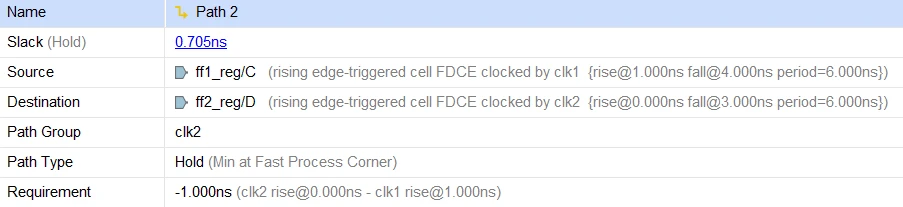

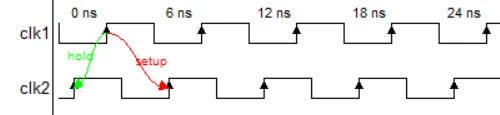

假设启动时钟clk1和捕获时钟clk2都是周期为6ns,但上升沿时间clk1在1ns,clk2在0ns,占空比都为50%,此时公共周期仍为6ns。

报告结果如下,setup的requirement为5ns

此时clk1的上升沿rise为1ns,即符合预期

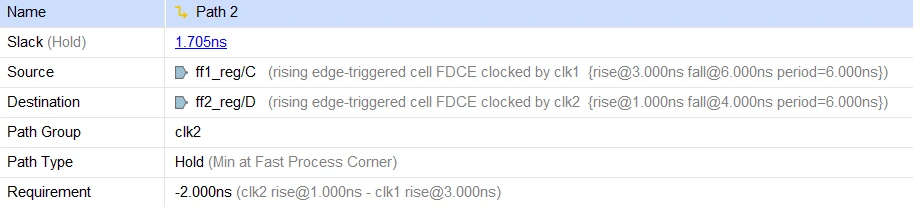

hold的requirement因上升沿非同一时刻,clk1右移了1ns,因此,Rise(clk2)-Rise(clk1)=-1ns

场景2

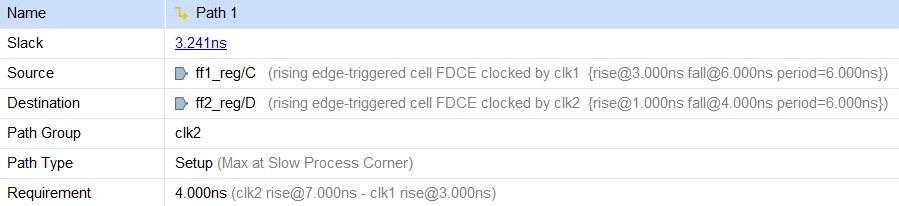

考虑在一个周期内,clk2的上升沿来的比clk1,如clk1的上升沿在3ns处,clk2的上升沿在1ns处,setup、hold分析如下图,可知此时红色setup的两个边沿已跨越了一个周期时间,绿色为hold的检查边沿

setup中requirement为4ns

hold中requirement的值为Rise(clk2)-Rise(clk1)=1ns-3ns=-2ns

2.5 倍频或分频关系

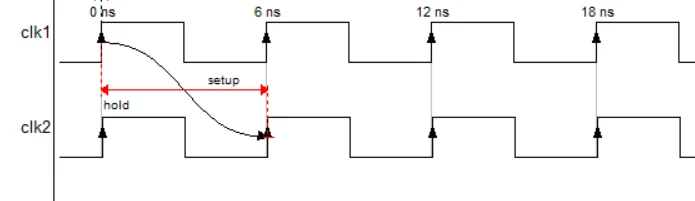

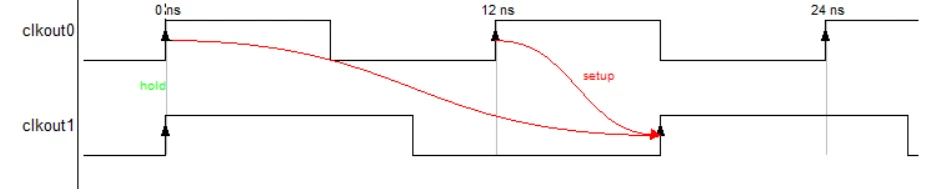

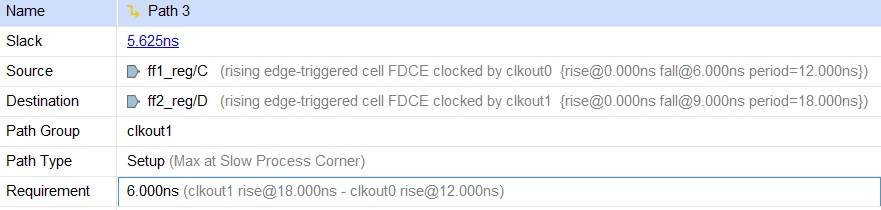

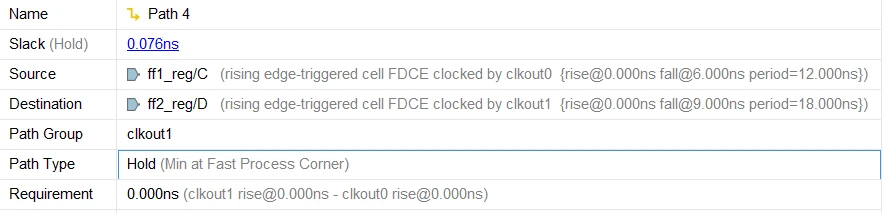

如由PLL输出的两个clkout0和clkout1分别是参考时钟clk1(周期为6ns的参考时钟)的2分频和2分频时钟,此时clkout0和clkout1仍为同步时钟,周期分别为12ns,18ns,因为相位关系是确定的。此时setup边沿有两条,根据最小值原则,应该要选取红色短线那条。

setup分析中requirement的值为12ns。

hold分析中因为上升沿对齐,仍为0

2.5 异步时钟

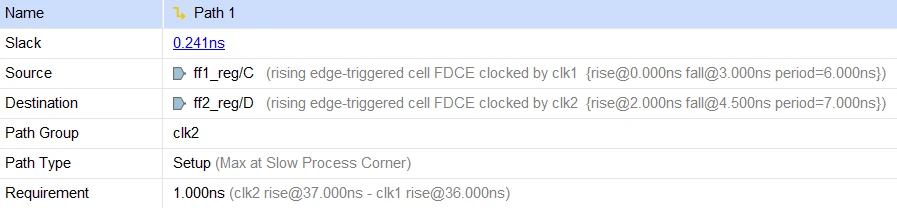

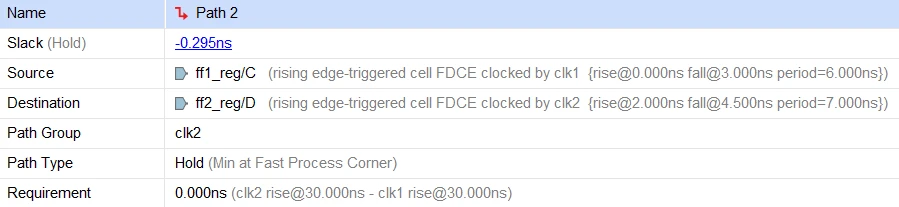

clk1周期为6ns,上升沿在0ns处,clk2周期为7ns,上升沿在2ns处,此时根据前面寻找公共周期的公式m*T1=n*T2,可知周期时长为42ns,两个时钟上升沿之差最小在clk1的36ns,clk2的37ns处,因此,setup下的requirement为1ns

hold的值类似,在30ns处二者的上升沿对齐,因为requirement为0

2.6 无公共周期

在上述的时钟clk1,clk2在一个数量的周期内都能找到公共周期,当两个时钟在1000个周期内仍找不到公共周期,则称为不可扩展时钟(unexpandable),即无公共周期,这种情况需要确认路径是否合理,是否需要设置为异步路径,如下图中一个周期为1994ns,一个为1995ns,在1000个周期内无公共周期。

假设时钟clkout0和clkout1都有PLL的clkin1(周期为4ns)生成的,

module add(clk1,clk2,d,rst,clkin1,clkin2,sel,out );

input clk1,clk2,d,rst,clkin1,clkin2,sel;

output out;

reg ff1,ff2;

wire ff_c;PLLE2_ADV #(.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64).CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).// CLKIN_PERIOD: Input clock period in nS to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN1_PERIOD(0.0),.CLKIN2_PERIOD(0.0),// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for CLKOUT (1-128).CLKOUT0_DIVIDE(1),.CLKOUT1_DIVIDE(2),.CLKOUT2_DIVIDE(4),.CLKOUT3_DIVIDE(5),.CLKOUT4_DIVIDE(1),.CLKOUT5_DIVIDE(1),// CLKOUT0_DUTY_CYCLE - CLKOUT5_DUTY_CYCLE: Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT0_DUTY_CYCLE(0.4),.CLKOUT1_DUTY_CYCLE(0.5),.CLKOUT2_DUTY_CYCLE(0.5),.CLKOUT3_DUTY_CYCLE(0.5),.CLKOUT4_DUTY_CYCLE(0.5),.CLKOUT5_DUTY_CYCLE(0.5),// CLKOUT0_PHASE - CLKOUT5_PHASE: Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT0_PHASE(0.0),.CLKOUT1_PHASE(0.0),.CLKOUT2_PHASE(0.0),.CLKOUT3_PHASE(0.0),.CLKOUT4_PHASE(0.0),.CLKOUT5_PHASE(0.0),.COMPENSATION("ZHOLD"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL.DIVCLK_DIVIDE(1), // Master division value (1-56)// REF_JITTER: Reference input jitter in UI (0.000-0.999)..REF_JITTER1(0.0),.REF_JITTER2(0.0),.STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE"))PLLE2_ADV_inst (// Clock Outputs: 1-bit (each) output: User configurable clock outputs.CLKOUT0(clkout0), // 1-bit output: CLKOUT0.CLKOUT1(clkout1), // 1-bit output: CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2// Feedback Clocks: 1-bit (each) output: Clock feedback ports.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock// Clock Inputs: 1-bit (each) input: Clock inputs.CLKIN1(clkin1), // 1-bit input: Primary clock.CLKIN2(clkin2), // 1-bit input: Secondary clock// Control Ports: 1-bit (each) input: PLL control ports.CLKINSEL(sel), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.RST(rst), // 1-bit input: Reset// Feedback Clocks: 1-bit (each) input: Clock feedback ports.CLKFBIN() // 1-bit input: Feedback clock);// End of PLLE2_ADV_inst instantiationalways@(posedge clkout0,negedge rst)if(!rst)ff1<=1'b0;else beginff1<=d;end

assign ff_c=ff1;always@(posedge clkout1,negedge rst)if(!rst)ff2<=5'b0;else beginff2<=ff_c+1'b1;end

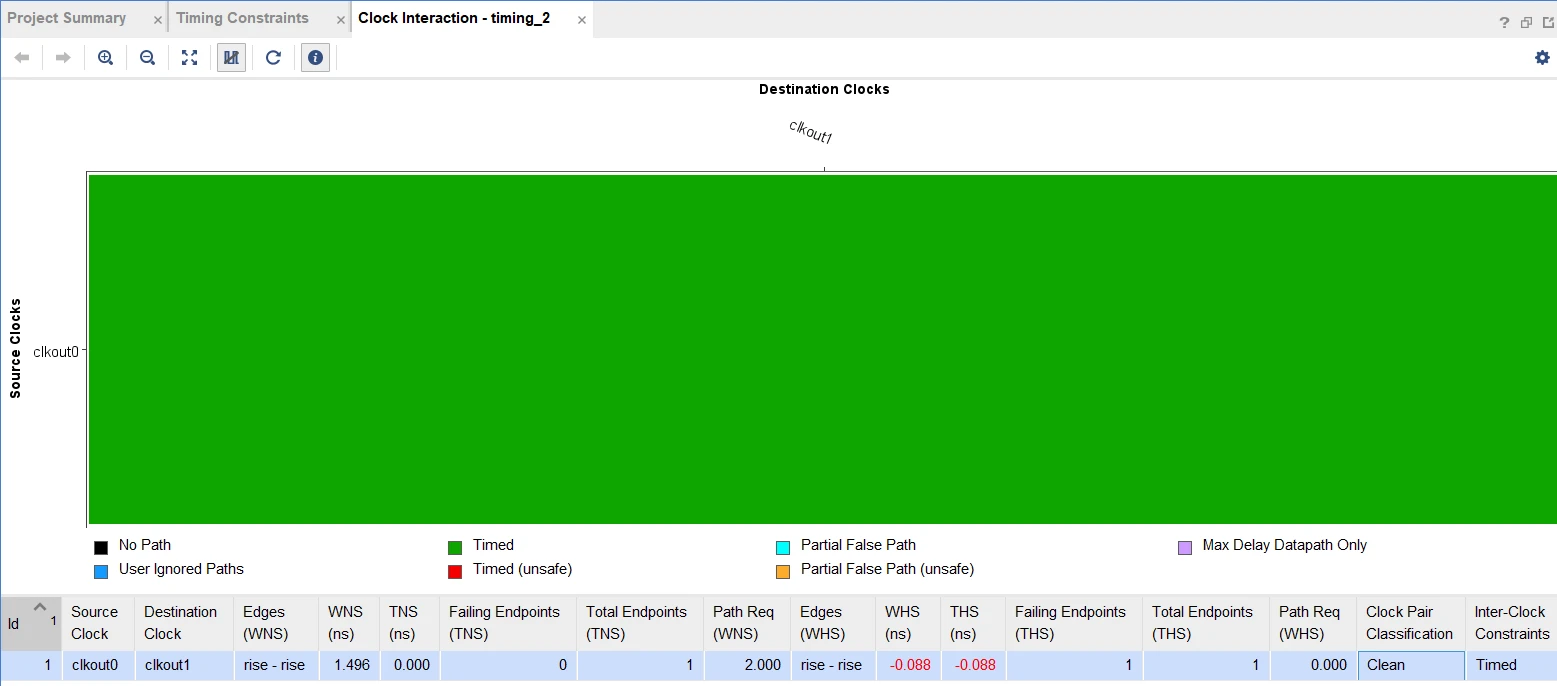

assign out=ff2;endmodule约束情况1,clkout0周期为4ns,clkout1周期为6ns,存在公共周期

create_clock -period 4.000 -name clkin1 -waveform {0.000 2.000} [list [get_ports clk1] [get_ports clkin1]]

create_generated_clock -name clkout0 -source [get_ports clkin1] -edges {1 2 3} -edge_shift {0.000 0.000 0.000} -add -master_clock clkin1 [get_pins PLLE2_ADV_inst/CLKOUT0]

create_generated_clock -name clkout1 -source [get_ports clkin1] -edges {1 2 3} -edge_shift {0.000 0.000 2.000} -add -master_clock clkin1 [get_pins PLLE2_ADV_inst/CLKOUT1]查看clock interaction可知关系为timed即属于同步时钟

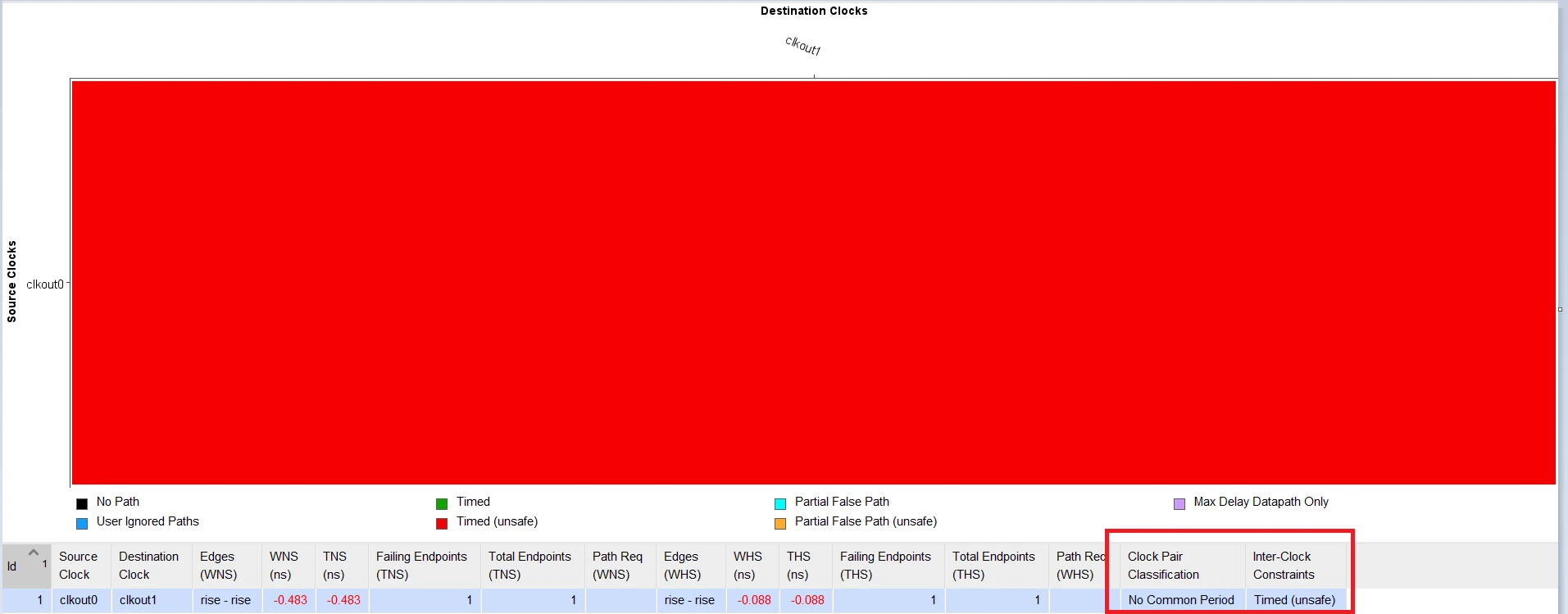

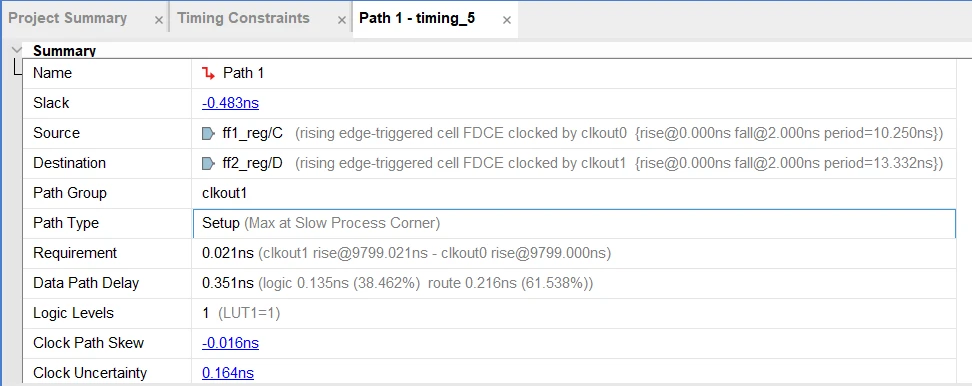

约束情况2,对应的周期clkout0和clkout1分别为10.250ns,13.332ns,此时在1000个周期内无公共周期

create_clock -period 4.000 -name clkin1 -waveform {0.000 2.000} [list [get_ports clk1] [get_ports clkin1]]

create_generated_clock -name clkout0 -source [get_ports clkin1] -edges {1 2 3} -edge_shift {0.000 0.000 6.25} -add -master_clock clkin1 [get_pins PLLE2_ADV_inst/CLKOUT0]

create_generated_clock -name clkout1 -source [get_ports clkin1] -edges {1 2 3} -edge_shift {0.000 0.000 9.332} -add -master_clock clkin1 [get_pins PLLE2_ADV_inst/CLKOUT1]在右下角的clock pair classification显示关系为no common clock,时钟关系也是Timed(unsafe)

此时的时序分析结果也是不可信的

这篇关于时序分析之setup/hold时钟path requirement解疑的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!