本文主要是介绍Jitter 和相位噪声,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

近期学习PLL的时候,发现里面有诸多jitter类型,绕晕了,写个帖子记录一下学习过程。

目录

基本jitter和相噪概念

jitter

相位噪声

相位噪声和jitter之间的联系

三种常见的抖动类型及其特点

基本jitter和相噪概念

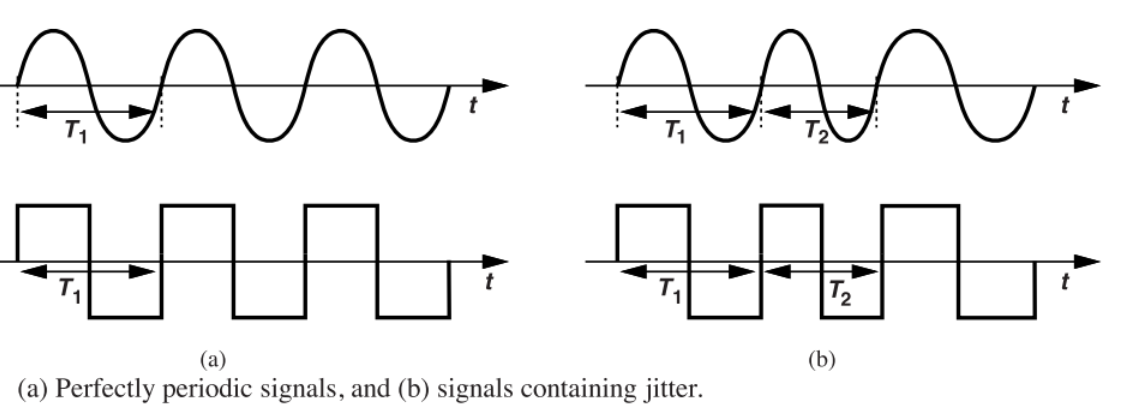

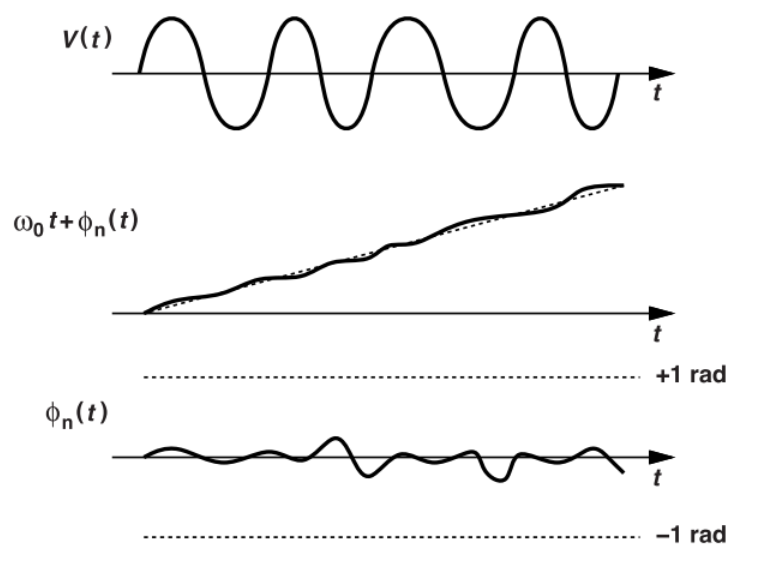

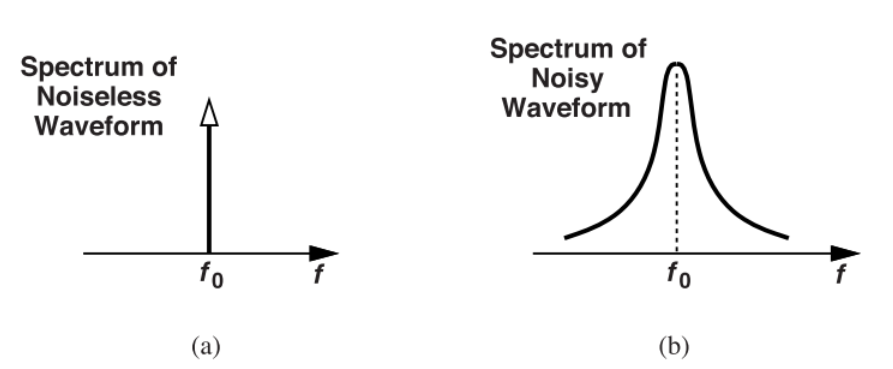

无噪声振荡器的输出是一个完全周期性的,如图a,其包含三个特点:1.周期不随时间变化2.瞬时频率不随时间变化3.在t=nT/2时均匀的发生过零点(即与横轴交点)的波形。这三个特点其实是同一个特点的三个角度描述。

实际上,VCO中的噪声源会干扰波形,对应上述三点:1.周期不相等2.瞬时频率随机变化3.在t=nT/2可能不过零点。可见,噪声随机调制频率和相位。

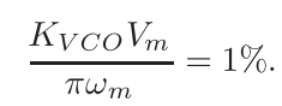

相位调制可以表示为,其中

为载波(无噪声时振荡频率),

为上述三种噪声造成的任意一种效果。如果dφn/dt= 0,则调制瞬时频率为ω0 + dφn/dt。(如果没看懂,请参考VCO 理论模型-CSDN博客)

jitter

周期性波形过零点偏离理想时间点的抖动(时域)

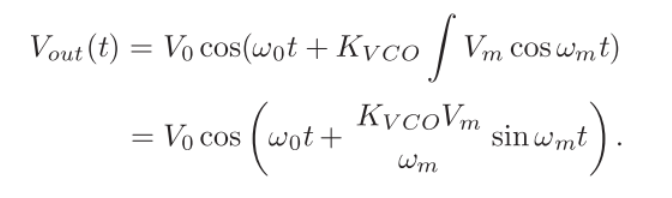

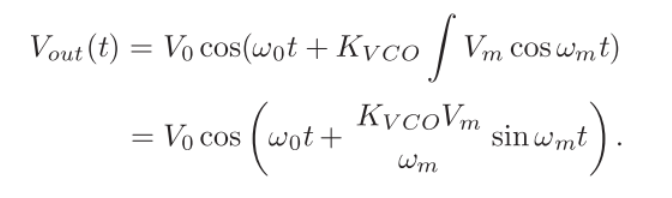

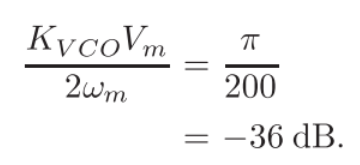

如果Vcont是一个周期性的确定扰动,则有:

相位差最大/最小时,过零点在时域上与理想点发生最大偏离(上式sin项为±1)。peak-to-peak jitter:

rad代表角频率,sec代表时域里面的秒

将时域上的peak-to-peak jitter归一化到(平均)VCO周期,即为确定性jitter(deterministic jitter):

确定性jitter:振荡器的频率周期性受到干扰。这种干扰可能来自显性控制电压,也可能来自电源或基板端子。

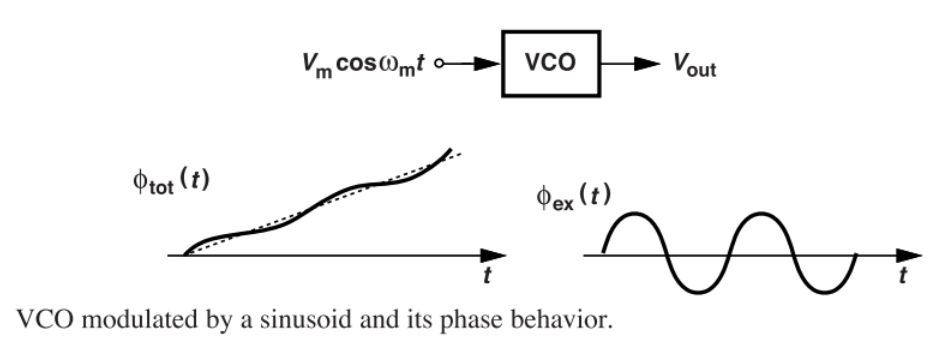

jitter在时域上的眼图如图,振荡器相位调制的时域视图不能很容易地揭示干扰是随机的还是确定的,所以求助于频域来区分不同类型的干扰。

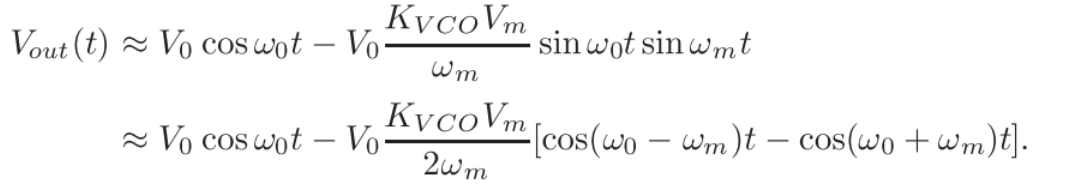

假设VCO的输入电压存在一个小扰动,即:

![]()

在VCO输出端:

经过窄带调频近似,得到:

表现在频域上即在载波附近对称分布两个旁带(杂散),对旁带幅值与载波幅值的比值感兴趣,即归一化后的旁带幅度:。随着调制频率ωm的增加,比值下降,抖动也随之下降。

可见,归一化的旁带幅度×4=peak-to-peak jitter

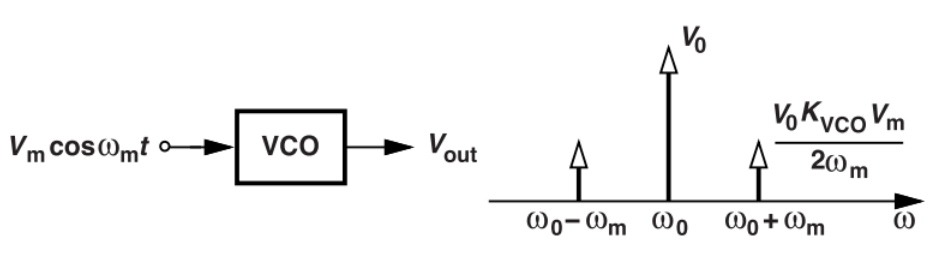

实例:如果希望振荡器产生的调频边带贡献的峰对峰抖动小于周期的1%,最大可容忍边带幅度是多少?

这是关于确定性抖动的时域和频域特性的一个有用的经验法则。

相位噪声

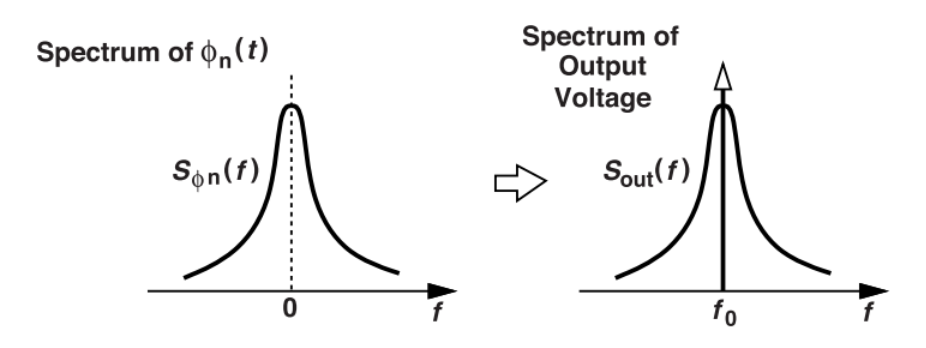

。其中,

为相位噪声。φn(t)随机调制Vout的相位和频率,频谱不再是ω = ω0处的单脉冲。也就是说,瞬时频率随机偏离ω0,将信号的一些能量溢出到脉冲附近。结果,频谱被拓宽。

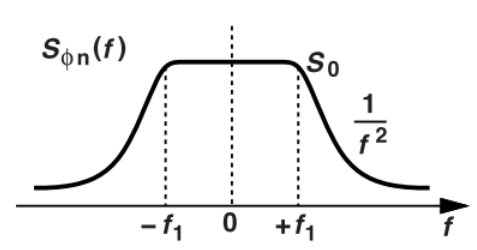

相位噪声频谱:

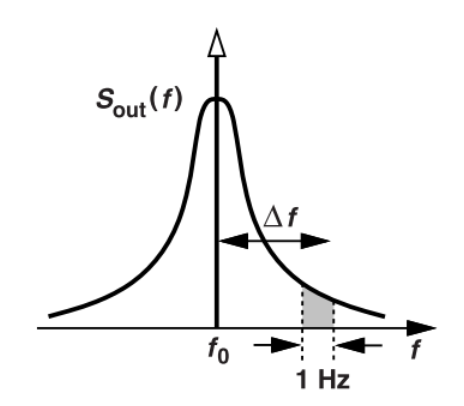

指定频偏处的相位噪声:

1、选择频偏

2.计算处1Hz带宽内的噪声功率

3.对载波功率归一化

4.取10log

结果以dBc/Hz表示,其中字母c表示归一化载波功率,每赫兹表示1hz带宽内的相位噪声功率。

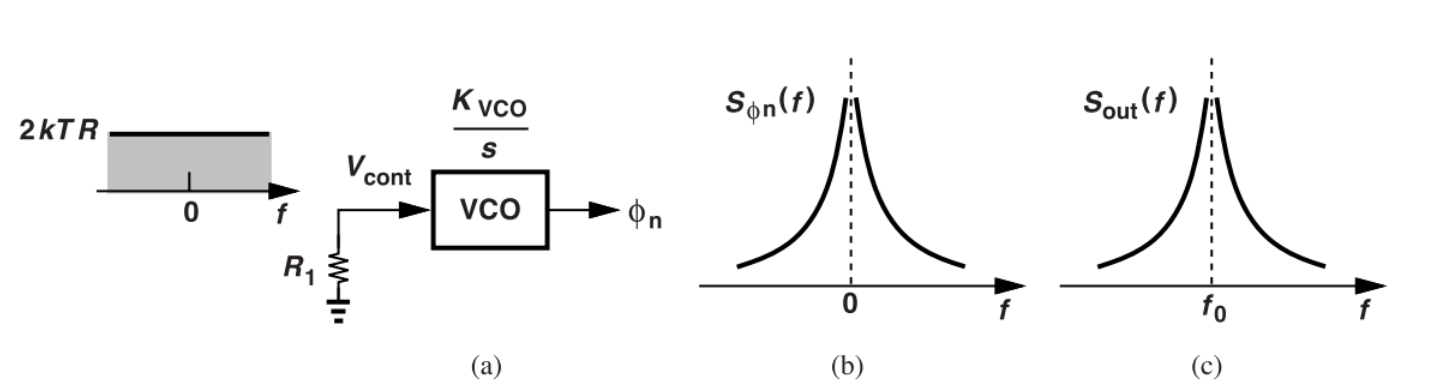

实例:在VCO输入处连接一个电阻,求其输出相位噪声谱和输出频率噪声谱。

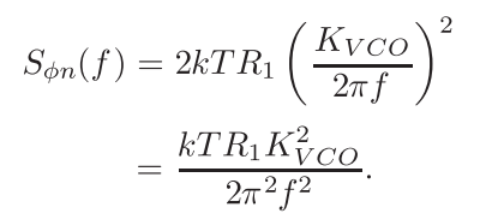

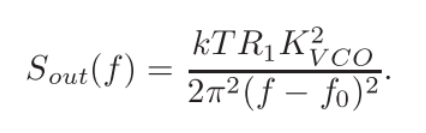

相位噪声频谱:

归一化:

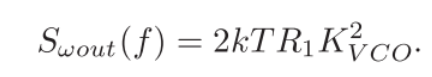

频率噪声频谱:

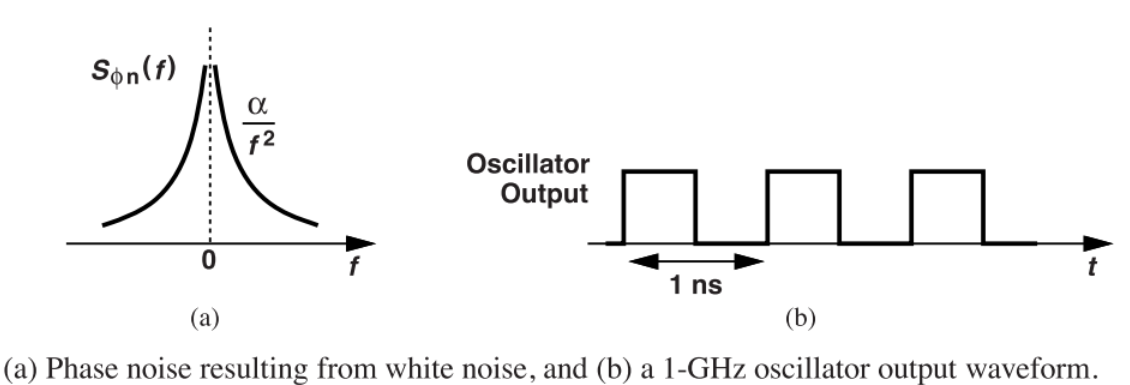

结论:任何通过白噪声调制振荡器频率的机制都会产生与1/ f2成比例的相位噪声轮廓。这是可以预料到的,因为频率和相位的相关系数是1/s。

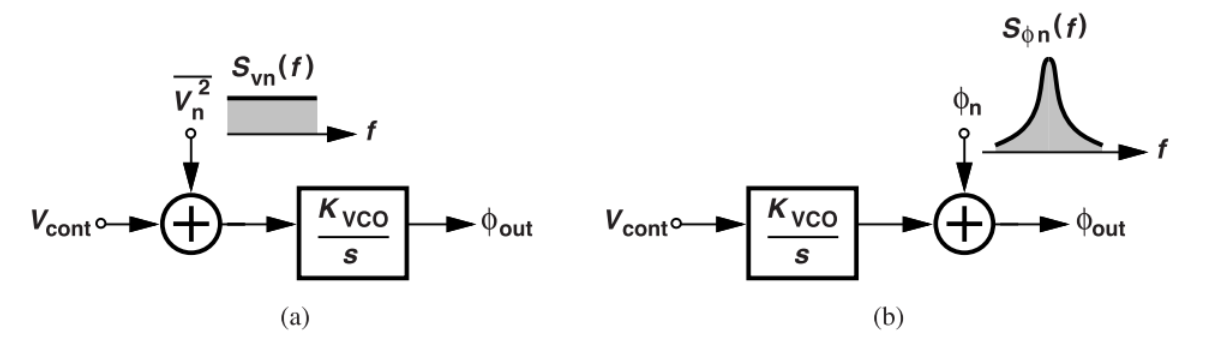

压控振荡器的相位噪声可以用两种不同的模型来表示:(1)作为一个电压量加到控制电压上[图(a)],或者(2)作为一个相位量加到输出相位上[图(b)]。当然,这两个相加方式具有不同的谱。

相位噪声和jitter之间的联系

把出现过的jitter概念总结一下,主要区分确定性成分和随机性成分。

| jitter(时域) | 确定性旁带+随机相位噪声 |

| 绝对jitter(Absolute Jitter) | 随机+确定,有噪声和无噪声VCO的相位差,无界 |

| 相位噪声(phase noise) | 随机波动 |

| 确定性jitter(Deterministic Jitter) | 确定性,频谱边带 |

| 峰峰值抖动(peak-to-peak jitter) | 确定性 |

| 随机jitter(random jitter) | 随机性 |

所以相位噪声只能和random jitter转化。

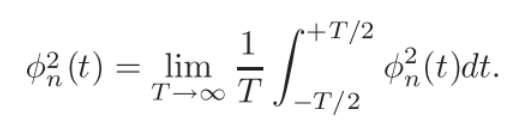

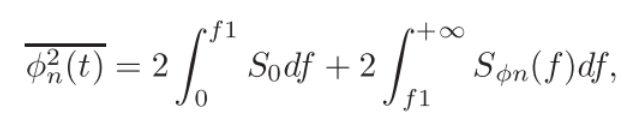

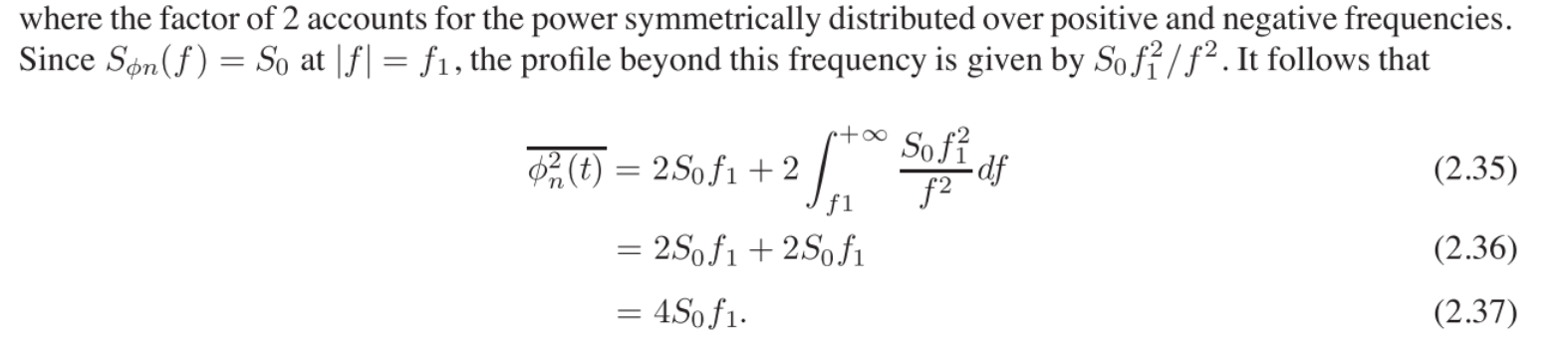

平均“功率”:

平均功率等于频谱下的面积:

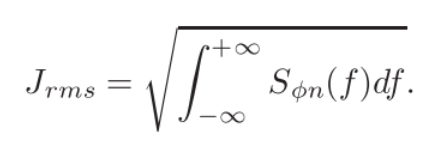

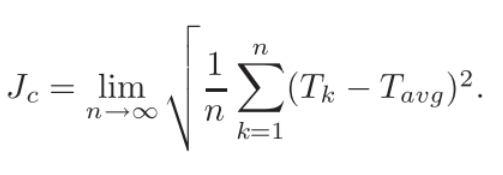

上式开根号,即为均方根抖动 rms jitter(Root Mean Square Jitter):

Jrms的单位是弧度,如果希望以秒表示,则必须除以2π并乘以周期。

实例:锁相环的输出相位噪声可以用图2.27所示的曲线来近似表示,其中Sφn(f)在|f| < f1时是平坦的,在|f| > f1时与1/ f2成比例下降。计算 rms jitter。

结论:rms jitter等于从0到f = +f1的频谱下面积的4倍。

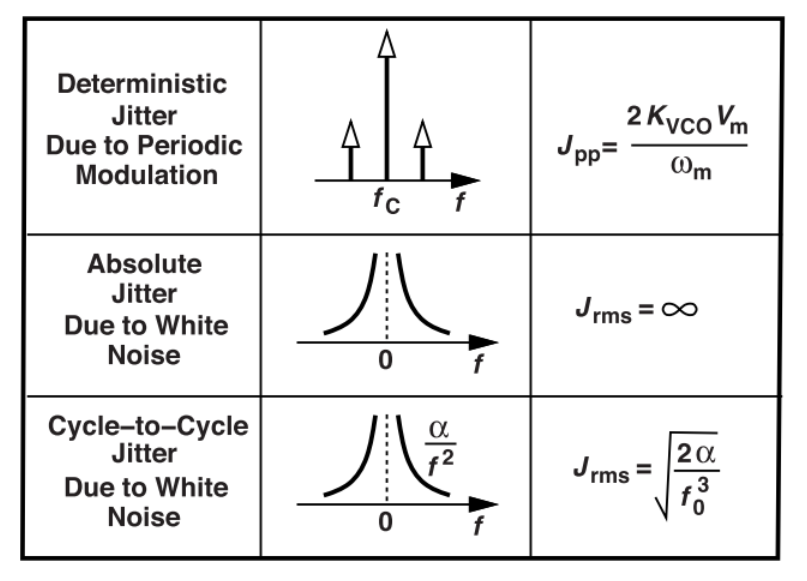

到目前为止,我们已经看到了两种类型的抖动:(a)确定性抖动,由周期性频率调制引起(表现为频谱中的边带),以及(b)绝对抖动,定义为以相同标称频率运行的有噪声振荡器和无噪声振荡器之间的相位差。

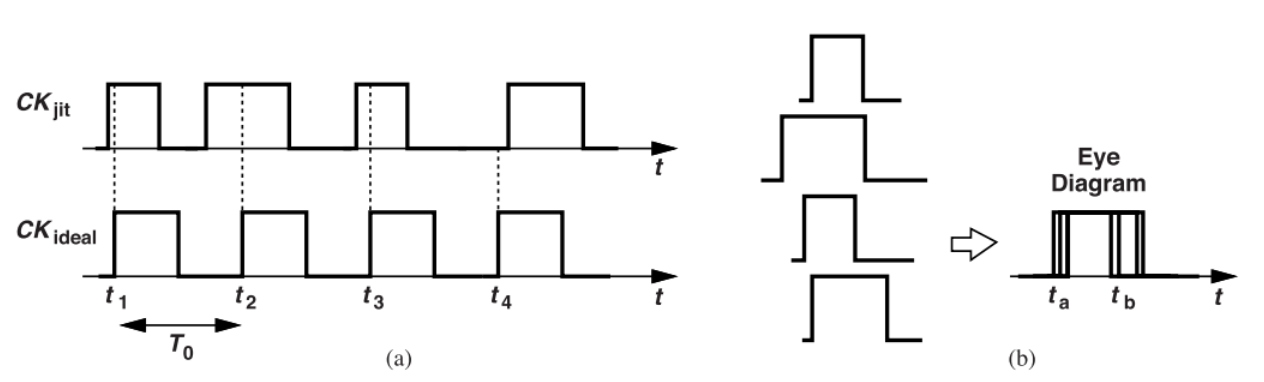

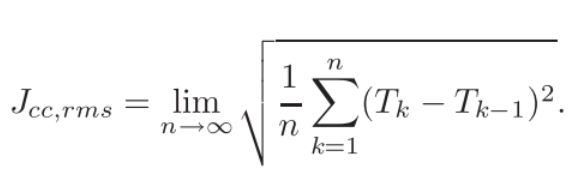

cycle-to-cycle jitter:

“周期到周期”抖动,Jcc,即连续周期之间的差异,Tk−Tk−1。

我们期望周期到周期的抖动非常小(但不可忽略!),因为相位噪声分量没有太多时间从一个输出周期累积到下一个。

图(a)所示的白噪声诱导的相位噪声分布图。我们假设φn(f) = α/ f2,其中α是常数。该剖面包含所有噪声频率,但随着|f|的增加,功率水平下降。假设此相位噪声出现在1 ghz振荡器的输出端[图2.28(b)]。由于每个周期为1ns长,我们推测只有高频相位噪声分量会在1ns后影响过零。例如,1 MHz左右的相位噪声分量可以用φ0 cos[2π(1 MHz)t]来近似,它在1 ns内的变化可以忽略不计。

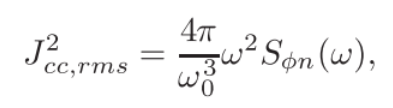

观察一段有限的时间,即一个周期,相位噪声会经历高通滤波。可以证明,对于白噪声诱导的相位噪声,在ω0工作的振荡器的cycle-to-cycle jitter等于:

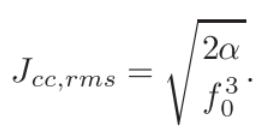

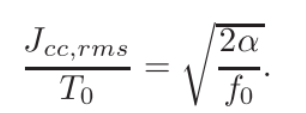

就好像Sφn(ω)经过了一个微分器。如果Sφn(ω)的形式是α/ f2,我们有

归一化到振荡周期T0 = 1/f0,结果为:

cycle jitter:另一种有界的抖动是“周期抖动”(也称为“周期抖动”)。表示周期与其平均值Tavg的随机偏离,该类型表示为:

对于白噪声引起的抖动,Jc = Jcc/√2

三种常见的抖动类型及其特点

确定性抖动可以从输出调频边带的幅度得到,绝对抖动对于独立振荡器来说是无界的。由白噪声源引起的周期间抖动的均方根由Eq计算。

参考:拉扎维,Design of CMOS Phase-Locked Loops

这篇关于Jitter 和相位噪声的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!