本文主要是介绍vivado Aurora 8B/10B IP核(2),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

端口说明 ( Port Descriptions )

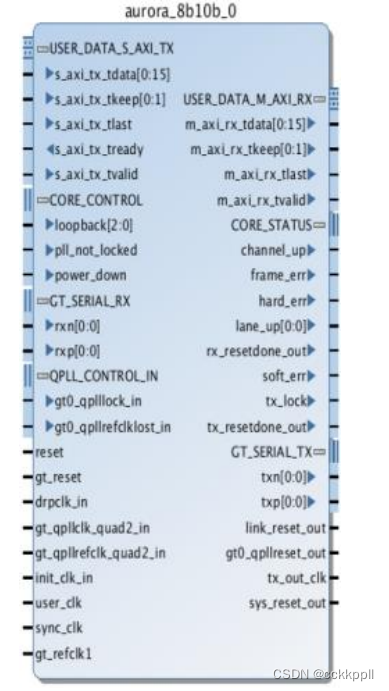

用于生成每个 Aurora 8B/10B 内核的参数决定了可用于该特定内核的接口。 接口在 IP 符号中

可见。 在 IP 符号中,如果左键单击界面旁边的+号,可以看到分组在其中的端口。 在

本节中,也就是端口描述,一般来说,界面显示为单行条目,后面是分组在其中的端口。 例如,USER_DATA_S_AXIS_TX 是接口,s_axi_tx_ *端口分组到该接口中。 核心有四到六个接口。

注意:

1.选择小端点支持选项时,使用[n:0]总线格式。

2.选择大端支持选项时,使用[0:n]总线格式。

3.端口为高电平,除非另有说明。

用户接口(User Interface):

Aurora 8B/10B 内核可以通过成帧或流用户数据接口生成。 该接口包括流或帧数据传输所需

的所有端口。帧用户接口符合 AMBA ® AXI4 流协议规范,包括发送和接收成帧用户数据所需的信号。流接口允许数据要发送没有帧分隔符,这样操作更简单,并且使用比帧接口少的资源。 数据端口宽度取决于通道宽度和所选通道数。

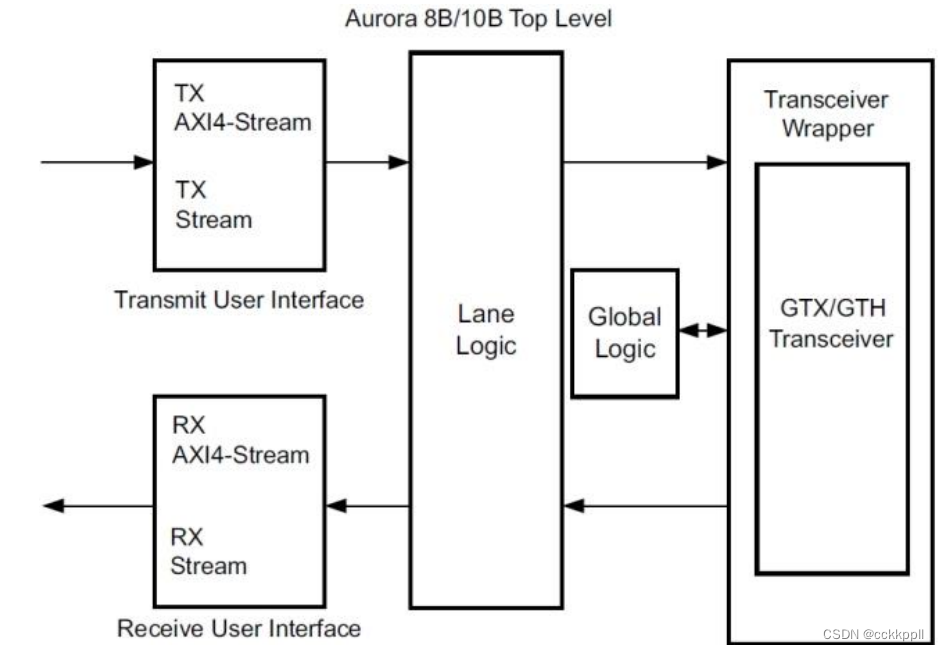

Top-Level Architecture(顶级架构)

Aurora 8B / 10B 核心顶层(块级)文件实例化了车道逻辑模块,TX 和 RX AXI4-Stream 模块,全局逻辑模块和收发器的包装器。 在示例设计中也实例化了时钟,复位电路,帧生成器和检测器模块。下图展示了双工配置的 Aurora 8B/10B 内核顶层。 顶级文件是用户设计的起点。

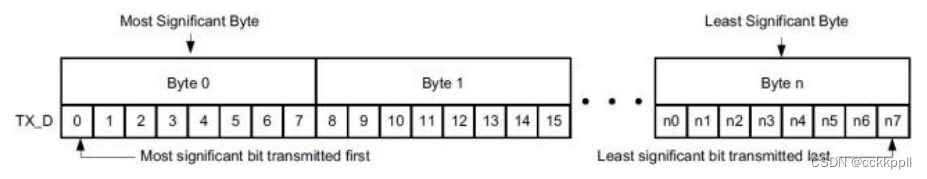

AXI4 数据流位排序(AXI4-Stream Bit Ordering):

Aurora 8B / 10B 内核采用升序排列。 它们首先发送和接收最高有效字节的最高有效位。 下

图显示了 Aurora 8B / 10B 内核的 AXI4-Stream 数据接口的 n 字节示例。

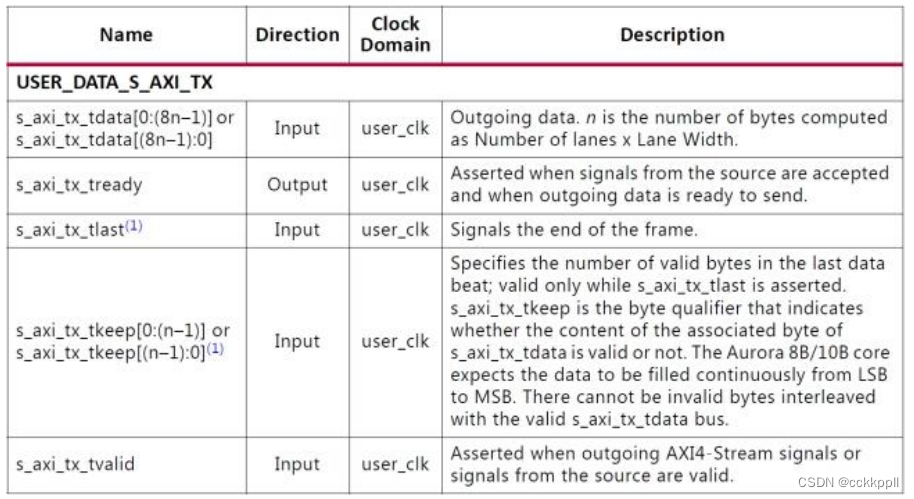

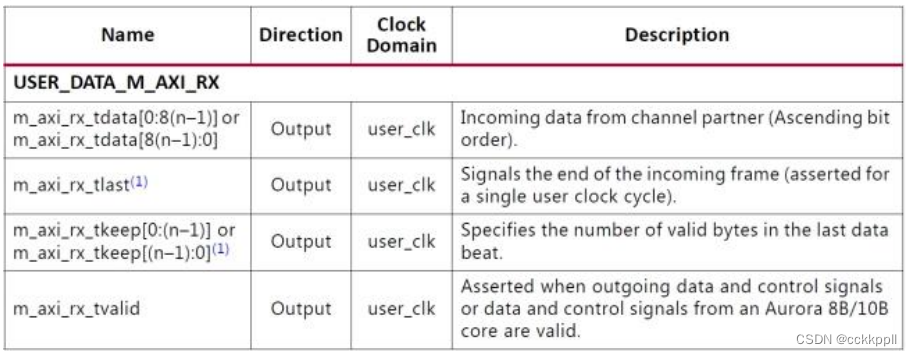

用户端口(User Interface Ports):

下表列出了双工和单工核心模块 AXI4-Stream TX 和 RX 数据端口的描述。

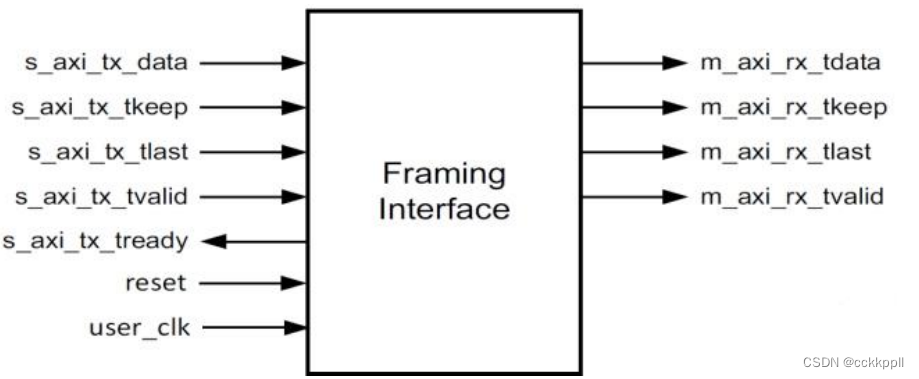

框架界面(Framing Interface)

下图显示了 Aurora 8B/10B 内核的成帧用户界面,AXI4-Stream 兼容端口用于 TX 和 RX 数据。

数据传输(Transmitting Data)

为了传输数据,用户应用程序操纵控制信号以使核心模块做到如下描述:

•从 s_axi_tx_tdata 总线上的用户端口获取数据

•s_axi_tx_tvalid 和 s_axi_tx_tready 信号被断言。

•在 Aurora 8B / 10B 通道中划分数据。

•使用 s_axi_tx_tvalid 信号传输数据。 用户应用程序可以设置 s_axi_tx_tvalid=0,以此插入空闲

(引入停顿或暂停)。

•暂停数据(即插入空闲)(s_axi_tx_tvalid 被取消置位)。

接收数据(Receiving Data)

当 IPCORE 接到数据时,它执行以下操作:

•检测和丢弃控制字节(空闲,时钟补偿,通道 PDU(SCP),通道协议数据单元结(ECPDU)和 PAD)。

•断开成帧信号(m_axi_rx_tlast)并指定有效字节数最后一个数据节拍(m_axi_rx_tkeep)。

•从车道恢复数据

•通过断言 m_axi_rx_tvalid 信号来组合数据以呈现给 m_axi_rx_tdata 总线上的用户接口。

只有当 s_axi_tx_tready 和 s_axi_tx_tvalid 都被断言时,Aurora 8B / 10B 内核才能采样(高)。

AXI4-Stream 数据仅在框架时有效。帧外的数据将被忽略。要启动一个帧,在 s_axi_tx_tdata

端口上的第一个数据字处于 assert s_axi_tx_tvalid 时。 要结束一个帧,在 s_axi_tx_tdata 端口

上的数据的最后一个字(或部分字)上使用 s_axi_tx_tlast,并使用 s_axi_tx_tkeep 来指定最后一

个数据节拍中的有效字节数。

在单个字长或更短的帧的情况下,s_axi_tx_tvalid 和 s_axi_tx_tlast 同时被断言。

这篇关于vivado Aurora 8B/10B IP核(2)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!