本文主要是介绍华为海思校园招聘-芯片-数字 IC 方向 题目分享——第九套,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

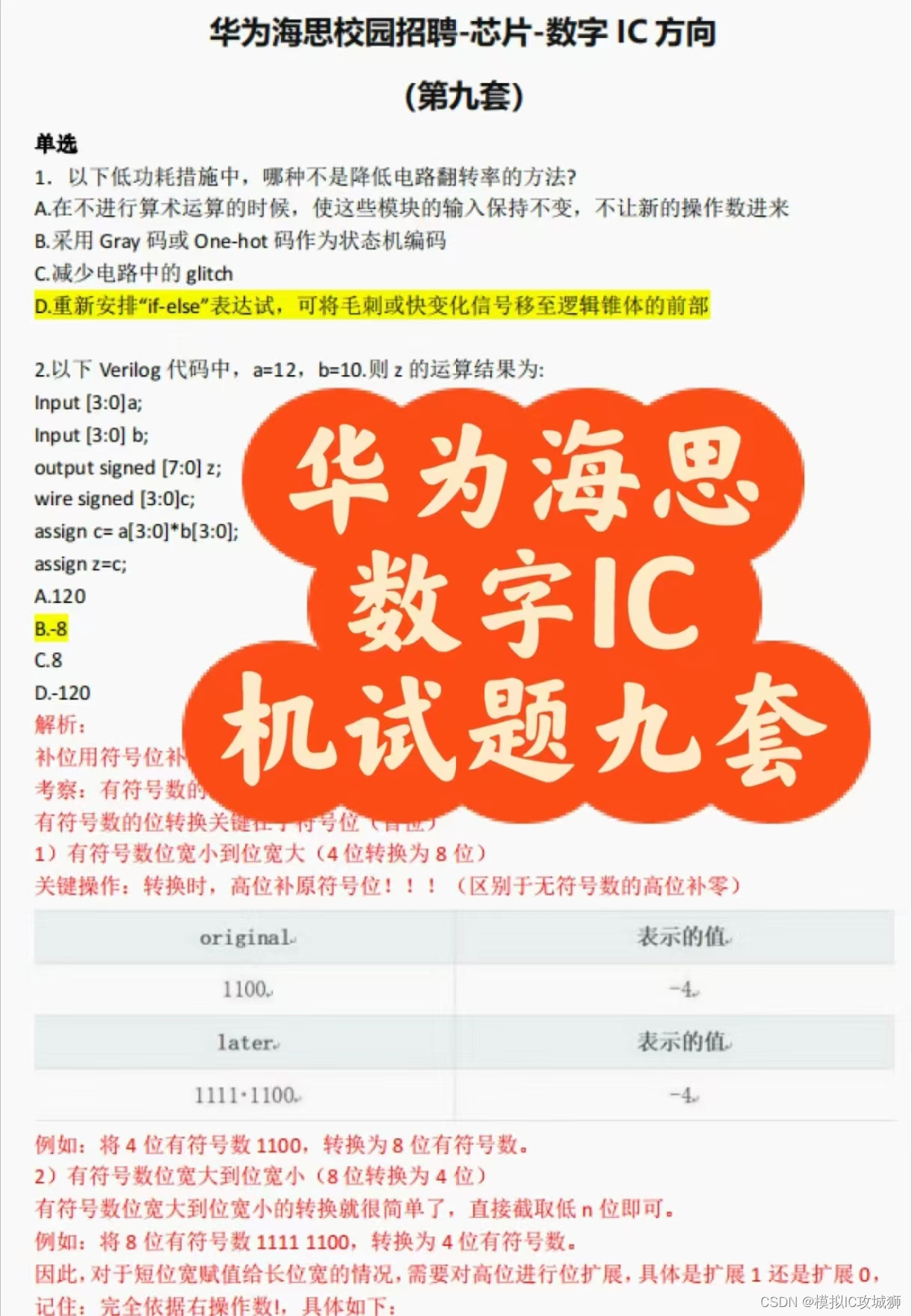

华为海思校园招聘-芯片-数字 IC 方向 题目分享(有参考答案)——第九套

部分题目分享,完整版获取(WX:didadidadidida313,加我备注:CSDN huawei数字芯片题目,谢绝白嫖哈)

单选

1.以下低功耗措施中,哪种不是降低电路翻转率的方法?

A.在不进行算术运算的时候,使这些模块的输入保持不变,不让新的操作数进来

B.采用 Gray 码或 One‐hot 码作为状态机编码

C.减少电路中的 glitch

D.重新安排“if‐else”表达试,可将毛刺或快变化信号移至逻辑锥体的前部

2.以下 Verilog 代码中,a=12,b=10.则 z 的运算结果为:

Input [3:0]a;

Input [3:0] b;

output signed [7:0] z;

wire signed [3:0]c;

assign c= a[3:0]b[3:0];

assign z=c;

A.120

B.‐8

C.8

D.‐120

解析:

补位用符号位补上。c=4’b1000‐‐>z=8’b11111000(最高位为符号位)

考察:有符号数的位宽转换

有符号数的位转换关键在于符号位(首位)

1)有符号数位宽小到位宽大(4 位转换为 8 位)

关键操作:转换时,高位补原符号位!!!(区别于无符号数的高位补零)

例如:将 4 位有符号数 1100,转换为 8 位有符号数。

2)有符号数位宽大到位宽小(8 位转换为 4 位)

有符号数位宽大到位宽小的转换就很简单了,直接截取低 n 位即可。

例如:将 8 位有符号数 1111 1100,转换为 4 位有符号数。

因此,对于短位宽赋值给长位宽的情况,需要对高位进行位扩展,具体是扩展 1 还是扩展 0,

记住:完全依据右操作数!,具体如下:

1)右操作数是无符号数,则无论左操作数是什么类型,高位都扩展成 0;

2)右操作数是有符号数,则要看右操作数的符号位,按照右操作数的符号位扩展,符号位

是 1 就扩展 1,是 0 就扩展 0;

3)位扩展后的左操作按照是无符号数还是有符号数解析成对应的十进制数值,如果是无符

号数,则直接转换成十进制数值,如果是有符号数,则看成 2 的补码解析成十进制数;

4)从上面 4 种情况看出,有符号数赋值成无符号数会出现数据错误的情况,因此要避免这

种赋值,而其他情况都是可以保证数据正确的。

3.constraint c_0{

src dist {0:=30, [1:3]:=90};

请问如上表达式约束,src 数值为 0 的概率为多大:( )

A. 0.2

B. 0.25

C. 0.1

D. 0.6

解析:

Systemverilog 中权重分布由操作符 dist 实现,有两种形式:“:=”或“:/”。

“:=”表示值的权重是相等的,“:/”表示值的权重是均分的。

权重不用百分比表示,权重和也不一定是 100.

例如:

src dist {0:=40; [1:3]:=60;};

即 src=0 的概率是 40/220,src=1 的概率是 60/220,是 2 的概率是 60/220,是 3 的概率是

60/220.

再例如:

dst dist {0:/40; [1:3]:/60;};

即 dst=0 的概率是 40/100,dst=1 的概率是 20/100,是 2 的概率是 20/100,是 3 的概率是

20/100.

综上:src dist {0:=30; [1:3]:=90;}; dst=0 的概率是 30/(903+30)=30/300=0.1

4.分析下面的一段程序,正确的打印结果是:

fork

begin

#20

$ display(“A”);

end

begin

#10

$ display(“B”);

end

join_none

#5

$ display(“C”);

A.CBA

B. BCA

C.ABC

D.C

解析:

https://blog.csdn.net/qq_31348733/article/details/100382377

1)join:The parent process blocks until all the processes spawned by this fork complete.

简单来说:fork…join 内的所有语句都是并发执行(对于 begin…end 内部是顺序执行)

2)join_any:The parent process blocks until any one of the processes spawned by this fork

completes.

简单来说:一旦 fork…join_any 内任何一个线程完成,父线程就会继续运行

3)join_none:The parent process continues to execute concurrently with all the processes spawned

by the fork. The spawned processes do not start executing until the parent thread executes a

blocking statement or terminates.

简单来说:子线程和父线程会同时执行。

5.下面有关 Cache 的说法哪一个是不正确的?

A. 设置 Cache 的理论基础,是程序访问的局部生原理

B. Cache 与主存统一编址,Cache 的地址空间属于主存的一部分

C. 设置 Cache 的目的,是解决 CPU 和主存之间的速度匹配问题

D. Cache 的功能匀由硬件实现,对程序员是透明的

解析:

A:使用 Cache 改善系统性能的依据是程序的局部性原理 [1]

B:cache 的地址与内存地址是两码事,不统一编址,也没有从属关系

C:Cache 是介于 CPU 和主存之间的小容量存储器,存取速度比主存快,接近 CPU。它能高

速地向 CPU 提供指令和数据,提高程序的执行速度。Cache 技术是为了解决 CPU 和主存之

间速度不匹配而采用的一项重要技术。

D:Cache 是主存的缓冲存储器,由高速的 SRAM 组成,所有控制逻辑全部由硬件实现,对

程序员而言是透明的。随着半导体器件集成度的不断提高,当前有些 CPU 已内置 Cache,并

且出现了两级以上的多级 Cache 系统。

Cache 通常采用相联存储器。Cache 又分为 L1Cache(一级缓存)和 L2Cache(二级缓存),

L1Cache 主要是集成在 CPU 内部,而 L2Cache 集成在主板上或是 CPU 上。

6.对于独立复位的模块,只需要考虑对后级模块的影响,无需考虑对前级模块的影响。

A.正确

B.错误

解析:B 考虑到可能会存在反馈电路,因此选择错误。

7.System Verilog 中,下面那种数组在使用前需要先执行 new 操作( )

A. Dynamic arrays

B. Associative arrays

C. packed array

D. 多维数组

8.System Verilog 中,下面哪种数组在使用前需要执行 new 操作( )

a.压缩数组

b.联合数组

c.动态数组

d.多维数组

解析:动态数组通过 new ( )函数预先分配存储空间。

9.下列哪个不是 Verilog 系统函数( )

A. $ finish

B. $ head

C. $ time

D. $ write

解析:

r e a d m e m b 和 readmemb 和 readmemb和readmemh 用来从文件中读取数据到存贮器中。

$finish 的作用是退出仿真器,返回主操作系统,也就是结束仿真过程。

$write(p1,p2,…pn);输出信息,即将参数 p2 到 pn 按参数 p1 给定的格式输出。

$time 返回一个 64 位的整数来表示当前的仿真时刻值

10.以下 Verilog 运算符号中,优先级最高的是?

A.==

B.“

C.!

D.?:

解析:

11.模块只收敛做到 0.75V,提压到 0.85V 可以正常工作

A.正确

B.错误

12.异步电路都不需要 STA 进行约束检查

A.是

B.否

解析:STA 都是针对同步电路的

13.在设计状态机时,有两种常用的编码方式:one‐hot code、binary code,前者相对于后者

的优势主要体现在

A.实现电路的速度更快

B.实现电路的面积更小

C.编码方式简单

D.实现电路的功耗更低

解析:

独热码和二进制码的优缺点比较:

二进制码、格雷码使用最少的触发器,但是消耗较多的组合逻辑(用于译码) ;

独热码则正好相反,因为状态比较时仅需要比较一位,从而在一定程度上简化了译码逻辑。

虽然在表示同样的状态时,独热码占用较多的位,也就是消耗较多的触发器,但这些额外的

触发器占用面积可与译码电路省下来的面积相抵消。

在 CPLD 更多的提供组合逻辑,而 FPGA 提供更多的触发器资源,所以在 CPLD 中更多的使用

二进制、格雷编码,在 FPGA 中更多使用独热编码。

另一方面,对于小型设计 gray‐code 和 binary‐code 编码更有效。对于大型设计,one‐hot 编

码更高效。

14.对于相同位数输入的变量比较器,大于和小于的面积是一样的

A.对

B.错误

解析:需要考虑有无符号位,如果无符号,大小面积相同;有符号是不同

15.有关综合的说法,以下哪个选项是错误的?

A. 相同的 RTL 代码,每次综合出来的网表可能是不一样的

B. 综合网表可用于 EDA 功能仿真

C. casez 是不可综合的

D. 时序逻辑 always 语句中,if‐else 如果 else 的分支缺乏,会综合成 latch

解析:

在组合逻辑中,当缺少嵌套 if‐else 语句中的最后一个 else 子句时,它将推断一个锁存器,因

为寄存器必须记住原来的值。

在一个时序逻辑的 always 语句块中,如果最后的 else 语句丢失,仍然会继续推断出触发器。

16.在 Verilog 代码中,对有符号数进行比特选择或拼接,其结果是无符号数

A.正确

B.错误

解析:

(1)对于长位宽赋值给短位宽的情况,无论左操作数、右操作数是有符号数还是无符号数,

都是直接截断高位,而左操作数二进制所表示的实际十进制数据要看左操作数是无符号数还

是有符号数,如果左操作数是无符号数,直接转换成十进制即可,如果是有符号数,则看成

2 的补码解析成十进制数,这也是实际计算机系统中有符号数的表示方法。

(2)对于短位宽赋值给长位宽的情况,需要对高位进行位扩展,具体是扩展 1 还是扩展 0,

记住:完全依据右操作数!,具体如下:

1)右操作数是无符号数,则无论左操作数是什么类型,高位都扩展成 0;

2)右操作数是有符号数,则要看右操作数的符号位,按照右操作数的符号位扩展,符号位

是 1 就扩展 1,是 0 就扩展 0;

3)位扩展后的左操作按照是无符号数还是有符号数解析成对应的十进制数值,如果是无符

号数,则直接转换成十进制数值,如果是有符号数,则看成 2 的补码解析成十进制数;

4)从上面 4 种情况看出,有符号数赋值成无符号数会出现数据错误的情况,因此要避免这

种赋值,而其他情况都是可以保证数据正确的。

这篇关于华为海思校园招聘-芯片-数字 IC 方向 题目分享——第九套的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!