本文主要是介绍用状态机实现简单的自动售卖机(Verilog)并验证,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

一、设计要求

二、分析

1、输入输出

(1)input

(2)output

2、状态

3、状态机

三、源代码

1、FSM.v

2、FSM_tb.v

四、仿真波形

一、设计要求

使用FSM实现自动售卖机。FSM的概念可参考:https://blog.csdn.net/qq_42922513/article/details/130828381![]() https://blog.csdn.net/qq_42922513/article/details/130828381售卖机描述:商品为可乐,一瓶可乐5元钱,每次只能投三种人民币中的一种,分别是:1元,2元,5元。当投够5元时,出一瓶可乐,并找零。

https://blog.csdn.net/qq_42922513/article/details/130828381售卖机描述:商品为可乐,一瓶可乐5元钱,每次只能投三种人民币中的一种,分别是:1元,2元,5元。当投够5元时,出一瓶可乐,并找零。

二、分析

1、输入输出

(1)input

输入包括:时钟信号clk,低电平复位信号rst_n,投币in_m

clk, rst_n, [3:0] in_m;(2)output

输出包括:可乐goods,找零out_m

goods, [3:0] out_m;2、状态

根据售卖机中有多少钱,将状态机共划分为5个状态,分别为:IDLE(0元)、S0(1元)、S1(2元)、S2(3元)、S3(4元)。

3、状态机描述

本文采用mealy型状态机。对各状态采用独热码进行编码,5个状态需要5bit。

三、源代码

1、FSM.v

`timescale 1ns/1nsmodule FSM (input clk,input rst_n,input [3:0] in_m,output reg goods,output reg [3:0] out_m

);reg [4:0] CS, NS;parameter [4:0]IDLE = 'b00001,S0 = 'b00010,S1 = 'b00100,S2 = 'b01000,S3 = 'b10000;//第一always块,同步时序逻辑

always @ (posedge clk or negedge rst_n) beginif (!rst_n)CS <= IDLE;elseCS <= NS;

end//第二always块,组合逻辑

always @ (*) begincase (CS)IDLE:if (in_m == 4'd1) NS = S0;else if (in_m == 4'd2) NS = S1;else if (in_m == 4'd5) NS = IDLE;else NS = IDLE;S0:if (in_m == 4'd1) NS = S1;else if (in_m == 4'd2) NS = S2;else if (in_m == 4'd5) NS = IDLE;else NS = S0;S1:if (in_m == 4'd1) NS = S2;else if (in_m == 4'd2) NS = S3;else if (in_m == 4'd5) NS = IDLE;else NS = S1;S2:if (in_m == 4'd1) NS = S3;else if (in_m == 4'd2) NS = IDLE;else if (in_m == 4'd5) NS = IDLE;else NS = S2;S3:if (in_m == 4'd1) NS = IDLE;else if (in_m == 4'd2) NS = IDLE;else if (in_m == 4'd5) NS = IDLE;else NS = S3;default:NS = IDLE;endcase

end//第三always块,同步时序逻辑

always @ (posedge clk or negedge rst_n) beginif (!rst_n) beginout_m <= 'd0;goods <= 'd0;endelse begincase (CS)IDLE: beginout_m <= 'd0;if (in_m == 'd5) goods <= 'd1;else goods<= 'd0;endS0: beginout_m <= 'd0;if (in_m == 'd1 || in_m == 'd2) begingoods <= 'd0;out_m <= 'd0;endelse begingoods <= 'd1;out_m <= 'd1;endendS1: beginout_m <= 'd0;if (in_m == 'd1 || in_m == 'd2) begingoods <= 'd0;out_m <= 'd0;endelse begingoods <= 'd1;out_m <= 'd2;endendS2: beginout_m <= 'd0;if (in_m == 'd1) begingoods <= 'd0;out_m <= 'd0;endelse if (in_m == 'd2) begingoods <= 'd1;out_m <= 'd0;endelse begingoods <= 'd1;out_m <= 'd3;endendS3: begingoods <= 'd1;if (in_m == 'd1) out_m <= 'd0;else if (in_m == 'd2) out_m <= 'd1;else out_m <= 'd4;enddefault: begingoods <= 'd1;out_m <= 'd0;endendcaseend

end

endmodule2、FSM_tb.v

//FSM_tb.v`timescale 1ns/1nsmodule FSM_tb;reg clk;

reg rst_n;

reg [3:0] in_m;

wire [3:0] out_m;

wire goods;FSM u(.clk(clk),.rst_n(rst_n),.in_m(in_m),.goods(goods),.out_m(out_m)

);initial beginrst_n = 'b0;clk = 'b0;#50rst_n = 'b1;

endalways #20 clk = ~clk;initial beginin_m = 0;#50in_m = 'd1;#40in_m = 'd1;#40in_m = 'd1;#40in_m = 'd1;#40in_m = 'd1;#40in_m = 'd2;#40in_m = 'd2;#40in_m = 'd2;#40in_m = 'd5;#40in_m = 'd2;#40in_m = 'd5;#40$stop;

endendmodule3、FSM_tb.sv

使用system verilog进行随机验证。SV相关基础可参考:System Verilog基础_qq_42922513的博客-CSDN博客![]() https://blog.csdn.net/qq_42922513/article/details/130984574

https://blog.csdn.net/qq_42922513/article/details/130984574

//FSM_tb.sv

`timescale 1ns/1nsmodule FSM_tb;bit clk;

bit rst_n;

bit [3:0] in_m;

bit [3:0] out_m;

bit goods;FSM u(.clk(clk),.rst_n(rst_n),.in_m(in_m),.goods(goods),.out_m(out_m)

);initial beginrst_n = 'b0;clk = 'b0;#50rst_n = 'b1;

endalways #20 clk = ~clk;class packet;rand bit [3:0] money_in;constraint c{money_in dist{1:=1, 2:=1, 5:=1};}

endclassinitial beginin_m = 0;packet M;M = new();#50repeat(20) beginassert(M.randomize());in_m = M.money_in;$display("******* in_m = %0d********/n", in_m);#40;end#40$stop;

endendmodule四、仿真波形

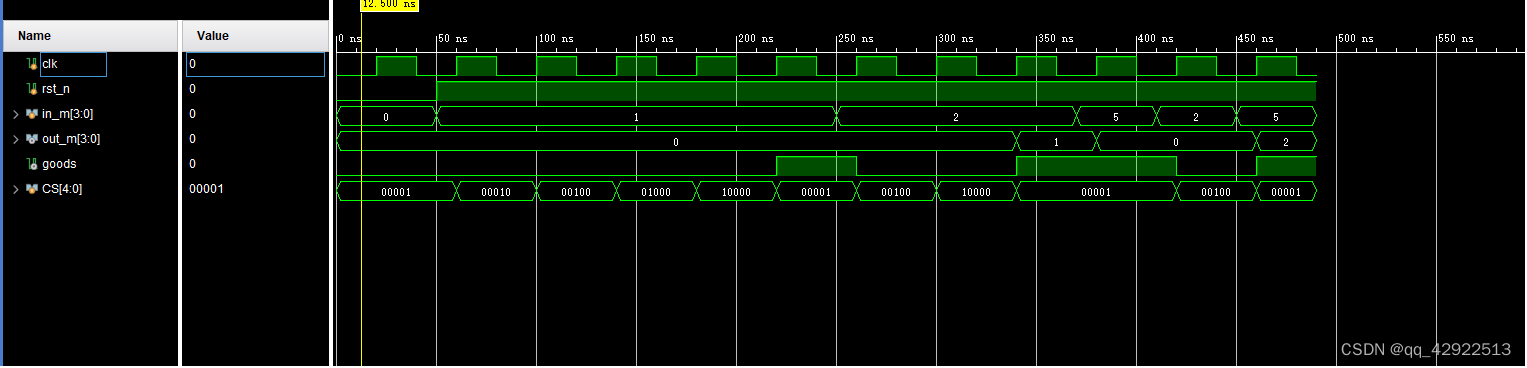

1、工具:VIVADO,testbench文件:FSM_tb.v

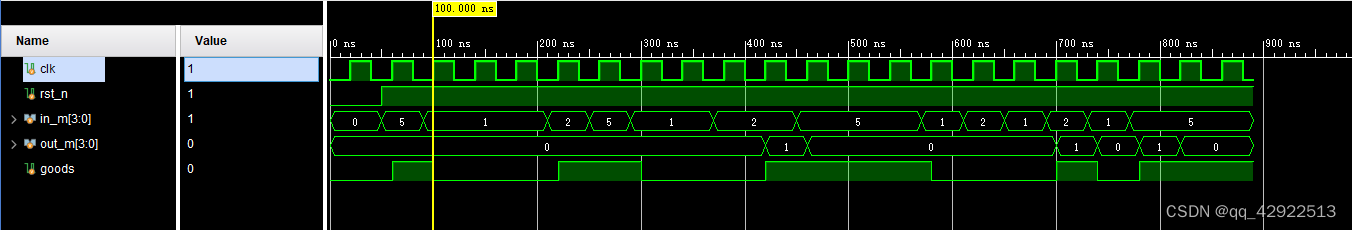

2、工具:VIVADO,testbench文件:FSM_tb.sv

PS:如果觉得有用可以点赞并收藏!!!

这篇关于用状态机实现简单的自动售卖机(Verilog)并验证的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!