本文主要是介绍【牛客】VL69 脉冲同步器(快到慢),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

描述

sig_a 是 clka(300M)时钟域的一个单时钟脉冲信号(高电平持续一个时钟clka周期),请设计脉冲同步电路,将sig_a信号同步到时钟域 clkb(100M)中,产生sig_b单时钟脉冲信号(高电平持续一个时钟clkb周期)输出。请用 Verilog 代码描述。

clka时钟域脉冲之间的间隔很大,无需考虑脉冲间隔太小的问题。

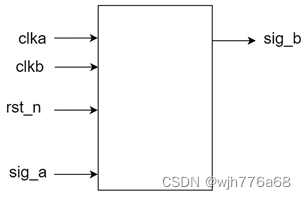

电路的接口如下图所示:

输入描述:

input clka ,

input clkb ,

input rst_n ,

input sig_a ,

输出描述:

output sig_b

`timescale 100ps/100psmodule pulse_detect(input clka , input clkb , input rst_n ,input sig_a ,output sig_b

);reg sig_a_r = 1'b0;reg sig_a_pulse_r = 1'b0;reg sig_a_pulse_clkb_r = 1'b0, sig_a_pulse_clkb_d1_r = 1'b0,sig_a_pulse_clkb_d2_r = 1'b0;always @(posedge clka, negedge rst_n) beginif (~rst_n) beginsig_a_r <= 1'b0;end else beginsig_a_r <= sig_a;endendalways @(posedge clka, negedge rst_n) beginif (~rst_n) beginsig_a_pulse_r <= 1'b0;end else beginif (~sig_a_r & sig_a) begin // 仅同步sig_a上升沿sig_a_pulse_r <= ~sig_a_pulse_r;endendendalways @(posedge clkb, negedge rst_n) beginif (~rst_n) beginsig_a_pulse_clkb_r <= 1'b0;sig_a_pulse_clkb_d1_r <= 1'b0;sig_a_pulse_clkb_d2_r <= 1'b0;end else beginsig_a_pulse_clkb_r <= sig_a_pulse_r;sig_a_pulse_clkb_d1_r <= sig_a_pulse_clkb_r;sig_a_pulse_clkb_d2_r <= sig_a_pulse_clkb_d1_r;endendassign sig_b = sig_a_pulse_clkb_d1_r ^ sig_a_pulse_clkb_d2_r;endmodule

这篇关于【牛客】VL69 脉冲同步器(快到慢)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![笔试强训,[NOIP2002普及组]过河卒牛客.游游的水果大礼包牛客.买卖股票的最好时机(二)二叉树非递归前序遍历](https://i-blog.csdnimg.cn/direct/17efc4d0a1b749cb89ebdd715e23402b.png)