本文主要是介绍基于ZYNQ的PCIE高速数据采集卡的设计(三)硬件设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

采集卡硬件设计

3.1 引言

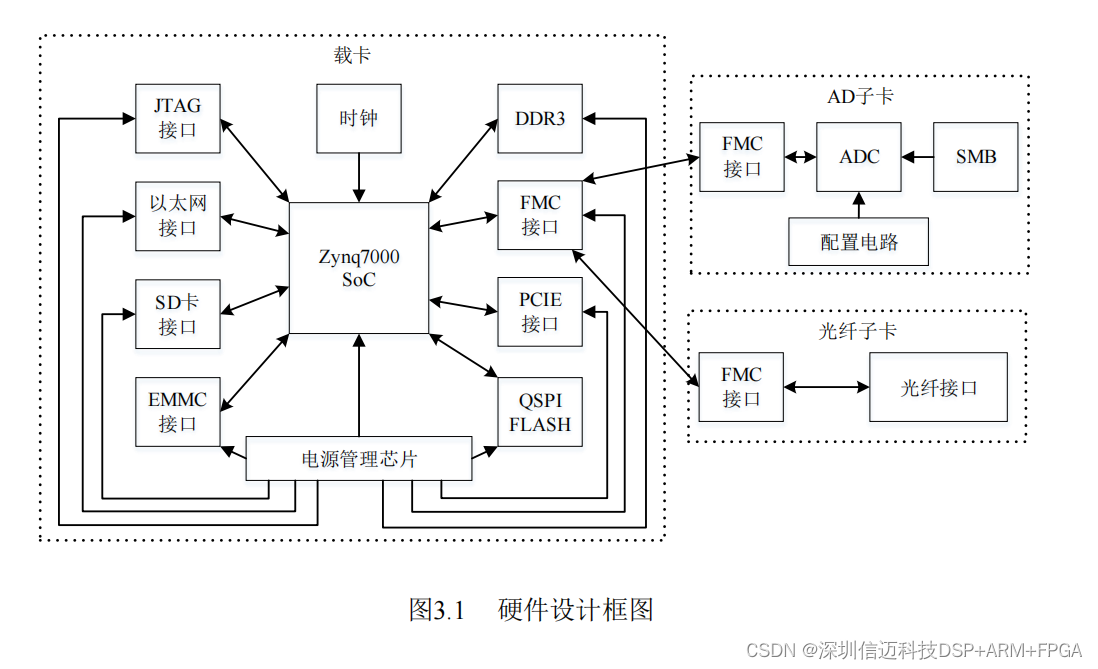

采集卡的硬件设计是实现采集功能的基础,良好的硬件设计可以使采集功能更容

易实现,方便软件开发。本章基于第二章的硬件设计方案来详细介绍采集卡硬件设计。

包括载卡和子卡的芯片的选型、配置和具体电路的设计。载卡和子卡的硬件设计总体

框图如图 3.1 所示。

3.2 载卡硬件设计

3.2.1

主控芯片选型及配置电路

( 1 )主控芯片选型及分析

根据第二章采集卡硬件设计分析结果,控制芯片需满足以下条件:

芯片包含高速 GTX 接口,不少于 12 对,其中光纤 4 对, PCIE8 对;

片内具有足够的 BRAM 资源,用作 FIFO 接口;

芯片支持 Aurora 及 PCIE2.0 协议;

芯片具有外设接口,方便调试,可移植性好。

综合以上需求,主控芯片选择 Xlinx 公司 Zynq7000 系列 SoC ,该产品分类及 PL

部分的资源如表 3.1 所示 [23] 。

由表 3.1 可知, Zynq-7135 以下的产品能满足本采集卡的设计条件,通过对比分

析,选择 Zynq-7100 系列型号为 XC7Z100FFG900-2 的芯片,该芯片内部包含以双

ARM Cortex-A9 为核心的 PS 部分和以 Xilinx Kintex7 系列 FPGA 为核心的 PL 部分。

3.3 子卡的电路设计

3.3.1

AD 子卡的电路设计

AD 子卡完成模拟信号的数字转换,并通过 FMC 接口发送至采集卡的 Zynq 芯

片。

ADC 芯片采用 TI 公司的型号为 ADC12D800 芯片,该芯片最大采样率为 1.6Gbps ,

分辨率为 12bit 。转换结果根据芯片的配置,能以 12 组差分对的形式输出,也可以分

别作为数据线并行输出。该 ADC 芯片支持两通道的数据转换,分别为 I 通道和 Q 通

道,每个通道有独立的数据线,芯片支持单边沿采样和双边沿采样,通过时钟和控制

接口来控制芯片的工作模式。

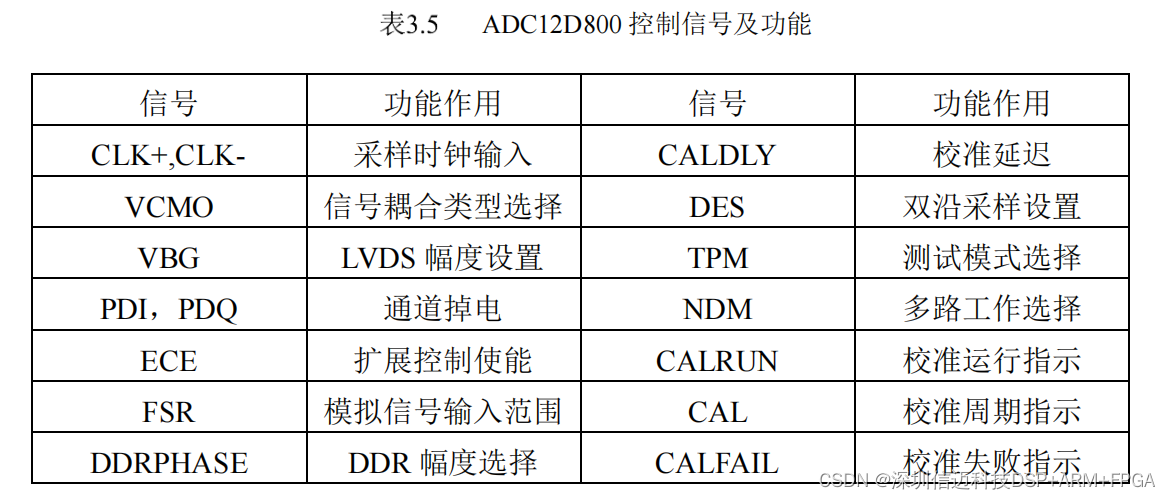

芯片的时钟和控制接口及功能如表 3.5 所示。

芯片还配有 SPI 总线接口,在 ADC 芯片工作在延伸控制模式时, SPI 接口可以

用来对 ADC 进行配置,完成偏置、校准等功能。由于本次设计没有涉及到 SPI 总线,

因此这里不在对 SPI 的配置方式和寄存器功能进行赘述。

ADC 芯片电压采用差分输入的形式,本次设计为模拟信号以交流耦合的方式进

入 ADC 芯片,模拟信号经过 SMB 射频接口后,经电路转换为两路差分信号进入 ADC

芯片。电路图如图 3.13 所示。

3.3.2

光纤子卡的电路设计

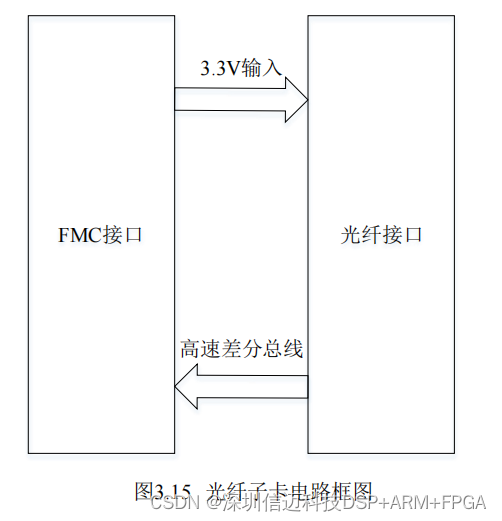

光纤子卡完成了光纤接口到 FMC 接口的转接,光纤接口采用 1761987-9 的 QSFP

接口,该接口提供 4 路高速差分接口,通常搭配光纤接口使用,接口提供了一种小型

化和高速传输的解决方案。

本次设计采用的光纤接口型号为 SR4-40G 的光纤插头,该接头提供 40Gbps 的传

输速率,传输距离可达 150m 。光纤接口需要 3.3V 供电,电源由采集卡的 FMC 接口

提供。并将 4 对高速差分线引至 FMC 接口,光纤子卡的框图如图 3.15 所示。

这篇关于基于ZYNQ的PCIE高速数据采集卡的设计(三)硬件设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!