本文主要是介绍基于ZYNQ的PCIE高速数据采集卡的设计(二)总体设计与上位机,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

采集卡总体设计及相关技术

2.1 引言

本课题是来源于雷达辐射源识别项目,需要对雷达辐射源中频信号进行采集传输

和存储。本章基于项目需求,介绍采集卡的总体设计方案。采集卡设计包括硬件设计

和软件设计。首先对采集卡的性能和指标进行分析,接着提出硬件的总体设计,在硬

件设计基础上提出软件的总体设计,最后对用到的相关协议与关键技术进行说明。

2.2 总体设计概述

2.2.1

采集系统指标分析

本项目中雷达辐射源中频信号频带为 760MHz ~ 1060MHz ,该雷达信号是一种带

通信号。采用带通采样定理,可以使采样率降低,进而降低数据传输速率。使得硬件

和软件更容易实现。

就可以从采样值恢复出原始信号

。其中, m 是一个不超过

的最大整数。

由公式 2-1 得,雷达辐射源信号的采样率大于 706.6Msa/s 时,就可以从采样的数

据中恢复出原始信号。实际中由于滤波器的特性不很理想,如果信号采样率过低,会

引起频谱混叠现象,导致恢复出的信号质量过差。因此实际采样率要高于理论的采样

率,才能保证恢复出的信号质量。本次设计的 AD 子卡的最大采样率为 1.6Gsa/s ,采

样精度为 12 位,数据最大速率为 19.2Gbps ,可满足项目数据采集要求。

采样后的数据形成高速数据流通过高速接口进入处理器,需要高效稳定的处理器

和高速数据传输协议技术来完成数据的接收、处理和发送。 Zynq7000 系列 SoC 内部

集成了以 FPGA 为基础的 PL 部分和以 ARM 为核心的 PS 部分,可单芯片实现数据

采集和数据处理功能。本文设计提供的 AD 子卡可实现雷达模拟信号的 AD 转换,并

形成高速数据流传输至采集卡。

由于高速接口不同,协议和传输速率也不同,如果采取直连的方式,可能会有数

据丢失的现象发生,在某些情况下,需要一定量的数据才可以进行处理,这需要一种

数据缓存技术解决。一般采用 DDR3 SDRAM 芯片用做高速数据缓存, DDR3 SDRAM

可以在时钟的双边沿进行数据读写,目前 DDR3 SDRAM 芯片颗粒支持最高频率的工

作时钟为 800MHz ,若 DDR3 SDRAM 芯片的数据线宽度为 16 位,则单片 DDR3

SDRAM 读写速率理论上最大为 25.6Gbps 。实际使用中需多片 DDR3 芯片搭配使用,

即可以扩大数据容量和位宽,又可以使数据读写速度得到成倍的提升。本设计从小型

化方面考虑,在 Zynq 芯片的 PL 端和 PS 端分别采用 2 片 16 位的 DDR3 SDRAM 芯

片组成 32 位宽的缓存器。

本设计的高速接口选用 PCIE 接口,为了满足雷达信号采样数据传输速率的要求,

PCIE 接口的速率应不低于 19.2Gbps 。经分析,选择 PCIE2.0 协议, x8 模式,可提供

40Gbps 的数据传输速率,能满足本项目的数据传输要求。

2.2.2

硬件总体设计

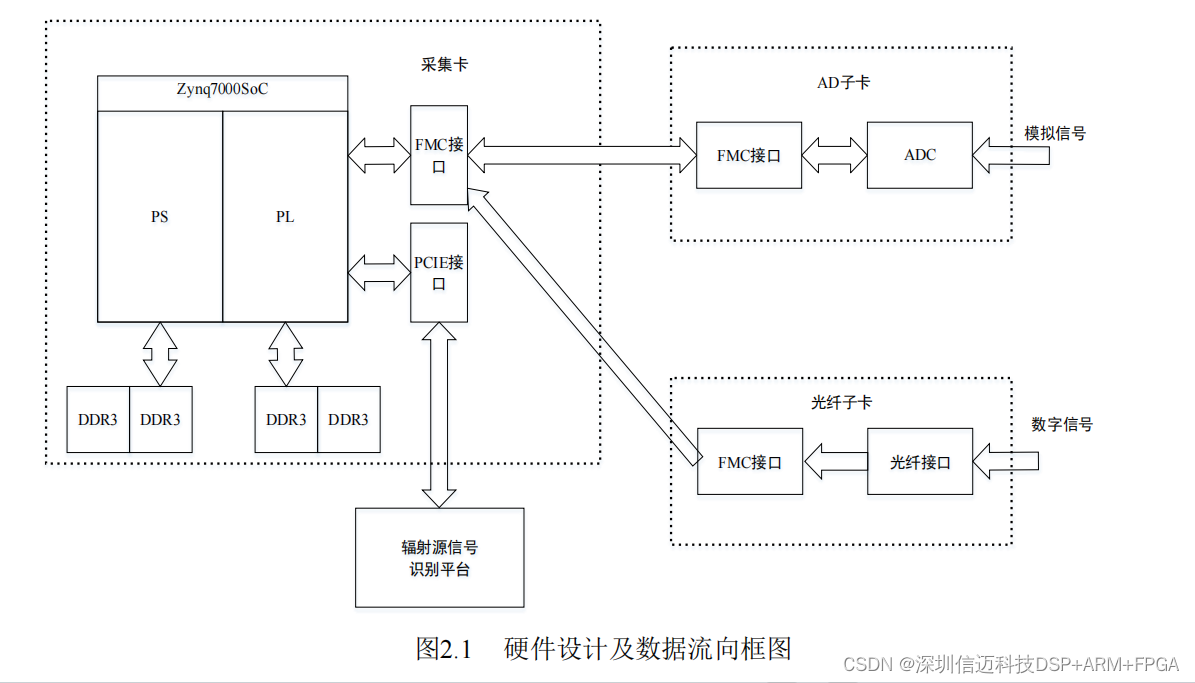

本节基于上一节的分析结果给出硬件总体设计。硬件设计及数据流向框图如图

2.1 所示:

为了灵活设计,采集系统采用载卡 + 子卡的方式,载卡和子卡之间用 FMC 接口

连接,可以满足不同子卡的数据传输。载卡的设计方式为核心板 + 底板,核心板为

Zynq7000 SoC 的最小系统,并经接插件引出芯片的接口至底板,底板主要是给核心

板供电和连接 Zynq7000 SoC 的外围接口。为了使采集系统适用于多种场合,采集系

统提供光纤子卡和 AD 子卡两种方式进行数据采集传输,其中,光纤子卡用来接收高

速数字信号, AD 子卡用来对辐射源信号进行模 - 数转换,形成高速数据流,子卡输出

的高速数据经 FMC 接口进入 Zynq 芯片,再经 PCIE 接口传输至辐射源信号识别平台

进行后续处理。

AD 子卡的模拟信号输入采用 SMB 射频接头,采用 TI 公司的 ADC 芯片,型号

为 ADC12D800 。该 ADC 最大采样率为 1.6Gsa/s ,分辨率为 12bit , AD 转换后的数据

线是以 12 路差分并行总线的形式输出的,支持 LVDS 电平。芯片可提供两路模拟信

号转换,支持双边沿采样。将 ADC 芯片的信号线引至 FMC 接口,以方便与采集卡

连接。光纤子卡将光纤接口的信号线连接至 FMC 接口,实现与采集卡的连接。

2.2.3

软件总体设计

采集卡系统软件设计包含两个部分,分别为底层逻辑设计、嵌入式软件设计和上

位机软件设计。底层逻辑设计主要完成各个模块的设计以及各模块之间的数据交互;

嵌入式设计是在虚拟机上完成 Zynq7000SoC 的内核移植;上位机软件完成 PCIE 设备

的检测和初始化,数据的接收,并以文件形式存储至硬盘,用来进行下一步处理。具

体设计如下。

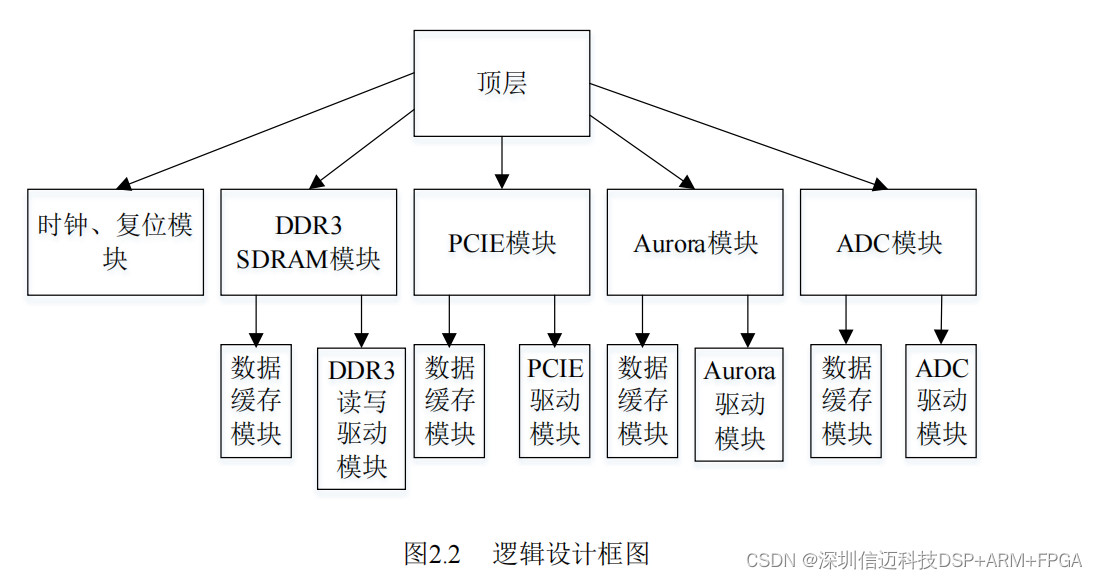

( 1 )逻辑软件总体设计

本次逻辑设计开发是基于 Vivado2017.4 平台, Vivado 软件是 Xilinx 公司开发推

出的专为 7 系列提供的开发套件。软件内部含有 SDK 开发软件,可以实现 Zynq7000

系列 SoC 的嵌入式开发。

逻辑设计采用自顶而下的方法,本次设计需要用到的协议有 Aurora 协议、 DDR3

SDRAM 接口协议和 PCIE 协议,每种协议对应相应的模块。 Aurora 协议是光纤的传

输协议,用来实现光纤数据的接收和转发; DDR3 SDRAM 接口协议主要是对 DDR3

SDRAM 的初始化和读写操作,用来实现对高速数据的缓存; PCIE 模块完成采集卡

与辐射源信号识别平台之间的数据交互。 Vivado 软件提供丰富的 IP 核,可以为高速

数据接口协议和 DDR3 SDRAM 提供解决方案。

由于各个协议不同,需要分模块设计,各个协议单独为一个模块。数据在各个模

块之间传送,各个高速协议之间很难工作在同步状态,如果数据采取直连的方式,可

能导致丢失数据发生。解决方法是采用异步 FIFO 接口,异步 FIFO 接口的读写时钟

是独立的,并且读写位宽可以成倍数关系,使设计更为灵活。整个逻辑设计包含 5 个

模块,时钟、复位模块用来给各模块提供时钟和复位信号; DDR3 SDRAM 模块实现

了高速数据的缓存功能; PCIE 模块包含 PCIE 的驱动模块,实现了采集卡与 PC 机的

数据交互; Aurora 模块是光纤驱动模块,实现光纤数据的接收和转发; ADC 模块实

现了 ADC 芯片的配置和驱动,实现了雷达信号的模数转换并转发。除了时钟复位模

块,其他模块由各自的驱动模块和数据缓存模块组成,其中数据缓存模块为 FIFO 接口,方便各模块之间的连接。逻辑设计框图如图 2.2 所示。

为了满足雷达辐射源识别项目需求,高速数据传输速率应不小于 19.2Gbps 。 FMC

接口支持的数据最大传输速率为 10Gbps ,为了实现高速率数据传输,光纤采用 4 通

道传输,单通道速率为 10Gbps ,总传输速率为 40Gbps ,为了与光纤速率保持同步,

PCIE 采用 2.0 协议,单通道 5.0Gbps , x8 模式,总速率为 40Gbps ,与光纤速率相同。

传输速率能基本满足大多高速数据传输。

( 2 )嵌入式软件总体设计

嵌入式软件设计主要在 PS 端开发,是为将来的用户应用程序做准备。在完成 PL

部分的设计基础上,使用 Vivado 软件自带的 SDK 开发平台,在 Linux 系统的环境下

进行嵌入式的开发设计。本设计在 Ubuntu 下完成嵌入式软件设计,通过运行一系列

脚本文件进行系统编译、内核编译、生成镜像和烧写镜像等操作。

( 3 )上位机软件总体设计

上位机的功能应具有采集卡的识别、检测和初始化,此外还能接收来自 PCIE 接

口的数据,并可以把数据保存成文件。

在 PC 机上开发 PCIE 驱动需要使用驱动开发工具,本次设计的 PCIE 驱动开发

使用 WinDriver 开发工具。 WinDriver 软件是由 Jungo 公司开发的驱动开发平台,能

支持多种操作系统,软件提供了 windrvr.sys 内核,可用来与操作系统实现核心交互,

使开发者不用直接操作系统内核,只用通过函数库来实现与系统内核的通信,这样既

简化了驱动程序开发流程也提高了驱动开发效率。

上位机在 Visual Studio(VS) 开发平台上进行开发, VS 是微软公司推出的开发工

具,支持多种编程语言。上位机的设计是通过 WinDriver 提供的内核和函数库的调用,

实现 PCIE 设备的初始化和数据交互。由于不同的 PC 机 CPU 处理能力不同,对中断

相应和数据处理的能力也有差别,一般采用 DMA 方式来传递数据。 DMA 长度在合

适的范围内 CPU 可以发挥最佳性能。 DMA 长度的设定既可以由逻辑设计设定也可以

由上位机设定,结合实际,由上位机设定 DMA 长度更方便,

结合以上分析,上位机需要有以下功能:

1) PCIE 设备的打开、关闭和初始化功能;

2) DMA 长度设定功能;

3) 保存数据并形成文件的功能。

这篇关于基于ZYNQ的PCIE高速数据采集卡的设计(二)总体设计与上位机的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!