本文主要是介绍保护模式 x86 TLB,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

TLB

文章目录

- TLB

- TLB结构

- TLB种类

- 实验

思考:

通过一个线性地址0x12345678访问一个物理页,我们想要读取0x12345678地指处一个字节的数据时,

操作系统是真的只读了一个字节吗?

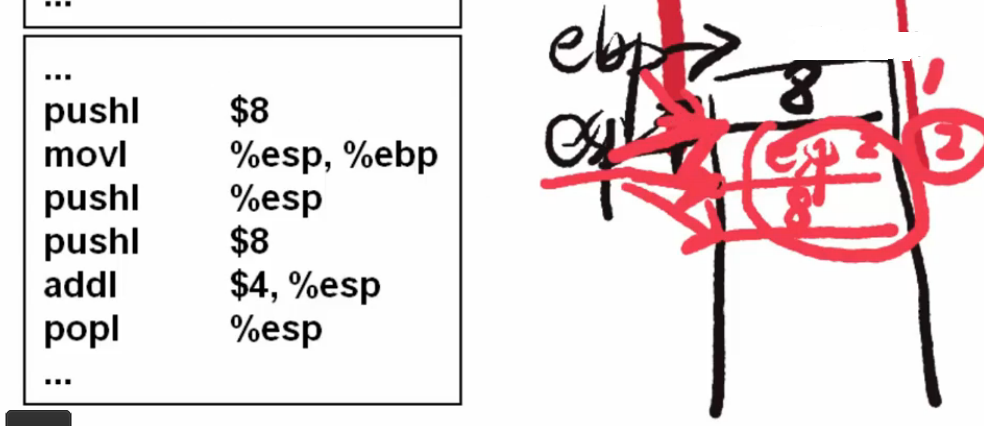

答:线性地址首先会被拆分,然后读取PDE(4字节),再读取PTE(4字节),最后读取物理页上的1字节,总共读取了8+1字节.

补充提问:

会不会有这种情况,DWORD 大小数据,前两个字节在一个物理页,后两个字节在另一个物理页,

这样当我要读取这DWORD字节大小的数据时,总共读取了多少字节?

答:这种情况肯定存在,并且也存在1个字节在单独物理页,其他三个在一个这种情况,但是不存在连续三个字节存储在分离的物理页的情况.上面说的那种情况,读取4字节PDE,4字节PTE,2字节数据,重复一遍,总共20个字节,如果是2-9-9-12分页模式, 就会多读8+8+8 = 24字节

这样的效率是非常低的! 为此CPU在内部做了一个表,来记录这些东西

这个表格是CPU内部的,和寄存器一样快

这个表格:TLB(Translation Lookaside Buffer)

思考:

任何一个进程都有4G大小的独立空间,那其中的线性地址最大能有4G个,但是TLB是存储在CPU内部的,大小受限,最多存储几百条记录,

那这几百条相对与4G少之又少,请思考这几百条的意义?

TLB结构

| LA(线性地址) | PA(物理地址) | ATTR(属性) | LRU(统计) |

|---|---|---|---|

| 0x80000000-以上 | G位=1 | ||

| 0x80000000-以下 | G位=0 |

LA <-> PA ,线性地址和相对应的物理地址对应并存储ATTR属性信息:如果是2 9 9 12 分页模式就是PDPE PDE PTE三个属性&运算起来的,如果是10 10 12分页模式就是PDE & PTELRU统计:统计该线性地址的使用频率,CPU保证TLB存储使用频率最高的线性地址.由于同一个线性地址在不同进程对应的物理地址不一定是相同的(绝大部分情况都不同),所以只要CR3变了 TLB立马刷新,一核一套TLB 如果CR3改了,TLB刷新,但是重建高2G以上的很浪费,所以PDE和PTE有个G标志位,如果G位为1刷新TLB时将不会刷新PDE/PTE的G位为1的页,当TLB满了,根据统计信息将不常用的地址废弃,最近最常用的保留.注意:PDE中的G位只有当PDE的P/S位 =1 时,即PDE代表大页的时候才有效

TLB种类

TLB在X86体系的CPU里的实际应用最早从Intel的486CPU开始,在X86体系的CPU里边,一般都设有如下4组TLB:

第一组:缓存一般页表(4K字节页面)的指令页表缓存(Instruction-TLB);

第二组:缓存一般页表(4K字节页面)的数据页表缓存(Data-TLB);

第三组:缓存大尺寸页表(2M/4M)的指令页表缓存(Instruction-TLB);

第四组:缓存大尺寸页表(2M/4M)的数据页表缓存(Data-TLB);

实验

步骤一:体验TLB的存在

步骤二:全局页的意义

步骤三:INVLPG指令的意义

待补充 - - -

这篇关于保护模式 x86 TLB的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!