本文主要是介绍FPGA综合系统设计(一):1.2/50μs冲击电压测量与显示,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

概述

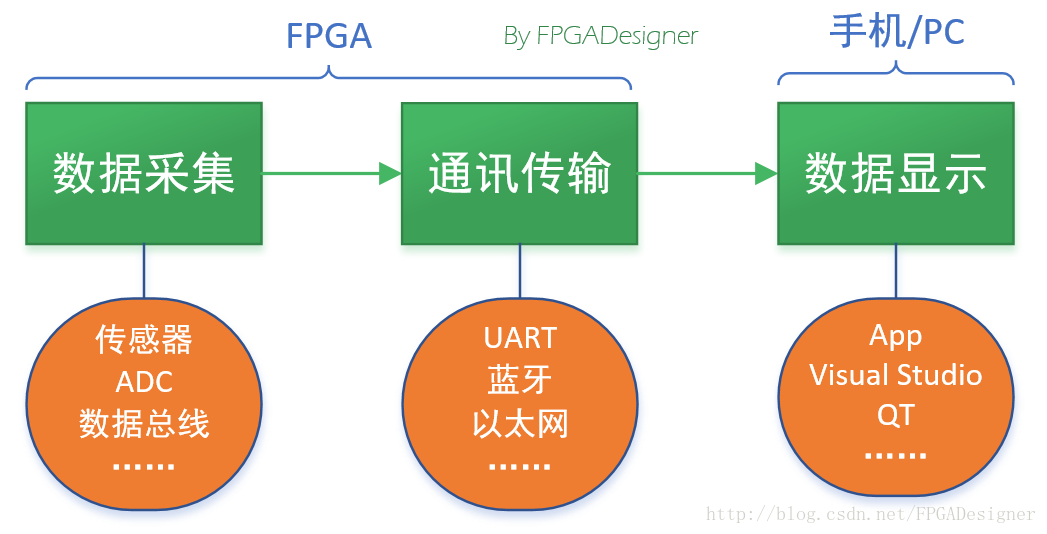

今天要谈的一个问题是“FPGA的数据采集、传输和显示系统”该如何实现。这个系统很常用,虽然比较简单,但在一定程度上还是很考验FPGA的综合设计能力,初学者可以多练习一些这种系统的设计来提升一下自己的能力。系统结构如下图所示:

我将会以(1)基于FPGA的1.2/50μs冲击电压测量与显示;(2)基于FPGA的温度采集和以太网传输;这两个课题为基础详细介绍在系统设计中遇到的问题与相关的解决方法,并且这些方法在其它系统中也有一定的适用性。今天的博文介绍的是第一个课题。

环境与设备

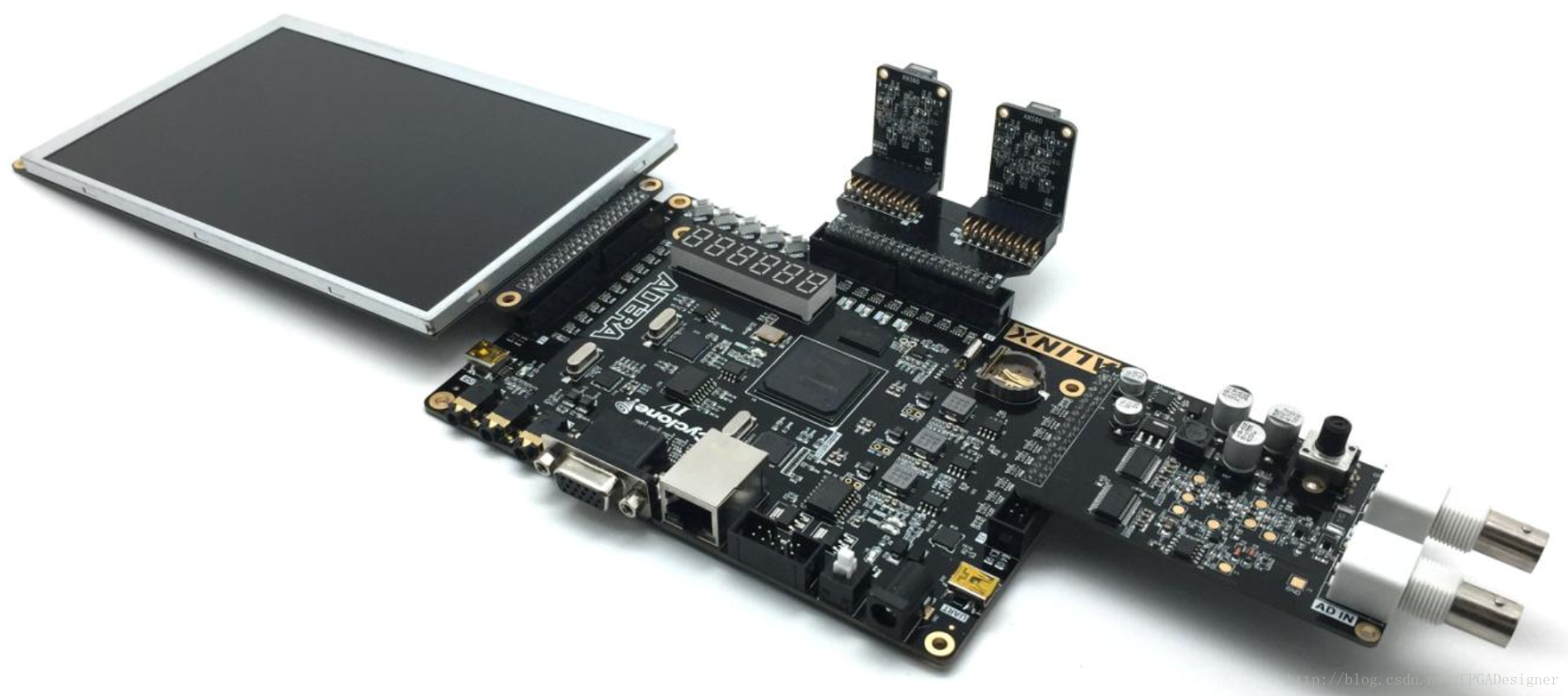

本文所使用的实验平台与开发环境如下所示:

- 黑金AX515开发板(Altera Cyclone IV代)与QuartusII软件;

- 高速并行AD9280芯片用于ADC采集和板载CP2102 USB转串口;

- 1.2/50μs高压冲击发生器,可产生最高达10kV的高压脉冲(或DDS);

- SD-M-M脉冲电阻分压器,电压比率200:1;

- MATLAB R2016a用于上位机的显示界面设计。

1.2/50μs冲击电压测量与显示

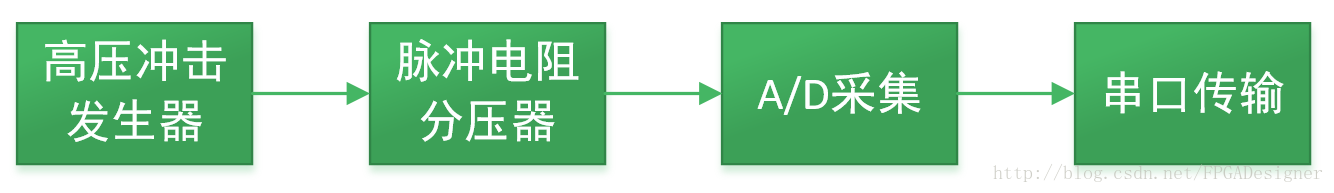

该系统的结构框图如下图所示:

首先进行系统级别的考量,系统的关键问题包括:

- 如何选择ADC芯片以保证采集和显示到的脉冲电压波形不失真;

- 如何将发生器输出的高压脉冲控制在一个FPGA可以采集到的范围。

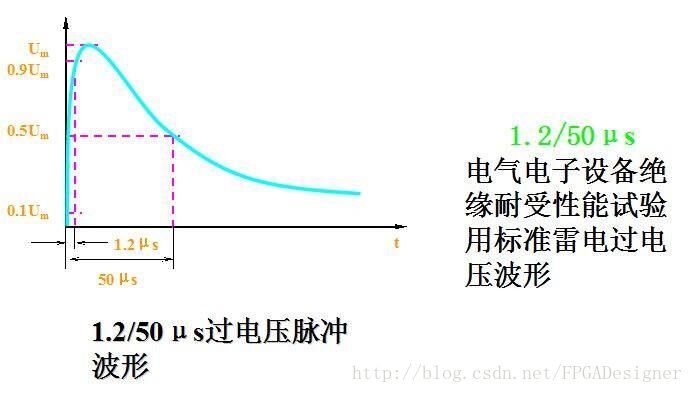

对于第一个问题,关键在于结合系统来确定A/D转换器的分辨率和采样速率。该系统中要采集的1.2/50μs冲击信号如下图所示:

其中的关键时间便是脉冲上升时间1.2μs,如果能保证无失真的采集到该段时间内的信号那么也可以确保整个脉冲时间内的信号采集都没问题。上升时间的信号频率可以认为是1/1.2μs≈833kHz,我们认为在这段时间内可以到采集10个点便能做到无失真,即ADC的采集速率至少为833kHz×10=8.33MHz。至于ADC的位数,本系统对电压精度的需求也不高,而且后续的串口传输帧格式是8位数据,如果选择8bit的ADC则可以使系统之间的数据位数匹配。综上所述选择8bit最高采样速率32MHz的AD9280。

对于第二个问题,系统难以调控的因素是A/D转换器的采集范围,较好调控的因素是高压冲击发生器的输出。如果将ADC的硬件电路设计控制在0~5V,则200:1的脉冲电阻分压器的前级电压最高只能是5*200=1kV,如果高压冲击发生器的输出超过了1kV,则会出现削顶的现象。

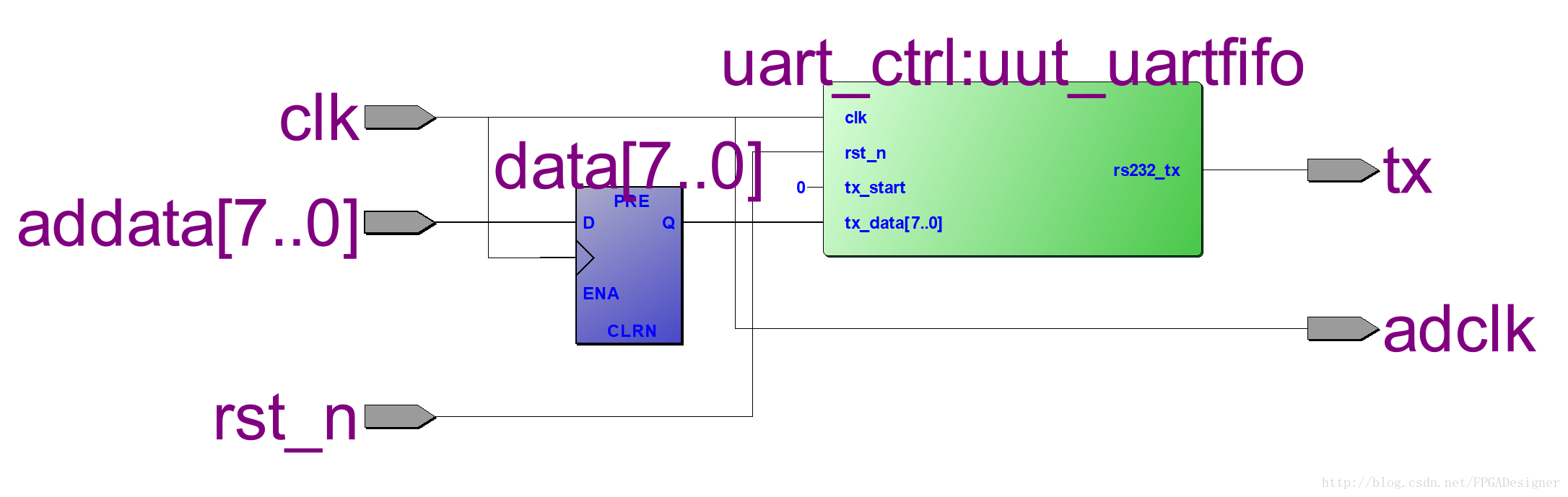

接下来进行FPGA的程序设计,如果按照上面的系统框图进行设计,设计结果如下所示:

设计中用一级寄存器存储ADC采集的结果,通过tx_data信号连接到串口模块,通过串口将数据发送出去。上位机使用MATLAB来设计,主要使用的是MATLAB串口操作时的事件驱动和函数回调机制,每当从串口接收到一个字节的数据(及一个电压值)便刷新图形,从而实现动态监测串口的效果。

然而设计后实际测试便会发现系统无法工作,上位机上没有任何波形。即使换一个低频信号源进行测试上位机中看到的也是完全变形的波形。其实仔细分析一下便会发现问题所在:前端的ADC采集模块的时钟信号高达几十M,而后端的串口发送数据的速率此处选择为9600bps,也就是说两者虽然在形式之上是直接相连,而它们的时钟域确完全不匹配,ADC模块采集到的大量数据其中只有少数被串口传输出去,可以理解为串口时钟对ADC数据重新做了一次数据采样,发生了严重的“数据泄露”。

解决上述问题的方法便是在ADC模块和串口模块之间增加一个存储器,可以是FIFO或双口RAM等,ADC模块从一个方向向存储器中写入数据,串口模块从另一个方向读出数据,改进后的系统框图如下所示:

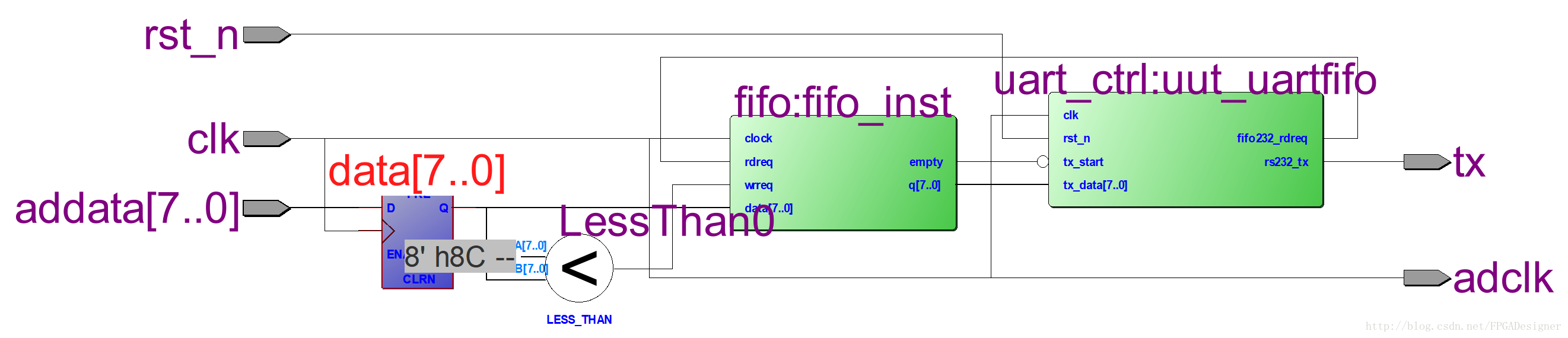

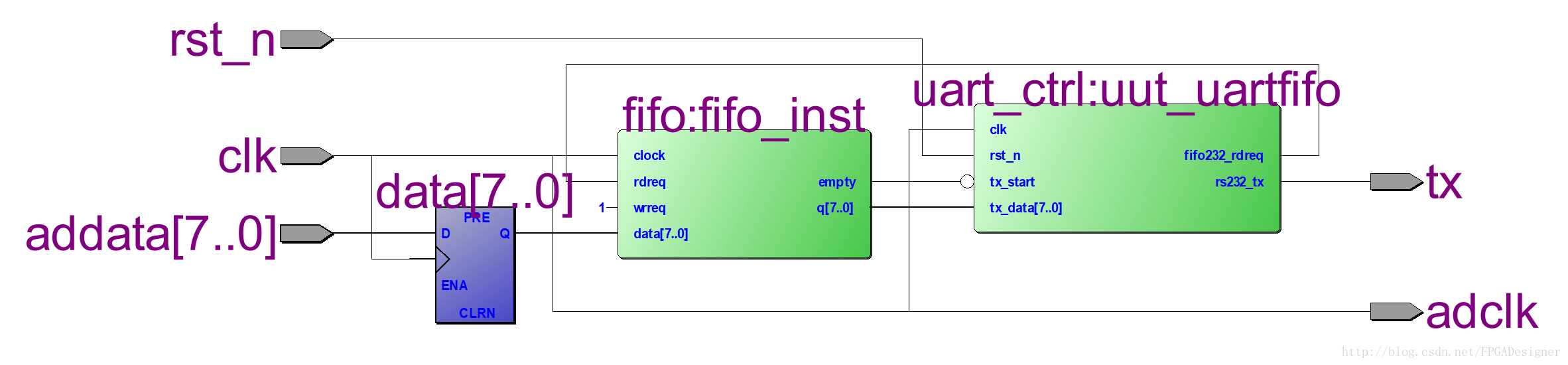

按照上述框图对FPGA设计进行改进,如下图所示:

两个不同时钟模块之间用一个FIFO隔离,再对FIFO为空、为满时做一些特殊处理,便可以保证串口传输的数据不会发生遗漏。实质上这种处理方法也是FPGA**处理多时钟域**常用的方法,比较庞大复杂的系统中经常能看到很多FIFO的使用。

然而即使解决了时钟域的问题,再次测试时还是没有效果,上位机的波形显示的始终在0V附近。导致这个问题的原因也显而易见,高速ADC采集到的数据量是非常庞大的,按10MHz采样1s就会产生10000000个数据,而串口想把这个多的数据发送完是需要比较长时间的。在脉冲来临之前,ADC已经采集了很多0V电压值,导致即使在脉冲信号来临的时候,串口还需要相当长的时间把之前存储的数据发送完(甚至可能会因为FIFO对空、满的特殊处理而把脉冲信号的数据过滤掉),这也就导致上位机中迟迟不能观察到脉冲信号波形的原因。

问题的解决方法便是对FIFO的写使能信号做处理。FPGA中的FIFO都可以配置一个wreq写请求信号,当该信号为1时允许向FIFO中写入数据,当该信号为0时禁止向FIFO写入数据。我们只要在设计中增加一个比较器即可,比较器的一端为当前采集的电压值,另一端为预设的比较电压信号值。改进后的设计如下图所示:

如果将比较值设置为比0V高一点,如0.1V或0.2V附近等,这样在无信号时期,电压值为0V时,关断FIFO的写入,FIFO中便不会存储0值数据,串口从FIFO中读出并发送的便是有用的脉冲信号。

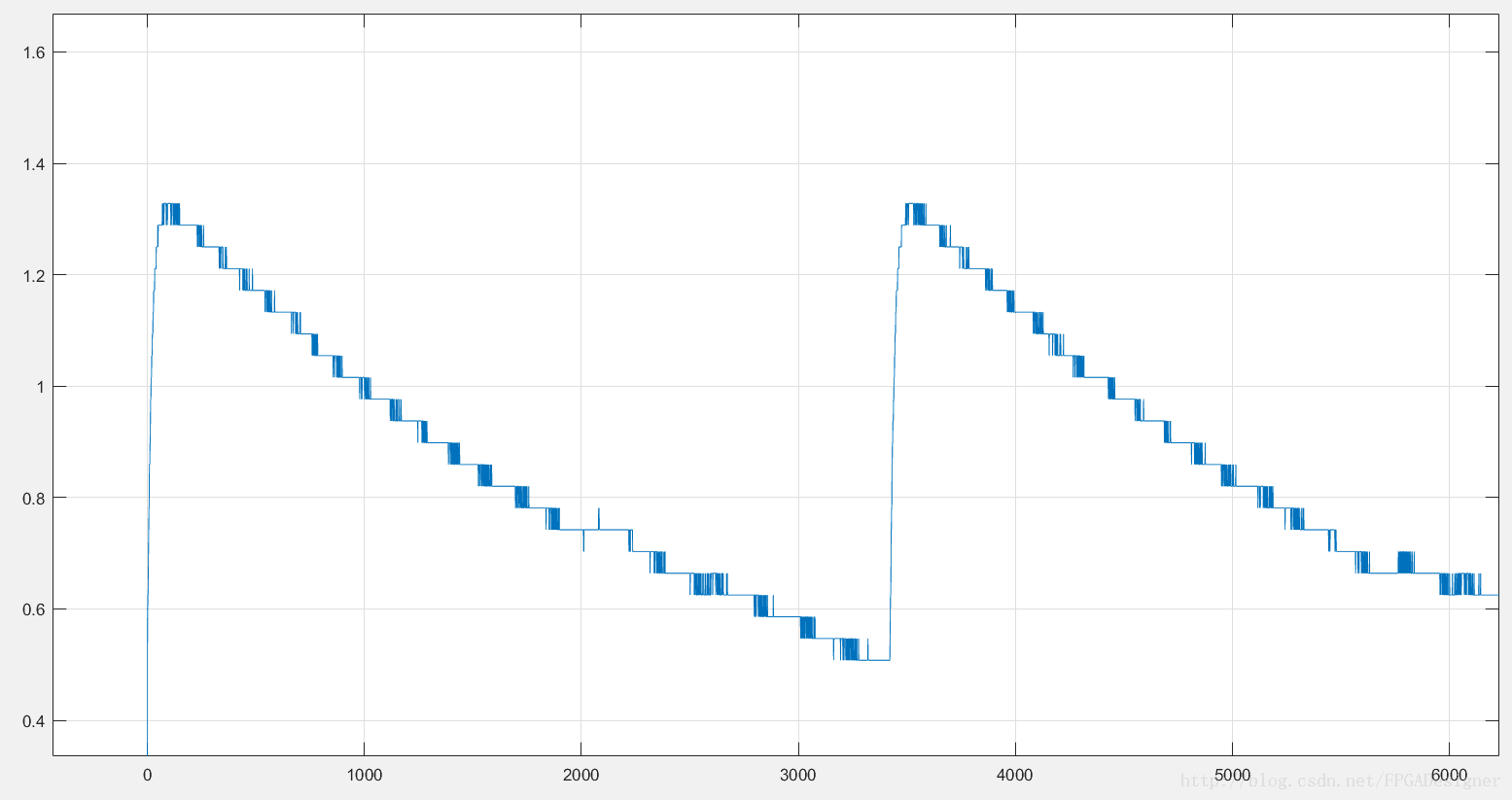

至此我们已经解决了一个基础的数据采集-传输-显示系统的FPGA设计,我带领大家逐步发现设计中的一些问题和解决这些问题的方法,这些方法完全可以应用在其它系统中。我们看一下这个系统的运行结果。下图是采集到的连续两个脉冲信号:

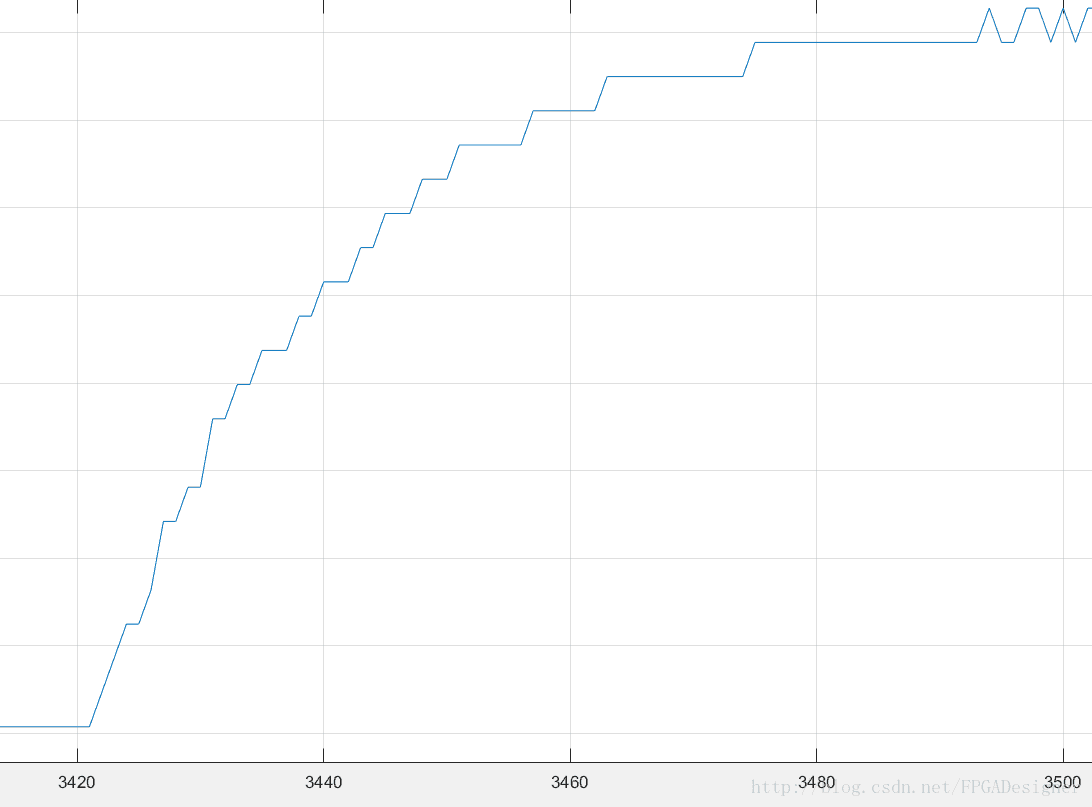

两个脉冲之间当然不可能是无间隔的,之所以没有显示出来便是因为加了比较器的原因。而脉冲的下降沿期间数据的跳变太严重这是由于ADC模块的硬件设计导致量化精度不够造成的。放大观察信号的1.2μs上升期间:

本系统采用的是50MHz采样,每个点代表的时间便是1/50MHz=20ns,粗略计算一下上图中从0.1U到0.9U之间的上升时间差不多也是1.2μs。表明本系统完成了预设的功能。

总结

如果您对本系统中采用的思想方法还是不熟悉,或者对将这些方法应用到其它系统中还不够熟练,没有关系,博主将在后面紧跟着更新“基于FPGA的温度采集和以太网传输”这个课题的设计,这个课题看起来与本课题差异很大,实质上系统设计思路可以说是完全一致。

完整的Quartus工程可以在这里下载:https://download.csdn.net/download/fpgadesigner/10475422

这篇关于FPGA综合系统设计(一):1.2/50μs冲击电压测量与显示的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!